КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Process

|

|

|

|

Begin

Begin

Begin

Else

Begin

Begin

Begin

End process

Begin

Асинхронная предустановка триггеров с динамическим управлением

Begin

Begin

Begin

Process

Begin

Process

Различие построения синхронных схем на базе if и wait конструкций

В ПРОЦЕССЕ RTL-СИНТЕЗА

ОСОБЕННОСТИ СИНХРОНИЗАЦИИ ЦУ

В if стиле может быть смоделировано более одного синхросигнала в одном процессе и что более верно - в одном процессе можно смешивать описание любой последовательной формы.

Использование wait-стиля логически ассоциировано с каждым синхросигналом, и синхронная форма должна быть отдалена от комбинационной и с ней ассоциируется свой собственный process stmt.

Используя wait style проектирования может быть описан с использованием более чем одного процесса, как это показано в следующем шаблоне:

wait until clock_expression_1;

synchronous_logic_description_1

end process;

wait until clock_expression_2;,

synchronous_logic_description_2

end process;

process (sensitivity_list)

combinational_logic_description

end process;

Используя стиль условного оператора, те же самые три процесса могут быть объединены в один единственный процесс, показанный в следующем шаблоне.

process (sensitivity-list-with-clocks)

if clock-expression-1 then

synchronous-logic-description-1

end if;

if clock-expression-2 then

synchronous-logic-description-2

end if;

combinational-logic-description

end process;

Для использования асинхронной предустановки используется специальная форма

if-stmt::=

if condition_1 then

async_logic_1

elsif condition_2 then

async_logic_2

elsif condition_3 then

async_logic_3

…

elsif clock_expr then

sync_logic

end if;

При важно, что оператор if может иметь одну и больше (максимально - восемь) ветвей elsif, но ветвь else здесь не допустима.

Если сигналу назначается значение в любой из асинхронных секций, а также назначается в синхронной части, то в результате синтеза будет получен триггер с асинхронной предустановкой.

|

|

|

| Моделирование триггеров | С асинхронной предустановкой С асинхронным сбросом С асинхронной предустановкой и сбросом |

process (sensitivity_list)

Combination_logic_description

If_style template:

process (sensitivity_list_with_clocks)

if clock_expr_1 then

synchronous_logic_description_1

end iиf;

if clock_expr_2 then

synchronous_logic_description_2

end if;

combinational_logi_-description

end process;

В зависимости от присваиваемого значения, триггер может быть либо триггером с асинхронной установкой (если назначается ненулевое значение), либо триггером с асинхронным сбросом (если назначается нулевое значение), либо же триггер с обоими входами.

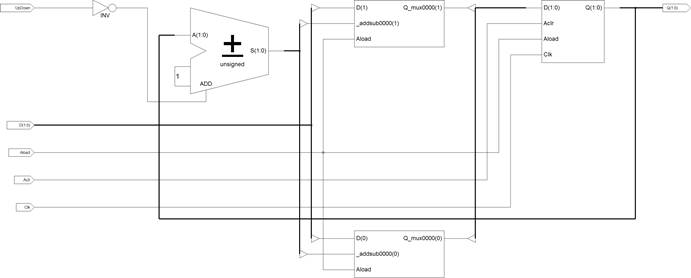

Имеется пример счетчика с верхним и нижним порогами с асинхронным сбросом и установкой. Синтезированная RTL схема приведена на рисунке 1.

library IEEE,

use IEEE.STD_LOGIC_1163.all;

use IEEE.NUMERIC_STD.all;

entity ASYNC_COUNT2 is

port (CLK, PRESET, UPDOWN, CLEAR: in STD_LOGIC;

DIN: in STD_LOGIC_VECTOR (1 downto 0);

DOUT: out STD_LOGIC_VECTOR (1 downto 0));

end;

architecture EXAMPLE of ASYNC_COUNT2 is

signal COUNTER: UNSIGNED (1 downto 0);

process (CLK, PRESET, UPDOWN, DJN, CLEAR, COUNTER)

if PRESET = '1' then

COUNTER <= UNSIGNED (DIN);

elsif CLEAR = '1' then

COUNTER <= (others => '0');

elsif CLK = '1' and CLK'EVENT then

if LJPDOWN ='1' then

COUNTER <= COUNTER + 1;

COUNTER <= COUNTER - 1;

end if;

end if;

DOUT <= STD_LOGIC_VECTOR(COUNTER);

end process;

end;

Рисунок 1 – RTL схема с асинхронным сбросом и установкой

Предостережение. Возможно записать следующий код, чтобы ввести триггер D-типа для ODL.

library IEEE;

use IEEE.STD_LOGIC_1163.all;

use IEEE.NUMERIC_STD.all;

entity MUX_FF is

port (CLK, SET, BRV: in STD_LOGIC;

DIN: in STD_LOGIC_VECTOR (1 downto 0);

ODL: out STD_LOGIC;

DOUT: out STD_LOGIC_VECTOR (1 downto 0));

end;

architecture EXAMPLE of MUX_FF is

signal COUNT: UNSIGNED (1 downto 0);

process (CLK, SET, DJN, COUNT, BRV)

if SET = '1' then

COUNT <= UNSJGNED(DIN);

elsif CLK = '1' and CLK'EVENT then

ODL <= BRV;

COUNT<=COUNT + 1;

end if;

end process;

DOUT <= STD_LOGIC_VECTOR(COUNT);

end;

В этом случае, ODL не синтезируется как простой D-триггер, но синтезируется как асинхронный D-триггер со сбросом и установкой. Это потому что присвоение ODL зависит еще и от значения SET. Какое значение ODL должно быть когда SET равен '1'? Ответ - значение ODL должно быть сохранено; это подразумевает, что имеется неявное присвоение " ODL < = ODL; " в переходе SET = '1'. Заметим, что пока выполняемый переход равен SET, все фронты синхроимпульса игнорируются; это потому что первое условие IF- всегда истинно и состояние фронта синхроимпульса никогда не проверяется.

|

|

|

Если ODL не должен зависеть от сигнала SET, существует хорошая альтернатива разделить процесс на два процесса как показано ниже.

-- Этот процесс — для триггера с асинхронными сбросом/ установкой:

process (CLK, SET, DIN, COUNT)

if SET = '1' then

COUNT <= UNSJGNED(DIN);

elsif CLK = '1' and CLK'EVENT then

COUNT<=COUNT+1;

end if;

end process;

-- Этот процесс — для простых D-триггеров:

|

|

|

|

|

Дата добавления: 2014-01-11; Просмотров: 354; Нарушение авторских прав?; Мы поможем в написании вашей работы!