КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Лекция 4

|

|

|

|

ПРИМЕНЕНИЕ ЛОГИЧЕСКИХ СХЕМ В УСТРОЙСТВАХ АВТОМАТИКИ: схемы И, ИЛИ, НЕ. КЛАССИФИКАЦИЯ ТРИГГЕРОВ. ШИФРАТОРЫ, ДЕШИФРАТОРЫ, МУЛЬТИПЛЕКСОРЫ

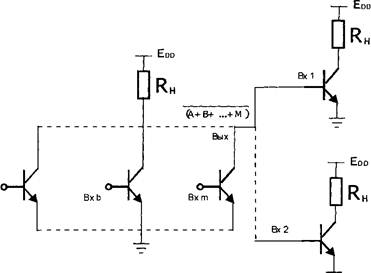

Рис 1 Логическая схема ИЛИ-НЕ с непосредственными связями на биполярных транзисторах.

Схема ИЛИ-НЕ, показанная на рис. 2, работает следующим образом. При наличии хотя бы на одном из входов напряжения U соответствующий переключательный транзистор входит в режим насыщения и напряжение на выходе схемы уменьшается до Uo Если на всех входах устанавливается напряжение, то ток источника питания через нагрузочный резистор поступает на базы нагрузочных транзисторов, открывая их. Неравномерное распределение тока между базами транзисторов, подключенных к одному выходу инвертора, и создает главную трудность реализации данного класса схем. Входные характеристики транзисторов имеют разброс, обусловленный разбросом технологических параметров, различиями в режимах работы и неодинаковость температур транзисторов.

Применение логических схем в устройствах автоматики

Логическая функция цифровой схемы может быть записана в виде таблицы истинности. Отдельные шаги при составлении таблицы истинности ведут к итоговому уравнению для выхода всей схемы, в котором присутствуют только состояния входов или их инвертированные состояния Такое уравнение выражает функцию всей схемы. Поэтому оно называется логической функцией цифровой схемы.

Логическая схема представляет собой функциональный узел, который выдает выходную величину, зависящую только от значений входных переменных в данный момент времени.

Электронную схему, в которой сигнал 1 на выходе появляется только тогда, когда на входе А и входе В совпадают сигналы 1, называется логическим элементом И (И-вентиль). Операция конюнкция.

|

|

|

Простейший И-вентиль на последовательно включенных контакторах может быть реализован по схеме на рис.. Но в настоящее время почти всегда применяются интегрированные полупроводниковые микросхемы.

Любая схема, удовлетворяющая таблице истинности логического умножения, является логическим элементом И. Для обозначения операции И в алгебре логики используется символ.

X = А ∩ В

В литературе встречаются другие символы для обозначения логического умножения, точка (•) или &:

На выходе логического элемента И сигнал 1 появится только тогда, когда на всех входах совпадут сигналы 1. Например плазматрон включится при наличии порошка в питателе и воды системе охлаждения.

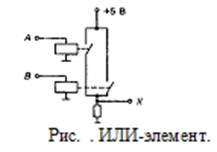

Логический элемент ИЛИ и операция логического сложения (дизъюнкции)

Двигатель остановит перемещение заготовки либо от пульта оператора либо по программе либо при наличии аварийной ситуации например открытие дверки в вакуумной камере. Эта ситуация (алгоритм) содержит в себе операцию логического сложения ИЛИ. Сказанное иллюстрирует таблица истинности на рис. (состояние 1 значит «истина», состояние 0 значит

«ложно»).

Электронная схема, на выходе X которой появляется сигнал 1, если на входе А или входе В или на обоих входах присутствует сигнал 1, называется логическим элементом ИЛИ. Элемент ИЛИ может быть реализован по схеме на рис. с помощью двух обмоток реле.

Для обозначения операции ИЛИ в алгебре логики используется символ v.

X = A v В

Электронную схему, состояние на выходе X которой всегда противоположно состоянию на входе А, называют логическим элементом НЕ или инвертором.

На рис. приведена схема логического элемента НЕ. Как и ранее рассмотренные логические элементы, вентили НЕ почти всегда используются в виде интегрированных полупроводниковых микросхем. Для обозначения операции НЕ в алгебре логики используется черта над символом или апостроф: Х = А

|

|

|

Условное обозначение логического элемента НЕ показано на рис. Состояние выхода логического элемента НЕ всегда противоположно состоянию входа.

Рис..4 Условные обозначения НЕ-элементов (USA).

Логические элементы И, ИЛИ и НЕ предназначены для выполнения трех основных операций цифровой логики над дискретными сигналами. С помощью этих элементов можно реализовать логические операции любой сложности. Поэтому эти элементы называются основными. К основным логическим элементам относится также буфер. Если на входе буфера 1, то и на выходе 1, иначе 0.

И ИЛИ НЕ

Логические элементы ИЛИ-НЕ используются так же часто, как и элементы И-НЕ. Для них так же создано собственное условное обозначение. Оно получается из символа вентиля ИЛИ с кружком на выходе. Этот кружок означает инвертирование выхода.

Для логического элемента ИЛИ-НЕ действительно следующее утверждение:

На выходе логического элемента ИЛИ-НЕ логическая 1 будет только в том случае, если ни на одном из входов нет состояния 1.

Рассмотрим более сложные схемы реализованные на основе описанных простейших логических схем.

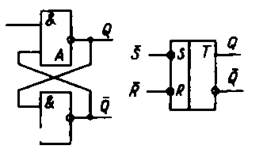

Классификация триггеров

Триггер предназначен для хранения значения одной логической переменной (или значения одноразрядного двоичного числа; при хранении многоразрядных двоичных чисел для запоминания значения каждого разряда числа используется отдельный триггер). В соответствии с этим триггер имеет два состояния: одно из них обозначается как состояние 0, другое — как состояние 1. Воздействуя на входы триггера, его устанавливают в нужное состояние.

Основные обозначения. Триггер имеет два выхода: прямой Q и инверсный Q. Состояние, в котором находится триггер, определяется уровнями напряжения на этих выходах: если напряжение на выходе Q соответствует уровню лог.О то принимается, что триггер находится в состоянии 0, при Q = 1 триггер, находится в состоянии 1. Логический уровень на инверсном выходе Q представляет собой инверсию состояния триггера (в состоянии 0 Q = 1, и наоборот).

Триггеры имеют различные типы входов. Приведем их обозначения и назначения:

|

|

|

R (от англ. Reset) —раздельный вход установки в состояние 0;

S (от англ. Set) — раздельный вход установки в состояние 1;

К — вход установки универсального триггера в состояние 0;

J — вход установки универсального триггера в состояние 1\

Т— счетный вход;

D (от англ. Delay) — информационный вход установки триггера в состояние, соответствующее логическому уровню на этом входе;

С — управляющий (синхронизирующий) вход.

Наименование триггера определяется типами его входов. Например, RS-триггер — триггер, имеющий входы типов R и S.

По характеру реакции на входные сигналы триггеры делятся на два типа: асинхронные и синхронные. В асинхронном триггере входные сигналы воздействуют на состояние триггера непосредственно с момента их подачи на входы, в синхронных триггерах — только при подаче синхронизирующего сигнала на управляющий вход С.

Переключение триггера из одного устойчивого состояния в другое происходит при подаче активных сигналов на входы.

Одновременная подача активных уровней лог. 1 на оба входа R и S не допускается, так как при этом на обоих выходах установится уровень лог.О, а после снятия со входов активных логических уровней состояние триггера окажется неопределенным: в силу случайных причин триггер может установиться либо в состояние 0, либо в состояние 1. На рис приведена таблица состояний RS-триггера в форме таблицы Вейча.

Можно сделать очень большое количество разнообразных триггеров. Хотя они будут обладать одним общим свойством: все они имеют два стабильных состояния. Условия, при которых триггеры переходят из одного стабильного состояния в другое и обратно, очень разнообразны. К настоящему времени появилось так много разновидностей триггеров, что возникла необходимость в их классификации.

Прежде всего, триггеры можно разбить на две большие группы. Первая группа охватывает все триггеры, не управляемые тактовыми импульсами синхронизации. Все тактируемые импульсами триггеры принадлежат ко второй группе.

Рис. 4. Обзор типов триггеров.

|

|

|

Однако установка тригеров происходит только в момент подачи сигнала синхронизации. Можно соединить большое число триггеров и приблизительно одновременно включить их совместным тактовым сигналом синхронизации. Этот способ управления называют тактовым управлением. Входы тактовых синхроимпульсов являются статическими входами.

Тактируемые по фронту триггеры, можно переключать одновременно с большой точностью. Тактируемые по фронту триггеры могут строиться по одноступенчатой и двухступенчатой схемам. Недостатком одноступенчатых триггеров является возможность «проскакивания» сигналов, например логических единиц.

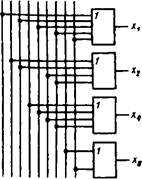

Шифратор (называемый также кодером) осуществляет преобразование десятичных чисел в двоичную систему счисления. Пусть в шифраторе имеется т входов, последовательно пронумерованных десятичными числами (0, l,2,...,m- 1), и n выходов. Подача сигнала на один из входов приводит к появлению на выходах n-разрядного двоичного числа, соответствующего номеру возбужденного входа.

Очевидно, трудно строить шифраторы с очень большим числом входов, поэтому они используются для преобразования в двоичную систему счисления относительно небольших десятичных чисел. Шифраторы широко используются в разнообразных устройствах ввода информации в цифровые системы. Такие устройства могут снабжаться клавиатурой, каждая клавиша которой связана с определенным входом шифратора. При нажатии выбранной клавиши подается сигнал на соответствующий вход шифратора, и на его выходе возникает двоичное число, соответствующее выгравированному на клавише символу.

На рис. приведено символическое изображение шифратора, преобразующего десятичные числа 0, 1, 2,...,9 в двоичное представление в коде 8421. Символ CD образован из букв, входящих в английское слово Coder. Слева показаны 10 входов, обозначенных десятичными цифрами 0, 1, 2,...,9, справа — выходы шифратора; цифрами 1, 2,4,8 обозначены весовые коэффициенты двоичных разрядов, соответствующих отдельным выходам.

| Номер входа | Выходной код 8421 | |||

| *8 | *4 | х2 | х\ | |

Изложенным способом могут быть построены шифраторы, выполняющие преобразование десятичных чисел в двоичное представление с использованием любого двоичного кода.

Для обратного преобразования двоичных чисел в небольшие по значению десятичные числа используются дешифраторы (называемые также декодерами). Входы дешифратора предназначаются для подачи двоичных чисел, выходы последовательно нумеруются деся

тичными числами. При подаче на входы двоичного числа появляется сигнал на определенном выходе, номер которого соответствует входному числу.

Дешифраторы имеют широкое применение. В частности, они используются в устройствах управления. В таких устройствах двоичное число, поступая на вход дешифратора, вызывает появление сигнала на определенном его выходе. С помощью этого сигнала производится управление каким либо устаройством электроавтоматики. На рис. приведено символическое изображение дешифратора. Символ DC образован из букв английского слова Decoder. Слева показаны входы, на которых отмечены весовые коэффициенты двоичного кода, справа — выходы, пронумерованные десятичными числами, соответствующие отдельным комбинациям входного двоичного кода. На каждом выходе образуется уровень лог.1 при строго определенной комбинации входного кода. Дешифратор может иметь парафазные входы для подачи наряду с входными переменными их инверсий. Можно использовать для включение различных устройств при сварке, пайке, термообработки.

По способу построения различают линейные и прямоугольные дешифраторы.

Устройство, которое осуществляет выборку одного из нескольких входов и подключает его к своему выходу, называется мультиплексором. Мультиплексор имеет несколько информационных входов адресные входы (А0, Ах,...), вход для подачи стробирующего сигнала С и один выход Q. На рис, показано символическое изображение мультиплексора с четырьмя информационными входами.

Каждому информационному входу мультиплексора присваивается номер, называемый адресом. При подаче стробирующего сигнала на вход С мультиплексор выбирает один из входов, адрес которого задается двоичным кодом на адресных входах, и подключает его к выходу.

Таким образом, подавая на адресные входы адреса различных информационных входов, можно передавать цифровые сигналы с этих входов на выход Q.

При отсутствии (пробирующего сигнала.(С = 0) связь между информационными входами и выходом отсутствует (Q = 0). При подаче (пробирующего сигнала (С = 1) на выход передается логический уровень того из информационных входов Di9 номер которого i в двоичной форме задан на адресных входах. Так, при задании адреса Лх А0= 112 = 3|0 на выход Q будет передаваться сигнал информационного входа с адресом 310, т.е. Dy

По этой таблице можно записать следующее логическое выражение для выхода Q:

Построенная по этому выражению принципиальная схема мультиплексора приведена на рис..

В тех случаях, когда требуется передавать на выходы многоразрядные входные данные в параллельной форме, используется параллельное включение мультиплексоров по числу разрядов передаваемых данных.

Максимальное число информационных входов мультиплексоров, выполненных в виде интегральных схем, равно 16. Если требуется построить мультиплексорное устройство с большим числом входов, можно объединить мультиплексоры в схему так называемого мультиплексорного дерева. Такое мультиплексорное дерево, построенное на четырехвходовых мультиплексорах.

Демультиплексор имеет один информационный вход и несколько выходов и осуществляет коммутацию входа к одному из выходов, имеющему заданный адрес (номер). На рис. показана структура демультиплексора. Она включает в себя дешифратор, выходы которого управляют ключами. В зависимости от поданной на адресные входы кодовой комбинации, определяющей номер выходной цепи, дешифратор открывает соответствующий ключ, и вход демультиплексора подключается к определенному его выходу.

Объединяя мультиплексор с демультиплексором, можно построить устройство, в котором по заданным адресам один из входов подключается к одному из выходов Таким образом может быть выполнена любая комбинация соединений входов с выходами. Например, при комбинации значений адресных переменных х} = 1, х2 = 0, х3 = 0, х4 = О вход D2 окажется подключенным к выходу у0.

Если требуется большое число выходов, может быть построено демультиплексорное дерево.

Основная функция регистров — хранение одного многоразрядного числа. При зтом число должно быть представлено в двоичной системе счисления или в любой другой системе, но с двоичным представлением цифр разрядов (т.е. в любой двоично-кодированной системе счисления). Регистр строится в виде набора триггеров, каждый из которых предназначается для хранения цифр определенного числа. Таким образом, регистр для хранения n-разрядного двоичного числа должен содержать п триггеров.

Регистры могут использоваться для выполнения и некоторых других функций: сдвиг хранимого в регистре числа на определенное число разрядов влево или вправо, преобразование числа из последовательной формы (при которой оно передается последовательно разряд в параллельную (с передачей всех разрядов одновременно), Р образование из параллельной формы представления числа в последовательную и др.

В зависимости от формы представления числа (параллельной или последовательной), вводимого в регистр, различают два типа регистров: параллельные и последовательные. В параллельный регистр предназначенное для хранения число подается одновременно всеми разрядами, т.е. в параллельной форме. В последовательный регистр ввод числа производится путем последовательной во времени подачи цифр отдельных разрядов (обычно начиная с цифры младшего разряда), т.е. в последовательной форме.

Параллельный регистр. Пусть на вход регистра поступает параллельный код числа. При этом для каждого разряда числа предусматривается два входа, на один из которых поступает прямой код, на другой — инверсный. Прием такого числа может производиться в регистр, построенный с использованием простейших синхронных RS- триггеров, как показано на рис..

Если цифра 1-го разряда ai = 1, то на вход S соответствующего триггера поступает 1 и при подаче уровня лог.1 на вход С триггер устанавливается в состояние 1. Если ai - 0 (ai = 1), то 1 поступает на вход R и этот триггер устанавливается в состояние 0. Таким образом, триггеры устанавливаются в состояния, определяемые поступающими на их входы цифрами разрядов числа.

Когда на вход регистра поступает однофазный код числа (без подачи инверсных значений цифр разрядов), регистр может быть построен с использованием простейших синхронных D-триггеров. В таком регистре при уровне лог J на входе С триггеры устанавливаются в состояния, определяемые действующими на входах D цифрами разрядов. На рис. 3 приведены условные обозначения рассмотренных типов регистров.

Суть сдвига состоит в том, что цифра, имевшаяся до сдвига в i-м разряде регистра, передается в соседний справа разряд (т.е. значение четвертого разряда передается в третий разряд, значение третьего разряда — во второй разряд и т.д.). В крайний левый разряд заносится значение, подаваемое извне, а цифра крайнего правого разряда числа выдвигается из регистра во внешнюю цепь. Такого рода сдвиги вправо (либо влево) выполняются так называемым сдвиговым регистром.

Для построения сдвигового регистра чаще всего используются D- триггеры, управляемые одним фронтом синхронизирующего сигнала, но могут использоваться и другие типы триггеров, управляемых одним фронтом синхронизирующего сигнала, либо триггеры, построенные по принципу двухступенчатого запоминания информации.

Сдвиговые регистры имеют разнообразные применения. Рассмотрим некоторые из них.

Последовательный регистр. Представляет собой сдвиговый регистр, в который многоразрядное число вводится последовательно цифра за цифрой (обычно начиная с цифры младшего разряда) через один из его крайних разрядов (обычно через старший). Таким образом, представленный на рис. сдвиговый регистр может выполнять функции последовательного регистра, если на вход D триггера старшего разряда не постоянно подавать уровень лог.О (как показано на рисунке), а вводить в регистр число в последовательной форме.

Временное диаграммы на рис. иллюстрируют работу такого последовательного регистра при вводе числа 1011 последовательно разряд за разрядом, начиная с младшего разряда. В момент 1, появление синхронизирующего импульса на входе С вызывает сдвиг информации в регистре на один ряд вправо. Если до этого момента в регистре было число 00002, то в результате сдвига в первом, втором, третьем разрядах сохранится значение 0; в четвертый разряд будет со входа принято значение 1. Таким образом, в регистре образуется число 10002. В момент i2 появления следующего синхронизирующего импульса процессы сдвига и приема очередного разряда вводимого числа приводят регистр в состояние 11002. Далее в момент /3 в регистре образуется число 01102 и, наконец, в момент /4 — число 10112. Поданное на вход число оказывается зафиксированным в регистре.

Преобразование формы представления чисел из последовательной в параллельную. Данное преобразование может быть выполнено сдвиговым регистром, в котором предусматривается выдача числа в параллельной форме (одновременно с выходов триггеров всех разрядов).

В процессе преобразования формы представления числа n-разрядное двоичное число в последовательной форме подается на вход последовательного регистра. Через n тактов (после подачи п синхронизирующих импульсов) число окажется принятым в регистр и может быть затем снято в параллельной форме с выходов триггеров всех разрядов.

Преобразование формы представления чисел из параллельной в последовательную. Это преобразование может быть выполнено сдвиговым регистром, в котором предусмотрены входы для приема числа в параллельной форме.

После принятия в регистр n-разрядного числа на выходе триггера первого разряда образуется младший разряд числа. При сдвиге числа в регистре на один разряд вправо в триггер первого разряда передается цифра второго разряда введенного в регистр числа, и, таким образом, с выхода этого триггера снимается цифра следующего разряда. При повторении сдвигов вправо (n - 1) раз на выходе триггера первого разряда регистра появляются цифры всех п разрядов, и, таким образом, число может быть снято в последовательной форме.

Для выдвижения из регистра числа в последовательной форме, начиная с его старшего разряда, необходимо производить серию сдвигов влево, снимая цифры разрядов числа с выхода триггера старшего разряда регистра.

Счетчик — это цифровое устройство, определяющее, сколько раз на его входе появился некоторый определенный логический уровень. В дальнейшем во всех случаях, когда это не оговаривается специально, будем полагать, что счетчик подсчитывает содержащиеся во входном сигнале переходы с уровня лог. О к уровню лог. 1. При входном сигнале, имеющем форму последовательности импульсов, счетчик ведет счет поступающих на вход импульсов. Числа в счетчике представляются некоторыми комбинациями состояний триггеров. При поступлении на вход очередного уровня лог.1 в счетчике устанавливается новая комбинация состояний триггеров, соответствующая числу, на единицу большему предыдущего числа. Таким образом, счетчик представляет собой логическое устройство последовательностного типа, в котором новое состояние определяется предыдущим состоянием и значением логической переменной на входе.

Для представления чисел в счетчике могут использоваться двоичная или десятичная система счисления. При использовании двоичной систе-

мы состояния триггеров и соответствующие им логические уровни на прямых выходах триггеров определяют цифры двоичных разрядов числа. Если для регистрации двоичного числа в счетчике используется п триггеров, то максимальное значение числа, до которого может вес» тись счет, N = 2я - 1. Так, при п = 4 N = 15. На рис. показаны вход и выходы счетчика (без раскрытия схемы счетчика), а в табл. приведено состояние триггеров, соответствующее различному числу поступивших на вход импульсов.

При использовании десятичной системы счисления цифры разрядов десятичного числа в счетчике представляются в четырехразрядной двоичной форме, т.е. используется двоично-кодированная десятичная система счисления. Таким образом, для представления цифр каждого разряда десятичного числа (каждой декады) требуется четыре триггера, и если число десятичных разрядов к то число триггеров, необходимое для регистрации чисел в счетчике, равно 4к, а максимальное значение чисел N = 10* - 1. В табл. показана последовательность состояний триггеров в двухразрядном десятичном счетчике, приведенном на рис..

Наряду с суммирующими счетчиками, в которых в процессе счета каждое очередное число в счетчике на единицу превышает предыдущее, используются и такие счетчики, в которых в процессе счета числа убывают (эти счетчики называются вычитающими). Находят применение счетчики, которые допускают в процессе работы автоматическое переключение (реверс) из режима суммирующего счетчика в режим вычитающего счетчика и наоборот. Такие счетчики называются реверсивными. Хотя для построения счетчиков могут использоваться любые типы триггеров, на которых может быть организован счетный вход, в дальнейшем будем пользоваться только одним типом — JK-триггерами. В суммирующем счетчике поступление на вход очередного уровня лог. 1 (очередного импульса) вызывает увеличение на единицу хранимого в счетчике числа. Таким образом, в счетчике устанавливается число, которое получается путем суммирования предыдущего значения с единицей. Это суммирование проводится по обычным правилам сложения в двоичной системе счисления.

Заметим, что в процессе такого суммирования имеют место следующие особенности:

- если цифра некоторого разряда остается неизменной либо изменяется с 0 на 1, то при этом цифры более старших разрядов не изменяются;если цифра некоторого разряда изменяется с 1 на 0, то происходит инвертирование цифры следующего за ним более старшего разряда. С каждым входным импульсом число в счетчике увеличивается на единицу. Такое нарастание числа происходит до тех пор, пока после (n - 1)-го входного импульса (п — число разрядов в счетчике) в счетчике не устанавливается двоичное число 11.1. Далее с приходом n-го импульса в счетчике устанавливается исходное состояние 00...0, после чего счет ведется сначала. Таким образом, при непрерывной подаче на вход счетчик циклически с периодом 2п входных импульсов уставливается в исходное состояние.

|

|

|

|

|

Дата добавления: 2014-12-10; Просмотров: 1008; Нарушение авторских прав?; Мы поможем в написании вашей работы!