КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Запоминающие устройства и программируемые матрицы в устройствах автоматизиции

ЛЕКЦИЯ 6

Блоки ЗУ служат для запоминания больших массивов данных. Они становятся важнейшей составляющей частью цифровых компьютеров и систем управления технологическими процессами. Различают следующие блоки ЗУ и способы их организации:

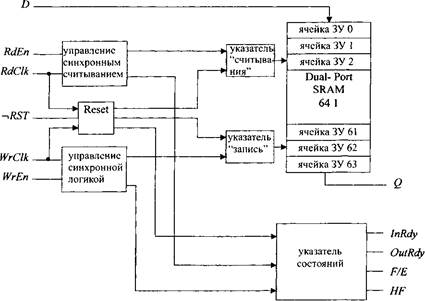

Полупроводниковые ЗУ реализуются на полупроводниковом чипе. ЗУ имеют высокую плотность ячеек памяти, следовательно, они могут запоминать большое количество данных в малом объеме. В устройствах применен последовательный доступ который означает, что данные вводятся и считываются только через один порт. Под этим понимаются ЗУ типа «пожарная цепочка», которые работают как сдвиговые регистры. Большей частью они организованны по принципу FIFO (first in, first out). Произвольный доступ говорит о том, что каждая запоминающая ячейка доступна независимо от других. ЗУ с адресацией по местоположению имеют адрес, делающий доступной любую ячейку ЗУ. При адресации по содержанию ЗУ информацию отыскивают по ассоциации с частью самой информации Например теплопроводность различных материалов хранится в одной области памяти или организация фреймовой структуры Энергозависимые ЗУ теряют информацию при выключении напряжения питания, тогда как энергонезависимые ЗУ сохраняют ее.

Постоянные ЗУ однажды программируются и с этого момента могут только читаться. Они энергонезависимы. В ЗУ с оперативной записью и считыванием можно многократно проводить запись и считывание. При побитовой организации ЗУ каждый бит доступен в отдельности. При пословной организации всегда одновременно считывается или записывается целое слово.

Информационная емкость ЗУ определяется как произведение количества слов ЗУ на их длину (разрядность). Схемы ЗУ подключаются как правило к шинной системе. Благодаря этому большое число различных ЗУ может быть подключено параллельно. Система шин должна давать возможность записывать в определенную ячейку ЗУ или считывать из нее. При этом различают:

Адресные шины Адресная шина подключается к каждому узлу ЗУ адресов, под которыми могут храниться данные или проводиться их поиск.

Управляющие шиныУправляющая шина содержит все линии, необходимые для управления схемным узлом. К ним относится линия, обеспечивающая выбор узла и содержащая вывод для выбора чипа (chip select, CS). Поскольку все узлы подключены к одной и той же адресной шине, то с помощью этой линии производится выбор соответствующего узла. С помощью линии считывание-запись можно осуществлять переключение между чтением и записью (read-write, RD-W).

Шины данных Шина данных подключается ко всем схемным узлам. Чтобы в линиях не создавались конфликты, выходы блоков ЗУ, влияющие на шину данных, должны быть выходами типа tristate («с тремя состояниями»). Их делают свободными для включения с помощью линии output enable (ОЕ, «разрешающий выход»), входящей в управляющую шину

ROM является сокращением для read only memory (ЗУ только с чтением, постоянное ЗУ, ПЗУ). ROM является схемой ЗУ, содержание данных в котором определяется изготовителем с помощью маски. Поэтому содержание данных фиксировано и их можно только читать. Запомненные данные являются энергозависимыми. ROM-схемы различаются числом битов, которые запомнены. Обычно используются ЗУ с длинами слов 1, 4, 8 и 16 бит.

В ROM, как и в большинстве других цифровых ЗУ, отдельные ячейки ЗУ расположены в виде матрицы (рис.). Ячейки ЗУ лежат в точках пересечений линий. К ним обращаются, подав напряжения 1 на строчную линию и на линию столбцов. Строчную линию называют числовой шиной (word line), линию столбцов называют шиной данных (data line). Преимущество данного устройства заключается в экономии шин. Для n2 ячеек требуется 2п шин против п2 в линейных устройствах.

Распределение числовых шин (word line) по адресам от A1 до А2 осуществляется строчным декодером. Столбцевой декодер осуществляет выбор шин данных. Поскольку шина данных наряду с выбором столбца осуществляет вывод накопленной информации к выходу, между декодером и матрицей ЗУ включается усилитель считывания. На рисунке показано ЗУ емкостью 8x8.

строчный декодер шина данных

Рис. 1. Принципиальная структурная схема ROM с емкостью 8x8.

Реализация ROM с емкостью 4x4 бит на основе КМОП технологии показана на рис.. Матрица ЗУ состоит из 16 n-канальных МОП ПТ. Если в ячейке ЗУ должна быть запомнена величина Н (то есть High), то контакта к стоку не должно быть. Технологически это может быть достигнуто с помощью одной единственной маски, которая, в зависимости от того, должен быть транзистор подсоединен или нет, создает соединение с транзистором на основе проводящей дорожки либо нет.

Сопротивлением нагрузки для шин данных служит р-канальный МОП ПТ. Столбцевой декодер все время подключает с помощью проходного транзистора к выходу одну из шин данных. Если с помощью строчного декодера выбирается какая-либо строка, переводя при этом соответствующий выход строчного декодера в состояние Н, то в этом случае шины данных, с которыми контактируют МОП ПТ, подтягиваются к низкому уровню напряжения L. В прочих случаях они остаются прежнем уровне. К выходу подключается только шина данных, проходной транзистор которой включен декодером данных.

Можно видеть, что для ячейки ЗУ необходим только один транзистор, что обуславливает высокую плотности ячеек в ЗУ. Логический символ ROM с емкостью IK х 8 бит показан на рис. Наряду с адресными входами данный схемный узел имеет вход выбора чипов (CS) и вход разрешения выхода (ОЕ). Вход CS служит для выбора ROM, когда к одной шине подключено большое количество ROM. Если в дополнении к этому вход ОЕ находится в состоянии 1, выход будет низкоомным.

PROM соответствует по структуре ROM, но с тем отличием, что она может программироваться пользователем. Можна запрограммировать процесс нагрева в печи или перемещение лазера по координатам и включение его при срабатывании датчиков положений. PROM также выполнена в виде матрицы, со столбцевым и строчным декодерам для адресного декодирования. Возможная реализация может быть разработана на основе рис. Стоки транзисторов в ячейках ЗУ PROM могут быть законтактированы вместо соединения проводящими дорожками соединением плавкими перемычками (fusible link). Это соединение показано на рис. В том случае, если должно быть запомнено состояние 1, плавкая перемычка при программировании расплавляется током. Как правило, для этого необходимо специальное программирующее устройство. Плавкая перемычка подобна плавкому предохранителю. Записанная информация является энергонезависимой. Однажды расплавленная плавкая перемычка не может быть вновь восстановлена. Поэтому подобные схемы обозначаются как OTP-ROM (OTP — one time programmable), то есть как ROM с однократным программированием.

Через EPROM обозначают erasable programmable ROM, стираемое программируемое ПЗУ, СППЗУ. EPROM по своей структуре соответствует ROM или PROM только на месте плавких перемычек или программируемых с помощью маски соединений находятся «стираемые» запоминающие элементы. элементов используются МОП ПТ с плавающим затвором (рис.). Эти МОП ПТ являются нормально-закрытыми транзисторами с дополнительным затвором, который не имеет внешнего вывода и называется плавающим затвором. Изначально этот затвор имеет нулевой потенциал. С помощью наведения заряда на плавающем затворе может быть осуществлена запись информации в ячейки. При отсутствии заряда на плавающем затворе транзистор функционирует как обычный n-канальный транзистор нормально-закрытого типа. Достаточно большое положительное напряжение на затворе включает транзистор. Это состояние ведет к уровню 1 на шине данных в том случае, если данная ячейка ЗУ выбрана числовой шиной.

В том случае, если должен быть запомнен уровень 0, на плавающем затворе должен быть накоплен отрицательный заряд. Теперь транзистор всегда заперт и при выборе ячейки с помощью числовой шины шина данных остается на уровне 0. Отрицательный заряд на плавающем затворе создается за счет туннелирования электронов через оксид. При повышенном напряжении между стоком и подложкой поле между затворным электродом и каналом достигает таких высоких значений и за счет лавинного пробоя появляются «горячие» электроны. Определенное количество электронов при этом может туннелировать через оксид. На плавающем затворе таким образом накапливается отрицательный заряд, который запирает транзистор. Облучение УФ светом в течение приблизительно 20 минут, ионизирует изолирующий материал, лежащий между затвором и истоком, благодаря чему заряд рассасывается. При этом информация стирается. Благодаря хорошим диэлектрическим свойствам оксида накопленный заряда остается стабильным в течение многих лет. Для программирования между истоком и стоком подается относительно высокое напряжение.

Через абревиатуру EEPROM обозначают электрически стираемое программируемое ПЗУ, ЭСППЗУ (electrically erasable programmable ROM). Эта схема ЗУ электрически записывается и электрически стирается. Единичная ячейка ЗУ также как и в EPROM, построена на одном МОП ПТ с плавающим затвором. Однако оксид между пла вающим затвором и каналом имеет меньшую толщину. Благодаря этому оказывается возможным, при повышенном напряжении между затвором и каналом, перемещать электроны с затвора в канал и обратно. Это происходит за счет эффекта туннелирования Фаулера - Нордхайма. EEPROM со специальными ячейками ЗУ иногда называют flash- EEPROM («мигающее» EEPROM). Они стираются не только полностью, но и поблочно. Если изменился режим обработки или используем другой нагревательный узел в печном агрегате то перепрогаммируем только часть микросхемы.

Коммерчески доступные ROM, PROM, EPROM, EEPROM часто совместимы по выводам корпуса так, что возможно применение в фазе разработки PROM или EPROM, которые при переходе к серийной продукции можно заменить на ROM или на PROM (табл).

Таблица. Обзор энергонезависимых ЗУ.

| Обозначение | Программирование | Стирание | |

| ROM (read only memory) | Маска | Однократное | Невозможно |

| PROM (программируемое ROM) программируемое полем ROM, однократное PROM (OTPROM) | Эл. | Однократное | Невозможно |

| EPROM (erasable ROM) | Эл. | Многократное | УФ облучение (20 минут), все содержимое ЗУ |

| EEPROM (electrically erasable ROM) flash-EEPROM | Эл. | Многократное | Электрическое, все содержимое ЗУ или по битам (20-100 мс) |

| EAPROM (electrically alterable ROM) | Эл. | Многократное | Электрическое, по битам (20-100 мс) |

| NOVRAM (nonvolatile RAM) | Эл. | Многократное | Электрическое, по битам (100 нс) |

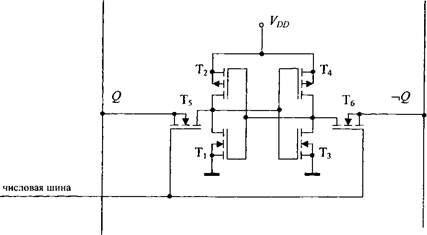

RAM является сокращением для random access memory (то есть ЗУ с произвольной выборкой, ЗУПВ). Под этим понимается схема ЗУ, в которое можно произвольно записывать и из которой можно произвольно считывать информацию. Различают статические RAM и динамические RAM (DRAM). В статических RAM в качестве ячеек памяти применяют триггеры. Схемы с высокой степенью интеграции работают в основном с использованием динамического запоминания информации в конденсаторах, управляемых одним транзистором. Ячейка ЗУ RAM показана на рис.. Она построена из двух КМОП- инверторов. Обращаться к ячейке ЗУ можно через числовую шину. Для выбора ячейки на числовую шину подается 0. Вследствие этого Т5 и Т6 становятся низкоомными.

В процессе записи можно, подав уровень 0 на шину данных DL, записать 0 в ЗУ. В таком случае Т3 будет открыт, а Т1 — закрыт.

Правый инвертор выдаст 1. После этого будет настроен на 0 левый инвертор. Точно также можно записать 1 в ЗУ, подав 0 на шину данных — DL. При считывании ячейка вновь выбирается с помощью числовой шины. На шинах данных может быть считан запомненный бит.

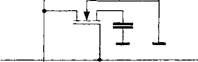

DRAM (динамическое RAM) представляет собой энергозависимое полупроводниковое ЗУ, в котором информация запоминается в конденсаторах. Благодаря очень простой структуре ячейки ЗУ подобные DRAM имеют очень большую информационную емкость. Запоминающий DRAM элемент показан на рис.. Приложение Н (низкий уровень соответствующий 0) к числовой линии позволяет выбрать ячейку ЗУ. Тогда накопленный на конденсаторе заряд может стекать по шине данных. Наличие заряда означает содержимое ЗУ со значением Н, а значению L (высокий уровень соответствует 1) соответствует отсутствие заряда. Чтение разрушает накопленный заряд, так что после каждого считывания заряд должен быть снова восстановлен (регенирирован).

Рис.2. Ячейка динамического RAM.

числовая шина

шина данных

Динамическое RAM организовано так, что процесс считывания автоматически связан с регенерацией заряда. Если ячейка ЗУ не считывается определенное время, заряд рассасывается, и информация теряется. Поэтому все запомненное содержимое должно периодически регенерироваться с помощью процесса считывания. Поскольку сопротивление МОП ПТ в выключенном состоянии очень велико, то достаточно очень малых емкостей конденсаторов, чтобы поддерживать время разряда в диапазоне миллисекунд. Каскадирование ЗУ. Во многих случаях появляется необходимость составления ЗУ из многих схем. Это имеет место, когда:

1. Не хватает емкости ЗУ. Следует различать, когда используются слишком короткие слова и когда применяется слишком малое количество ячеек ЗУ.

Блок ЗУ должен состоять из энергонезависимых ROM и энергозависимых ЗУ с записью и считыванием.

Из-за соображений стоимости необходимо комбинировать быстрые и медленные ЗУ.

Рис. 3. Блочная схема FIFO-ЗУ SN74ACT2226.

Пусть, например, в шине данных должно быть реализовано слово с длиной 8 бит, а в нашем распоряжении имеются схемы ЗУ с длиной слова 4 бит. В этом случае их можно соединить между собой так, как это показано на рис.. К отдельным схемам (ЗУ адресная шина и шина данных) подводятся идентично. Вход и выход данных первой схемы ЗУ подключена для передачи от нулевого до 3-го бита в шину данных, в то время как вход и выход данных другой схемы ЗУ подсоединены для передачи по шине данных от 4-го до 7-го битов. В тех случаях, когда число ячеек в ЗУ должно быть увеличено, необходимо включать вместе несколько ЗУ меньшей емкости.

Программируемые логические интегральные схемы - ИС (PLD) являются по своей сути стандартными схемными элементами, конфигурацию которых заказчики могут изменять в своих целях. Их электрические характеристики хорошо известны, поэтому можно получить очень достоверные модели для моделирования. Программируемые логические ИС могут быть разработаны достаточно надежно на основании моделирования. Стоимость одного образца, отнесенная к количеству вентилей, может оказаться очень малой, так как PLD могут быть изготовлены с высокой степенью интеграции. При этом с помощью небольшого ресурса проектирования можно добиться высокой степени использования вентилей. Поэтому PLD хорошо подходят для вариантов применения, когда требуется малое число образцов. В число их преимуществ входит и то, что они могут быть скорректированы за короткий срок.

К преимуществам программируемых логических ИС относится также то, что они тестируются изготовителем. Пользователю приходится проверять только топологию. С помощью них можно запрограммировать режим работы любого теплового агрегата, включение и выключени источника концентрированного потока энергии (КПЭ) с помощью очень простых манипуляций. Программируемые логические ИС обозначаются общим термином «programmable logic devices» (PLD).

Благодаря возможности конфигурации логики пользователем в PLD объединяются преимущества стандартных схемных узлов, характеристики которых оптимально согласованны с потребностями заказчиков.

Эти типы PLD различаются по способу программирования:

пережигаемые перемычки (fuse link), электрические пережигаемые соединения.

без пережигаемых перемычек (anti fuse), электрически формируемые соединения.

1-битовые RAM-ячейки;

триггеры.

EPROM-ячейки: долговременное хранение заряда, информация может стираться при воздействии ультра фиолетового облучения.

EEPROM-ячейки: долговременное хранение заряда, информация может стираться электрическим путем.

На основе энергонезависимых ЗУ ROM, EPROM, EEPROM и т.д., могут быть выполнятся логические схемы. Пусть, например, с помощью ROM с емкостью 16x2 бит должна быть реализована функция с четырьмя входными переменными и двумя выходными переменными. Под каждым из 16 адресов в ROM могут храниться запомнены значения обеих функций. Например последовательность включения лезера, плазматрона, электроннолучевой пушки, термопечи при наличии каких либо внешних условий или заданных параметров с пульта оператора. При этом еще возможно выполнение логической операции. Таким образом ROM, используемая как логическая схема, универсальна. Но оно может оказаться не эффективным, если функция имеет очень мало нулей в таблице истинности.

Применение ROM предпочтительно в следующих случаях:

Когда функция задана таблицей истинности. Тогда функция может быть без дальнейшей обработки введена в ЗУ.

Когда функция нуждается в большом количестве термов логического произведения (булевых логических термов).

Когда очевидно, что схема должна часто изменяться.

Когда в таблице истинности имеется большое число единиц.

ROM можно представить себе как логическую схему, в состав которой входят: фиксированная И-матрица, осуществляющая адресное декодирование, и программируемая масками ИЛИ-матрица.

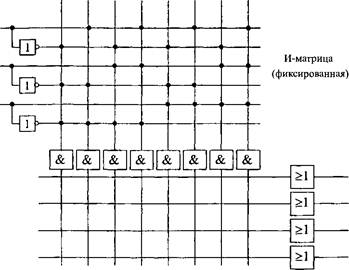

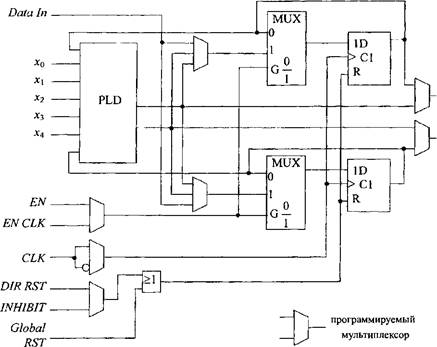

Как показано на рис., программируемые логические матрицы PLA (programmable logic array) включают программируемую И-матрицу. С помощью PLA можно непосредственно создавать нормальную дизъюктивноую нормальную форму (DNF), причем термы логического произведения (product term) реализуются с помощью И-матрицы, а суммарные термы с помощью ИЛИ-матрицы. При этом число термов логического произведения меньше 2П. Общие термы логического произведения могут быть поданы на многие логические входы.

В общую схему, приведенную на рис., могут быть введены некоторые улучшения.

Выходы должны иметь возможность подвергаться логической операции НЕ, так как для многих функций дополнение реализуется с меньшими затратами. Часто необходимы выходы типа tri-state («с тремя состояниями»). В этом случае имеет смысл, чтобы некоторые выходы могли бы быть использованы как входы. При определенных обстоятельствах выходные сигналы должны подвергаться промежуточному запоминанию Например что деталь находится в зоне лазерной резки. Поэтому многие PLA имеют на выходе триггеры.

С помощью введения инвертированной обратной связи из матицы ИЛИ могут быть при определенных обстоятельствах сэкономлены многие термы логического произведения.

|

Рис. PAL

PAL (Programmable Array Logic, «Программируемая матричная логика»), показанная на рис., является упрощенным вариантом PLD). Она имеет только лишь программируемую И-матрицу. ИЛИ- матрица ограничена несколькими термами логического произведения.Для программирования GAL вводится в режим программирования с помощью подведения определенного напряжения к одному из выводов (здесь вывод 2 = 16,8 В). На выводах набираются строки матрицы ЗУ и в соответствии с тактовым сигналом SCLK биты, которые лежат на контакте SDIN, передвигаются в сдвиговый регистр GAL, который снабжен электронной защитой от копирования. Когда введен бит защиты, программированные данные не могут быть считаны. Остается возможным только стирание. Гарантируется работоспособность GAL течение 10 лет. Процесс программирования продолжается в течение нескольких секунд. Программируемые полем вентильные матрицы (FPGA, field programmable gate arrays) представляют собой стандартные логические блоки, конфигурацию которых задает пользователь. Они состоят из многих PLD, взаимодействия между которыми обеспечивается матрицей соединений.

FPGA имеют следующие преимущества:

При применении специального программного обеспечения FPGA можно легко запрограммировать.

Не требуется какое-либо складирование схем у заказчика, поскольку стандартные логические блоки легко доступны.

При заказном же проектировании необходимо учесть время доставки продолжительностью в несколько месяцев, которое пройдет после выдачи заказа изготовителю интегральных схем.

Тестирование проводится просто.

FPGA тестируются изготовителем, поэтому пользователю достаточно проведения сокращенной программы испытаний

Затраты на разводку проводящих дорожек меньше. Благодаря этому при определенных обстоятельствах могут быть использованы более дешевые печатные платы.

В FPGA может быть реализована оптимальная архитектура. Поэтому они обладают высоким быстродействием.

Изменения проводятся легко, так как для этого достаточно только изменения программы.

FPGA представляет собой программируемые в соответствии с применением матрицы из логических блоков, выполненных большей частью в форме PLА (программируемых логических матриц). Логическая конфигурация устанавливается программой, которая хранится в статическом RAM, выполненном в кристалле. В начале работы статическое RAM загружается из ROM. В альтернативном варианте FPGA может быть запрограммирована, например, с помощью пережигаемых перемычек.

Рис. 4 Конфигурируемый логический блок (CLB) FPGA из семейства ХС3000 компании Xilinx.

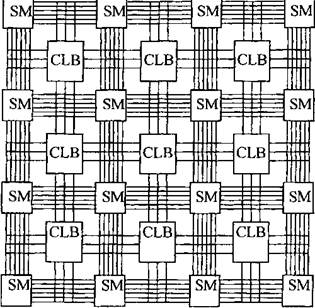

Архитектура FPGA может быть разделена на 3 типа блоков, из которых формируются различные конфигурации:

Логика сведена в образующие различные конфигурации блоки (CLB, configurable logic blocks). CLB соответствуют приблизительно одному PAL и могут быть запрограммированы с помощью конфигурационной программы. CLB размещены в форме матрицы в центральной части FPGA.

Входы и выходы реализованы с помощью блоков input/output (IO-blocks). Их можно включить как вход, выход, выход типа tri- state или как двунаправленный интерфейс. Ю-блоки размещены на краю FPGA рядом с выводами корпуса.

Соединительные линии реализованы в виде программируемой сети, которая подключает друг к другу CLB и Ю-блоки. Программируемые переключательные матрицы располагаются между CLB.

В настоящее время для построения логических устройств может быть использован универсальный элемент, называемый программируемой логической матрицей (ПЛМ). Такая матрица может быть настроена (запрограммирована) на выполнение любой логической функции определенной сложности.

На рис показана структура ПЛМ. Цепи входных переменных и их инверсий составляют горизонтальные цепи матрицы А вертикальными цепями которой служат так называемые цепи конъюнкции. Другую матрицу М2 образуют цепи конъюнкции с горизонтальными цепями выходов ух, у2,... В узлах матрицы М включены элементы, с помощью которых на цепях конъюнкции могут формироваться любые требуемые конъюнкции входных переменных, имеющиеся в узлах матрицы М2 элементы позволяют формировать на выходных цепях любые требуемые дизъюнкции функций, полученных на цепях конъюнкций. В процессе программирования ПЛМ в узлах матриц М1 и М2 производят подключение элементов, которые необходимы для реализации требуемых выходных логических функций в зависимости от того, прямая или инверсная функция реализуется, в выходные цепи могут включаться инверторы.

Матрица А, содержит горизонтальные цепи, на которых действуют входные переменные и их инверсии и вертикальные цепи, на которых формируются конъюнкциирВ отдельных узлах матрицы между ее вертикальными и горизонтальными цепями включены диоды. На вертикальной цепи образуется высокий потенциал (уровень лог.1) в том случае, когда на всех входах, идущих к узлам, содержащим диоды, действует высокий потенциал (уровень лог.1), закрывающий диоды. Если хотя бы на одном из таких входов низкий

потенциал (уровень лог.О), открывается диод и уровень лог.О с этого входа через открытый диод передается на вертикальную цепь матрицы.

На рис. крестиками показаны участки, в которых в процессе программирования создаются соединения. Включая в соответствующие узлы диоды, можно на выводахр{ сформировать любые конъюнкции входных переменных и их инверсий

В узлах матрицы М2 между цепями включены транзисторы, базы которых подключены к цепям а эмиттеры — к цепям у Если в цепи действует высокий потенциал (уровень лог. У), транзистор оказывается в открытом состоянии и высокий потенциал через открытый транзистор передается вцепь независимо от уровней на других выходах матрицы М

Программирование ПЛМ может осуществляться на заводе в процессе изготовления микросхемы на этапе формирования элементов в узлах матриц. Программирование может выполняться пользователем. В этом случае завод — изготовитель микросхемы выпускает ПЛМ со вставленными элементами во все узлы матриц. Пользователь, пропуская импульсы тока через определенные элементы, пережигает плавкие перемычки, последовательно включенные с элементами, и таким образом отключает их. Остающиеся элементы должны обеспечить требуемые функции на выходах ПЛМ.

В выпускаемых ПЛМ число входов может достигать 24, число выходов — 16, число цепей конъюнкций — 96. Структуры с программированием на заводе—изготовителе широко используются при выпуске БИС.

Ниже рассматриваются типовые узлы цифровых устройств, выполненные на программируемых логических устройствах с матричной структурой.

Шифратор. Рассмотрим построение шифратора, преобразующего унитарный десятичный код (с отображением десятичной цифры уровнем лог. 1 на одной из десяти цепей) в двоичный код 8421 где yi — входные сигналы; х- — выходные сигналы (значения разрядов кода 8421). На рис. показана ПЛМ, реализующая функции шифратора (для упрощения схемы здесь и в последующих схемах отсутствуют некоторые элементы схемы рис.— источник питания и резисторы).

Дешифратор. Реализацию на ПЛМ дешифратора рассмотрим на примере дешифратора, преобразующего трехразрядный двоичный код (jc,, х2, jc) подаваемый на вход, в унитарный 8- разрядный код на выходе О.

Функционирование такого дешифратора определяется следующими логическими выражениями: настроенная на реализацию данных функций ПЛМ приведена на рис.. На рис. показана схема мультиплексора с четырьмя входами (Z)3, Z)2, Z),, D0). Здесь >4,, A0 — адресные входы; С— вход для подачи сигнала разрешения выдачи; у — выход.

На рис. приведена схема демультиплексора с четырьмя выходами Здесь D — вход; А,, А0 — адресные входы; С — вход сигнала разрешения выдачи. Регистр. Регистр является устройством с памятью (устройством последовательностного типа

Реализация такого типа устройства на ПЛМ требует наличия в ПЛМ элементов памяти — триггеров, образующих регистр. В такой ПЛМ матрицы А, и М2 используются для построения комбинационной схемы, с помощью которой регистру придаются дополнительные свойства, кроме простого хранения кода. Одним из таких свойств может быть, например, сдвиг содержимого регистра влево или вправо (на один или несколько разрядов). Рассмотрим построение универсального регистра, обладающего следующими возможностями: прием извне в регистр кодовой комбинации, поступающей в регистр; циклический сдвиг содержимого регистра влево или вправо (сдвиг с передачей выдвигаемой из регистра цифры в освобождающий при сдвиге разряд регистра); сдвиг вправо с приемом в освобождающийся старший разряд регистра цифры, подаваемой на вход.

|

|

Дата добавления: 2014-12-10; Просмотров: 1777; Нарушение авторских прав?; Мы поможем в написании вашей работы!