КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Программная модель внешнего устройства

|

|

|

|

Организация ввода/вывода в микопроцессорной системе

Микропроцессоры INTEL

Процессоры фирмы INTEL являются не самым лучшим решением для персональных компьютеров, но благодаря тому, что 8086 наследуют все свойства предыдущих моделей — они получили самое широкое распространение в мире. Наряду с INTEL аналогичные процессоры выпускают и другие фирмы — AMD, Texas Instruments, Cyrix, NexGen, Motorola и другие. Многие из них отличаются не только количеством элементов на кристалле, но и системой команд, архитектурой.

34. Организация ввода/вывода в микропроцессорной системе (МПС).

Вводом/выводом (ВВ) называется передача данных между ядром ЭВМ, включающим в себя микропроцессор и основную память, и внешними устройствами (ВУ). Это единственное средство взаимодействия ЭВМ с "внешним миром", и архитектура ВВ (режимы работы, форматы команд, особенности прерываний, скорость обмена и др.) непосредственно влияет на эффективность всей системы. За время эволюции ЭВМ подсистема ВВ претерпела наибольшие изменения благодаря расширению сферы применения ЭВМ и появлению новых внешних устройств. Особенно важную роль средства ВВ играют в управляющих ЭВМ. Разработка аппаратных средств и программного обеспечения ВВ является наиболее сложным этапом проектирования новых систем на базе ЭВМ, а возможности ВВ серийных машин представляют собой один из важных параметров, определяющих выбор машины для конкретного применения.

35.Программная модель внешнего устройства.

Подключение внешних устройств к системной шине осуществляется посредством электронных схем, называемых контроллерами ВВ (интерфейсами ВВ). Они согласуют уровни электрических сигналов, а также преобразуют машинные данные в формат, необходимый устройству, и наоборот. Обычно контроллеры ВВ конструктивно оформляются вместе с процессором в виде интерфейсных плат.

|

|

|

В процессе ввода/вывода передается информация двух видов: управляющие данные (слова) и собственно данные, или данные-сообщения. Управляющие данные от процессора, называемые также командными словами или приказами, инициируют действия, не связанные непосредственно с передачей данных, например запуск устройства, запрещение прерываний и т.п. Управляющие данные от внешних устройств называются словами состояния; они содержат информацию об определенных признаках, например о готовности устройства к передаче данных, о наличии ошибок при обмене и т.п. Состояние обычно представляется в декодированной форме - один бит для каждого признака.

Регистр, содержащий группу бит, к которой процессор обращается в операциях ВВ, образует порт ВВ. Таким образом, наиболее общая программная модель внешнего устройства, которое может выполнять ввод и вывод, содержит четыре регистра ВВ: регистр выходных данных (выходной порт), регистр входных данных (входной порт), регистр управления и регистр состояния (рис. 3.1). Каждый из этих регистров должен иметь однозначный адрес, который идентифицируется дешифратором адреса. В зависимости от особенностей устройства общая модель конкретизируется, например, отдельные регистры состояния и управления объединяются в один регистр, в устройстве ввода (вывода) имеется только регистр входных (выходных) данных, для ввода и вывода используется двунаправленный порт.

Рис. 3.1. Программная модель внешнего устройства

Непосредственные действия, связанные с вводом/выводом, реализуются одним из двух способов, различающихся адресацией регистров ВВ.

Интерфейс с изолированными шинами характеризуется раздельной адресацией памяти и внешних устройств при обмене информацией. Изолированный ВВ предполагает наличие специальных команд ввода/вывода, общий формат которых показан на рис. 3.2. При выполнении команды ввода IN содержимое адресуемого входного регистра PORT передается во внутренний регистр REG процессора, а при выполнении команды OUT содержимое регистра REG передается в выходной порт PORT. В процессоре могут быть и другие команды, относящиеся к ВВ и связанные с проверкой и модификацией содержимого регистра управления и состояния.

|

|

|

Рис. 3.2. Команды ввода/вывода (общий формат)

Нетрудно заметить, что в этом способе адресное пространство портов ввода и вывода изолировано от адресного пространства памяти, т.е. в ЭВМ один и тот же адрес могут иметь порт ВВ и ячейка памяти. Разделение адресных пространств осуществляется с помощью управляющих сигналов, относящихся к системам ВВ и памяти (MEMRD# - считывание данных из памяти, MEMWR# - запись данных в память, IORD# - чтение порта ВВ, IOWR# - запись в порт ВВ) (# - активный низкий уровень сигналов).

В ЭВМ, рассчитанной на изолированный ВВ, нетрудно перейти к ВВ, отображенному на память. Если, например, адресное пространство памяти составляет 64 Кбайт, а для программного обеспечения достаточно 32 Кбайт, то область адресов от 0 до 32 К-1 используется для памяти, от 32 К до 64 К-1 - для ввода/вывода. При этом признаком, дифференцирующим обращения к памяти и портам ВВ, может быть старший бит адреса.

Таким образом, интерфейс с общими шинами (ввод/вывод с отображением на память) имеет организацию, при которой часть общего адресного пространства отводится для внешних устройств, регистры которых адресуются так же, как и ячейки памяти. В этом случае для адресации портов ВВ используются полные адресные сигналы: READ - чтение, WRITE - запись.

В операционных системах ЭВМ имеется набор подпрограмм (драйверов ВВ), управляющих операциями ВВ стандартных внешних устройств. Благодаря им пользователь может не знать многих особенностей ВУ и интерфейсов ВВ, а применять четкие програ ммные протоколы.

36.Форматы передачи данных в МПС.

В МПС существует три способа передачи информации:

· асинхронный;

· синхронный;

· смешанный.

Асинхронный способ характеризуется тем, что сигналы передаются с произвольными промежутками времени.

|

|

|

Синхронный способ характеризуется тем, что сигналы передаются строго периодично во времени.

Смешанный способ характеризуется тем, что байты передаются асинхронно, а биты внутри байтов синхронно.

Асинхронный способ. Асинхронный способ обеспечивает передачу информации по единственной линии. Для надежной синхронизации обмена в асинхронном режиме

1) передатчик и приемник настраивают на работу с одинаковой частотой;

2) передатчик формирует стартовый и стоповый биты, отмечающие начало и конец посылки;

3) передача ведется короткими посылками (5..9 бит), а частоты передачи выбираются сравнительно низкими.

Синхронный способ. В синхронном способе передачи информации выделяют изохронный метод.

Синхронизация бывает:

· внутренняя

· внешняя

Изохронный метод. В этом методе передачи информации возможна потеря данных. Здесь сам приемник определяет какие данные принимать, а какие нет (например для звуковой информации).

Внешняя синхронизация. Сигналы синхронизации поступают вместе с данными. В этом случае форма сигналов может быть неправильной. Поэтому внешняя синхронизация используется только при передаче на небольшие расстояния, т.е. внутри платы.

Внутренняя синхронизация. Сигналы синхронизации вырабатываются внутренними схемами и поступают на все цифровые узлы.

Достоинства:

· достаточно двух линий: сигнал и земля;

· высокая частота;

· высокая надежность связи;

При синхронном методе передатчик генерирует две последовательности - информационную TxD и синхроимпульсы CLK, которые передаются на

приемник по разным линиям (Рис. 10.2.).

|

Рис. 10.2. Последовательный синхронный обмен с внешней синхронизацией

Синхроимпульсы обеспечивают синхронизацию передаваемых бит, а начало передачи отмечается по-разному.

При организации внешней синхронизации сигнал начала передачи BD генерируется передатчиком и передается на приемник по специальной линии (Рис. 10.2).

В системах с внутренней синхронизацией отсутствует линия BD, а на линию данных генерируются специальные коды длиной 1-2 байта - “символы синхронизации”. Для каждого приемника предварительно определяются конкретные синхросимволы, таким образом можно осуществлять адресацию конкретного абонента из нескольких, работающих на одной линии. Каждый приемник постоянно принимает биты с RxD, формирует символы и сравнивает с собственными синхросимволами. При совпадении синхросимволов последующие биты поступают в канал данных приемника.

|

|

|

37.Параллельная передача данных (Простой параллельный контроллер вывода и вывода).

параллельная передача данных между контроллером и ВУ является по своей организации наиболее простым способом обмена. Для организации параллельной передачи данных помимо шины данных, количество линий в которой равно числу одновременно передаваемых битов данных, используется минимальное количество управляющих сигналов.

В простом контроллере ВУ, обеспечивающем побайтную передачу данных во внешнее устройство (рис. 2.5), в шине связи с ВУ используются всего два управляющих сигнала — «Выходные данные готовы» и «Данные приняты».

Для формирования управляющего сигнала «Выходные данные готовы» и приема из ВУ управляющего сигнала «Данные приняты» в контроллере используется одноразрядный адресуемый регистр состояния и управления А2. Одновременно с записью очередного байта данных из шины данных системного интерфейса в адресуемый регистр данных контроллера (порт вывода А1) в регистр состояния и управления записывается логическая единица. Тем самым формируется управляющий сигнал «Выходные данные готовы» в шине связи с ВУ.

ВУ, приняв байт данных, управляющим сигналом «Данные приняты» обнуляет регистр состояния контроллера. При этом формируются:

управляющий сигнал системного интерфейса «Готовность ВУ»;

признак готовности ВУ к обмену, передаваемый в процессор по одной из линий шины данных системного интерфейса посредством стандартной операции ввода при реализации программы асинхронного обмена.

Логика управления контроллера обеспечивает селекцию адресов регистров контроллера, прием управляющих сигналов системного интерфейса и формирование на их основе внутренних управляющих сигналов контроллера, формирование управляющего сигнала системного интерфейса «Готовность ВУ». Для сопряжения регистров контроллера с шинами адреса и данных системного интерфейса в контроллере используются приемники шины адреса и приемопередатчики шины данных.

Рис. 2.5. Простой параллельный интерфейс (контроллер) вывода

Рассмотрим на примере, каким образом контроллер ВУ обеспечивает параллельную передачу данных в ВУ под управлением программы асинхронного обмена. Алгоритм асинхронного обмена в данном случае передачи прост.

1. Проверка готовности ВУ к приему данных.

Проверка содержимого регистра А2, т. е. готовности ВУ к приему данных. При выполнении команды процессор по шине адреса передает в контроллер адрес А2, сопровождая его сигналом «Ввод». Логика управления контроллера, реагируя на эти сигналы, обеспечивает передачу в процессор содержимого регистра состояния и управления А2 по одной из линий шины данных системного интерфейса (например, это может быть старший — 15-й разряд шины данных).

Процессор проверяет значение старшего (знакового) разряда принятого слова данных. Единица в старшем разряде (знак минус) указывает на неготовность ВУ к приему данных и, следовательно, на необходимость возврата к проверке содержимого А2, т. е. процессор, выполняя две первые команды, ожидает готовности ВУ к приему данных. Нуль в старшем разряде подтверждает готовность ВУ и, следовательно, возможность передачи байта данных.

2. Передача данных.

Процессор по шине адреса передает в контроллер адрес А1, а по шине данных — байт данных, сопровождая их сигналом «Вывод». Логика управления контроллера обеспечивает запись байта данных с шины данных в регистр данных А1 и устанавливает в единицу регистр состояния и управления А2, формируя тем самым управляющий сигнал для ВУ «Выходные данные готовы». ВУ принимает байт данных и управляющим сигналом «Данные приняты» обнуляет регистр состояния и управления А2. Контроллер ВУ по этому сигналу формирует и передает в процессор сигнал «Готовность ВУ», который в данном случае извещает процессор о приеме байта данных внешним устройством и завершает цикл вывода данных в команде пересылки.

Рис. 2.6. Простой параллельный интерфейс (контроллер) ввода

Блок-схема простого контроллера ВУ (параллельного интерфейса), обеспечивающего побайтный прием данных из ВУ, приведена на рис. 2.6. В этом контроллере при взаимодействии с внешним устройством также используются два управляющих сигнала — «Данные от ВУ готовы» и «Данные приняты».

Для формирования управляющего сигнала «Данные приняты» и приема из ВУ управляющего сигнала «Данные от ВУ готовы» используется одноразрядный адресуемый регистр состояния и управления А2.

ВУ записывает в регистр данных контроллера А1 очередной байт данных и управляющим сигналом «Данные от ВУ готовы» устанавливает в единицу регистр состояния и управления А2.

При этом формируются: управляющий сигнал системного интерфейса «Готовность ВУ»; признак готовности ВУ к обмену, передаваемый в процессор по одной из линий шины данных системного интерфейса посредством операции ввода при реализации программы асинхронного обмена.

Тем самым контроллер извещает процессор о готовности данных в регистре A1. Процессор, выполняя программу асинхронного обмена, читает байт данных из регистра данных контроллера и обнуляет регистр состояния и управления А2. При этом формируется управляющий сигнал «Данные приняты» в шине связи с ВУ.

Логика управления контроллера и приемопередатчики шин системного интерфейса выполняют те же функции, что и в контроллере вывода (см. рис. 2.5).

Рассмотрим работу параллельного интерфейса ввода при реализации программы асинхронного обмена. Алгоритм асинхронного ввода так же прост, как и асинхронного вывода.

Проверка наличия данных в регистре данных контроллера А1.

Процессор проверяет значение старшего (знакового) разряда принятого слова данных. Единица в знаковом разряде (содержимое регистра А2) подтверждает, что данные от ВУ записаны в регистр данных контроллера и необходимо переслать их в шину данных. Нуль в знаковом разряде указывает на неготовность данных от ВУ и, следовательно, на необходимость вернуться к проверке готовности

Передача данных.

Если данные готовы (логическая 1 в регистре А2), то процессор передает в контроллер по шине адреса системного интерфейса адрес А1, сопровождая его сигналом «Ввод». Логика управления контроллера в ответ на сигнал «Ввод» обеспечивает передачу байта данных из регистра данных А1 на шину данных, сопровождая их сигналом «Готовность ВУ», который подтверждает наличие данных от ВУ на шине данных. Затем логика управления обнуляет регистр состояния и управления А2, формируя тем самым управляющий сигнал для ВУ «Данные приняты». Таким образом, завершается цикл ввода данных в команде пересылки.

Как видно из рассмотренных примеров, для приема или передачи одного байта данных процессору необходимо выполнить всего несколько команд, время осуществления которых и определяет максимально достижимую скорость обмена данными при параллельной передаче. При этом время обработки байта данных в электронных схемах контроллера можно не учитывать, так как оно существенно меньше времени выполнения одной команды процессора. Таким образом, при параллельной передаче обеспечивается довольно высокая скорость обмена данными, которая на практике ограничивается только быстродействием ВУ.

Простота реализации и высокая скорость обмена, присущие параллельной передаче данных, обеспечили широкое распространение этого способа обмена данными с внешними устройствами в ЭВМ.

38.Последавательная передача данных (Контроллер последовательной синхронной передачи).

Использование последовательных линий связи для обмена данными с ВУ возлагает на контроллеры ВУ дополнительные по сравнению с контроллерами для параллельного обмена функции. Во-первых, возникает необходимость преобразования формата данных: из параллельного формата, в котором они поступают в контроллер ВУ из системного интерфейса микроЭВМ, в последовательный при передаче в ВУ и из последовательного в параллельный при приеме данных из ВУ. Во-вторых, требуется реализовать соответствующий режиму работы ВУ способ обмена данными: синхронный или асинхронный.

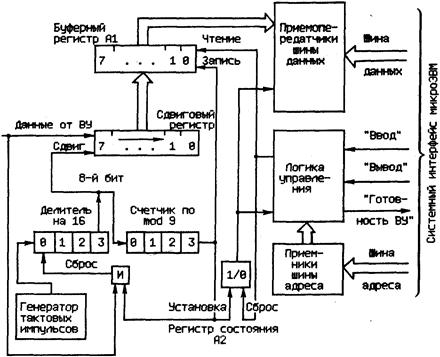

Синхронные последовательные интерфейсы. Простой контроллер для синхронной передачи данных в ВУ по последовательной линии связи (последовательный интерфейс) представлен на рис. 2.7.

Восьмиразрядный адресуемый буферный регистр контроллера А1 служит для временного хранения байта данных до его загрузки в сдвиговый регистр. Запись байта данных в буферный регистр из шины данных системного интерфейса производится так же, как и в параллельном интерфейсе только при наличии единицы в одноразрядном адресуемом регистре состояния контроллера А2. Единица в регистре состояния указывает на готовность контроллера принять очередной байт в буферный регистр. Содержимое регистра А2 передается в процессор по одной из линий шины данных системного интерфейса и используется для формирования управляющего сигнала системного интерфейса «Готовность ВУ». При записи очередного байта в буферный регистр А1 обнуляется регистр состояния А2.

Рис. 2.7. Контроллер последовательной синхронной передачи

Преобразование данных из параллельного формата, в котором они поступили в буферный регистр контроллера из системного интерфейса, в последовательный и передача их в линию связи производятся в сдвиговом регистре с помощью генератора тактовых импульсов и двоичного трехразрядного счетчика импульсов следующим образом.

Последовательная линия связи контроллера с ВУ подключается к выходу младшего разряда сдвигового регистра. По очередному тактовому импульсу содержимое сдвигового регистра сдвигается на один разряд вправо и в линию связи «Данные» выдается значение очередного разряда. Одновременно со сдвигом в ВУ передается по отдельной линии «Синхронизация» тактовый импульс. Таким образом, каждый передаваемый по линии «Данные» бит информации сопровождается синхронизирующим сигналом по линии «Синхронизация», что обеспечивает его однозначное восприятие на приемном конце последовательной линии связи.

Количество переданных в линию тактовых сигналов, а следовательно, и переданных бит информации подсчитывается счетчиком тактовых импульсов. Как только содержимое счетчика становится равным 7, т. е. в линию переданы 8 бит (1 байт) информации, формируется управляющий сигнал «Загрузка», обеспечивающий запись в сдвиговый регистр очередного байта из буферного регистра. Этим же управляющим сигналом устанавливается в «1» регистр состояния. Очередным тактовым импульсом счетчик будет сброшен в «0», и начнется очередной цикл выдачи восьми битов информации из сдвигового регистра в линию связи.

Синхронная последовательная передача отдельных битов данных в линию связи должна производиться без какого-либо перерыва, и следующий байт данных должен быть загружен в буферный регистр из системного интерфейса за время, не превышающее времени передачи восьми битов в последовательную линию связи.

При записи байта данных в буферный регистр обнуляется регистр состояния контроллера. Нуль в этом регистре указывает, что в линию связи передается байт данных из сдвигового регистра, а следующий передаваемый байт данных загружен в сдвиговый регистр.

Простой контроллер для последовательного синхронного приема данных из ВУ (рис. 2.8) состоит из тех же компонентов, что и контроллер для синхронной последовательной передачи, за исключением генератора тактовых импульсов.

Буферный регистр контроллера А1 служит для временного хранения байта данных, поступившего из сдвигового регистра. Чтение байта данных в системный интерфейс из буферного регистра производится так же, как и в параллельном интерфейсе Единица в регистре состояния контроллера А2 указывает на готовность контроллера передать очередной байт данных в системный интерфейс.

Данные, поступающие из линии связи в последовательном коде, преобразуются в контроллере в параллельный код с помощью сдвигового регистра и трехразрядного двоичного счетчика тактовых импульсов следующим образом.

Входная последовательная линия связи «Данные» подключается в контроллере к последовательному входу сдвигового регистра, а входная линия

Рис. 2.8. Контроллер последовательного синхронного приема

«Синхронизация» — на управляющий вход «Сдвиг» сдвигового регистра и на вход счетчика тактовых импульсов. По очередному тактовому сигналу, поступившему от синхрогенератора ВУ по линии «Синхронизация», производятся сдвиг содержимого сдвигового регистра на один разряд влево и запись очередного бита данных из линии связи «Данные» в младший разряд этого регистра. Одновременно увеличивается на единицу содержимое счетчика тактовых импульсов. Как только содержимое счетчика становится равным 7, т. е. в сдвиговый регистр приняты последовательно восемь битов информации, формируется управляющий сигнал «Запись», который обеспечивает запись в буферный регистр очередного принятого байта из сдвигового регистра. Этим же управляющим сигналом устанавливается в «1» регистр состояния.

За время приема в сдвиговый регистр следующих восьми битов информации байт данных из буферного регистра должен быть передан в шину данных системного интерфейса микроЭВМ. При этой передаче обнуляется регистр состояния контроллера и нуль в этом регистре означает, что в сдвиговый регистр принимается из линии связи очередной байт информации.

Асинхронные последовательные интерфейсы. Организация асинхронного последовательного обмена данными с ВУ осложняется тем, что на передающей и приемной стороне последовательной линии связи используются настроенные на одну частоту, но физически разные генераторы тактовых импульсов и, следовательно, общая синхронизация отсутствует. Рассмотрим на примерах организацию контроллеров последовательных интерфейсов для последовательных асинхронных передачи и приема данных.

Простейший контроллер для асинхронной передачи данных в ВУ по последовательной линии связи представлен на рис. 2.9. Он предназначен для передачи данных в формате с двумя стоповыми битами.

Рис. 2.9. Контроллер последовательной асинхронной передачи

После передачи очередного байта данных в регистр состояния А2 записывается «1». Единичный выходной сигнал регистра А2 информирует процессор о готовности контроллера к приему следующего байта данных и передаче его по линии связи в ВУ. Этот же сигнал запрещает формирование импульсов со схемы выработки импульсов сдвига — делителя частоты сигналов тактового генератора на 16. Счетчик импульсов сдвига (счетчик по той 10) находится в нулевом состоянии, и его единичный выходной сигнал поступает на вентиль «И», подготавливая цепь выработки сигнала загрузки сдвигового регистра.

Процесс передачи байта данных начинается с того, что процессор, выполняя команду «Вывод», выставляет этот байт на шине данных. Одновременно процессор формирует управляющий сигнал системного интерфейса «Вывод», по которому производятся запись передаваемого байта в буферный регистр А1, сброс регистра состояния А2 и формирование на вентиле И сигнала «Загрузка». Передаваемый байт переписывается в разряды 1,...,8 сдвигового регистра, в нулевой разряд сдвигового регистра записывается 0 (стартовый бит), а в разряды 9 и 10— 1 (стоповые биты). Кроме того, снимается сигнал «Сброс» с делителя частоты, он начинает накапливать импульсы генератора тактовой частоты и в момент приема шестнадцатого тактового импульса вырабатывает импульс сдвига.

На выходной линии контроллера «Данные» поддерживается состояние 0 (значение стартового бита) до тех пор, пока не будет выработан первый импульс сдвига. Импульс сдвига изменит состояние счетчика импульсов сдвига и перепишет в нулевой разряд сдвигового регистра первый информационный бит передаваемого байта данных. Состояние, соответствующее значению этого бита, будет поддерживаться на линии «Данные» до следующего импульса сдвига.

Рис. 2.10. Контроллер последовательного асинхронного приема

Аналогично будут переданы остальные информационные биты, первый стоповый бит и, наконец, второй стоповый бит, при передаче которого счетчик импульсов сдвига снова установится в нулевое состояние. Это приведет к записи 1 в регистр состояния А2. Единичный сигнал с выхода регистра А2 запретит формирование импульсов сдвига, а также информирует процессор о готовности к приему нового байта данных. После завершения передачи очередного кадра (стартового бита, информационного байта и двух стоповых битов) контроллер поддерживает в линии связи уровень логической единицы (значение второго стопового бита).

Уровень логической единицы поступает по линии «Данные» в контроллер для асинхронного приема данных (рис. 2.10). Этот уровень создает условия для выработки сигнала, запрещающего работу делителя частоты генератора тактовых импульсов. Действительно, после приема предыдущего байта данных счетчик импульсов сдвига (счетчик по тоа 9) находится в нулевом состоянии и на вентиль И поступают два единичных сигнала: со счетчика сдвигов и из линии «Данные». На выходе вентиля И вырабатывается сигнал сброса делителя частоты сигналов тактового генератора, запрещающий формирование импульсов сдвига.

В момент смены стопового бита на стартовый бит (момент начала передачи нового кадра) на линии «Данные» появится уровень логического нуля и тем самым снят сигнал сброса с делителя частоты. Состояние 4-разрядного двоичного счетчика (делителя частоты) начнет изменяться. Когда на счетчике накопится значение 8, он выдаст сигнал, поступающий на входы сдвигового регистра и счетчика импульсов сдвига. Так как частота сигналов генератора тактовых импульсов приемника должна совпадать с частотой генератора тактовых импульсов передатчика, то сдвиг (считывание) бита произойдет примерно на середине временного интервала, отведенного на передачу бита данных, т. е. времени, необходимого для выработки шестнадцати тактовых импульсов. Это делается для уменьшения вероятности ошибки из-за возможного различия частот генераторов передатчика и приемника, искажения формы передаваемых сигналов (переходные процессы) и т. п. Следующий сдвиг произойдет после прохождения шестнадцати тактовых импульсов, т. е. на середине временного интервала передачи первого информационного бита.

При приеме в сдвиговый регистр девятого бита кадра (восьмого информационного бита) из него «выдвинется» стартовый бит и, следовательно, в сдвиговом регистре будет размещен весь принятый байт информации. В этот момент счетчик импульсов сдвига придет в нулевое состояние и на его выходе будет выработан единичный сигнал, по которому:

содержимое сдвигового регистра перепишется в буферный регистр;

в регистр состояния А2 запишется 1 и он будет информировать процессор об окончании приема очередного байта;

вентиль И подготовится к выработке сигнала «Сброс» (этот сигнал сформируется после прихода первого стопового бита).

Получив сигнал готовности (1 в регистре А2), процессор выполнит команду «Ввод». При этом вырабатывается управляющий сигнал системного интерфейса «Ввод», по которому производятся пересылка принятого байта данных из буферного регистра в процессор (сигнал «Чтение») и сброс регистра состояния А2.

Отметим, что для простоты изложения в контроллере на рис. 2.10 не показаны схемы контроля стоповых битов принимаемого кадра. Не показаны также схемы контроля четности или нечетности (паритета) передаваемой информации (обычно в передаваемом байте восьмому биту придается значение 0 или 1 так, чтобы в этом байте было четное количество единиц). В реальных контроллерах имеются такие схемы, и если контроллер не принимает из линии связи нужного количества стоповых битов или вырабатывается сигнал ошибки паритета в схеме контроля четности, то принятые в текущем кадре биты данных игнорируются и контроллер ожидает поступления нового стартового бита.

Обмен данными с ВУ по последовательным линиям связи широко используется в современных микроЭВМ, особенно в тех случаях, когда не требуется высокой скорости обмена. Вместе с тем применение в микроЭВМ последовательных линий связи с ВУ обусловлено двумя важными причинами. Во-первых, последовательные линии связи просты по своей организации: два провода при симплексной и полудуплексной передаче или четыре — при дуплексной. Во-вторых, в микроЭВМ широко используются ВУ, обмен с которыми необходимо вести в последовательном коде.

В современных микроЭВМ применяют, как правило, универсальные контроллеры для последовательного обмена, т. е. обеспечивающие как синхронный, так и асинхронный режим обмена данными с ВУ.

39.Асинхронный последовательный интерфейс.(контроллер…)

|

|

|

|

|

Дата добавления: 2015-04-23; Просмотров: 1892; Нарушение авторских прав?; Мы поможем в написании вашей работы!