КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Асинхронный последовательный интерфейс 1 страница

|

|

|

|

Организация асинхронного последовательного обмена данными с внешним устройством осложняется тем, что на передающей и приемной стороне последовательной линии связи используются настроенные на одну частоту, но физически разные генераторы тактовых импульсов и, следовательно, общая синхронизация отсутствует. Рассмотрим на примерах организацию контроллеров последовательных интерфейсов для последовательных асинхронных передачи и приема данных.

Простейший контроллер для асинхронной передачи данных в ВУ по последовательной линии связи представлен на рис. 3.8. Он предназначен для передачи данных в формате с двумя стоповыми битами.

Рис. 3.8. Контроллер последовательной асинхронной передачи

После передачи очередного байта данных в регистр состояния А2 записывается 1. Единичный выходной сигнал регистра А2 информирует процессор о готовности контроллера к приему следующего байта данных и передаче его по линии связи в ВУ. Этот же сигнал запрещает формирование импульсов со схемы выработки импульсов сдвига - делителя частоты сигналов тактового генератора на 16. Счетчик импульсов сдвига (счетчик по mod 10) находится в нулевом состоянии и его единичный выходной сигнал поступает на вентиль И, подготавливая цепь выработки сигнала загрузки сдвигового регистра.

Процесс передачи байта данных начинается с того, что процессор, выполняя команду "Вывод", выставляет этот байт на шине данных. Одновременно процессор формирует управляющий сигнал системного интерфейса "Вывод", по которому производятся запись передаваемого байта в буферный регистр А1, сброс регистра состояния А2 и формирование на вентиле И сигнала "Загрузка". Передаваемый байт переписывается в разряды 1,..., 8 сдвигового регистра, в нулевой разряд сдвигового регистра записывается 0 (стартовый бит), а в разряды 9 и 10 - 1 (стоповые биты). Кроме того, снимается сигнал "Сброс" с делителя частоты, он начинает накапливать импульсы генератора тактовой частоты и в момент приема шестнадцатого тактового импульса вырабатывает импульс сдвига.

|

|

|

На выходной линии контроллера "Данные" поддерживается состояние 0 (значение стартового бита) до тех пор, пока не будет выработан первый импульс сдвига. Импульс сдвига изменит состояние счетчика импульсов сдвига и перепишет в нулевой разряд сдвигового регистра первый информационный бит передаваемого байта данных. Состояние, соответствующее значению этого бита, будет поддерживаться на линии "Данные" до следующего импульса сдвига.

Аналогично будут переданы остальные информационные биты, первый стоповый бит и, наконец, второй стоповый бит, при передаче которого счетчик импульсов сдвига снова установится в нулевое состояние. Это приведет к записи 1 в регистр состояния А2. Единичный сигнал с выхода регистра А2 запретит формирование импульсов сдвига, а также информирует процессор о готовности к приему нового байта данных. После завершения передачи очередного кадра (стартового бита, информационного байта и двух стоповых бит) контроллер поддерживает в линии связи уровень логической единицы (значение второго стопового бита).

Рис. 3.9. Контроллер последовательного асинхронного приема

Уровень логической единицы поступает по линии "Данные" в контроллер для асинхронного приема данных (рис. 3.9). Этот уровень создает условия для выработки сигнала, запрещающего работу делителя частоты генератора тактовых импульсов. Действительно, после приема предыдущего байта данных счетчик импульсов сдвига (счетчик по mod 9) находится в нулевом состоянии и на вентиль И поступают два единичных сигнала: со счетчика сдвигов и из линии "Данные". На выходе вентиля И вырабатывается сигнал сброса делителя частоты сигналов тактового генератора, запрещающий формирование импульсов сдвига.

|

|

|

В момент смены стопового бита на стартовый бит (момент начала передачи нового кадра) на линии "Данные" появится уровень логического нуля и тем самым будет снят сигнал сброса с делителя частоты. Состояние 4-разрядного двоичного счетчика (делителя частоты) начнет изменяться. Когда на счетчике накопится значение 8, он выдаст сигнал, поступающий на входы сдвигового регистра и счетчика импульсов сдвига. Так как частота сигналов генератора тактовых импульсов приемника должна совпадать с частотой генератора тактовых импульсов передатчика, то сдвиг (считывание) бита произойдет примерно на середине временного интервала, отведенного на передачу бита данных, т. е. времени, необходимого для выработки шестнадцати тактовых импульсов. Это делается для уменьшения вероятности ошибки из-за возможного различия частот генераторов передатчика и приемника, искажения формы передаваемых сигналов (переходные процессы) и т. п. Следующий сдвиг произойдет после прохождения шестнадцати тактовых импульсов, т. е. на середине временного интервала передачи первого информационного бита.

При приеме в сдвиговый регистр девятого бита кадра (восьмого информационного бита) из него "выдвинется" стартовый бит и, следовательно, в сдвиговом регистре будет размещен весь принятый байт информации. В этот момент счетчик импульсов сдвига придет в нулевое состояние и на его выходе будет выработан единичный сигнал, по которому содержимое сдвигового регистра перепишется в буферный регистр, в регистр состояния А2 запишется 1 и он будет информировать процессор об окончании приема очередного байта, вентиль И подготовится к выработке сигнала "Сброс" (этот сигнал сформируется после прихода первого стопового бита).

Получив сигнал готовности (1 в регистре А2), процессор выполнит команду "Ввод" (см. пример 2.2 Параллельной передачи данных). При этом вырабатывается управляющий сигнал системного интерфейса "Ввод", по которому производятся пересылка принятого байта данных из буферного регистра в процессор (сигнал "Чтение") и сброс регистра состояния А2.

|

|

|

Отметим, что для простоты изложения в контроллере на рис. 14 не показаны схемы контроля стоповых бит принимаемого кадра. Не показаны также схемы контроля четности или нечетности (паритета) передаваемой информации (обычно в передаваемом байте восьмому биту придается значение 0 или 1, так чтобы в этом байте было четное количество единиц). В реальных контроллерах имеются такие схемы, и если контроллер не принимает из линии связи нужного количества стоповых бит или вырабатывается сигнал ошибки паритета в схеме контроля четности, то принятые в текущем кадре биты данных игнорируются и контроллер ожидает поступления нового стартового бита.

Обмен данными с ВУ по последовательным линиям связи широко используется в микроЭВМ, особенно в тех случаях, когда не требуется высокой скорости обмена. Вместе с тем применение в них последовательных линий связи с ВУ обусловлено двумя важными причинами. Во-первых, последовательные линии связи просты по своей организации: два провода при симплексной и полудуплексной передаче и максимум четыре - при дуплексной. Во-вторых, в микроЭВМ используются внешние устройства, обмен с которыми необходимо вести в последовательном коде.

В современных микроЭВМ применяют, как правило, универсальные контроллеры для последовательного ВВ, обеспечивающие как синхронный, так и асинхронный режим обмена данными с ВУ.

40.Микроконтроллеры их назначение области применения и перспективы развития как оба они позволяют получать исходный код.

Постановка задачи

Результатом данного проектирования должен явиться программный продукт контроллера, обеспечивающий данными вычислитель о скорости летательного аппарата. Система должна обеспечивать считывание с датчиков и обработку данных, используя следующий набор операций: считывание, обработка, формирование слов, выдача на ЦАП приборной скорости.

Входными данными служат:

счтанные данные с маски приборной скорости;

|

|

|

счтанные данные с маски максимальной скорости;

Выходными формами служат:

слово 206 в соответствии с РТМ;

слово 207 в соответствии с РТМ;

слово 271 в соответствии с РТМ;

данные с ЦАП приборной скорости.

Кроме того, система должна включать в себя следующие подсистемы:

контроль программного обеспечения;

контроль о выходе из строя маски приборной скорости;

контроль о выходе из строя маски максимальной скорости;

контроль о превышении скорости более чем на 2 км/ч, сигнализируя о перегрузки;

частота обновления минимальная 31 мсек по каждому значению и максимальная 60 мсек по каждому значению.

Цена младшего разряда по 206 и 207 слову 0,11575

В качестве базового языка программирования использовать

язык С-51 совместно с Assembler 8051.

Выводы

В настоящем разделе выпускной работы были проведены следующие работы:

- анализ автоматизированных контроллеров, и микропроцессоров, на основе чего произведена их классификация;

- рассмотрена и проанализирована проблема выбора инструментальных средств для разработки контроллера, на основании чего выбраны языки С-51 и Assembler;

- на основании анализа требуемого к контроллера было сформулирована задача и требования к комплексу программ деятельности контроллера.

Обобщенная структура и алгоритм функционирования контроллера

Данные в системе представляют собой информацию в виде переменных, которым жестко заданы адреса переменных для обмена между программами обслуживания контроллера.

Выбор инструментальных средств и элементной базы.

При выборе элементной базы прибора контроля учитывались следующие обстоятельства:

- построить разрабатываемую технику на современном уровне (по функциям, стоимости, энергопотреблению и габаритам) исключительно на отечественных элементах не представляется возможным;

- так как мощность, потребляемая МК, в значительной мере определяет возможности разработки экономичной аппаратуры, применения кабелей питания небольшого сечения и должна быть выбрана микро мощная элементная база. Часть схемы контроллера может быть выполнена на элементной базе с небольшим быстродействием, однако для другой части схемы должны быть применены микро мощные элементы с высоким быстродействием. Одним из, таким элементом является микроконтроллер Intel 87C51FB.

Применяемый в разработке микроконтроллер Intel 87C51FB обладает следующими основными характеристиками, которые необходимо знать для выполнения поставленной в дипломном проекте задаче.

Intel87C51FB относится к семейству n-МОП технологии и выпускается в корпусе БИС, имеющем 40 внешних выводов. Цоколевка корпуса и наименования выводов показаны на рис 3.1. Для работы Intel87C51FB требуется один источник электропитания +5 В. Через четыре программируемых порта ввода/вывода Intel87C51FB взаимодействует со средой в стандарте ТТЛ-схем с тремя состояниями выхода. Корпус Intel87C51FB имеет два вывода для подключения кварцевого резонатора, четыре вывода для сигналов, управляющих режимом работы МК, и восемь линий порта 3, которые могут быть запрограммированы пользователем на выполнение специализированных (альтернативных) функций обмена информацией со средой.

Рис 3.1.

Разработки на базе контроллеров Intel87C51FB поддерживается ассемблером, программным симулятором, внутрисхемным эмулятором фирмы Phyton и программатором.

Серия Intel87C51FB подходит для широкого спектра приложений от схем высокоскоростного управления автомобильными и электрическими двигателями до экономичных удаленных приемопередатчиков, показывающих приборов и связных процессоров. Наличие ПЗУ позволяет подстраивать параметры в прикладных программах (коды передатчика, скорости двигателя, частоты приемника и т.д.).

Малые размеры корпусов, как для обычного, так и для поверхностного монтажа, делает эту серию микроконтроллеров пригодной для портативных приложений. Низкая цена, экономичность, быстродействие, простота использования и гибкость ввода/вывода делает Intel87C51FB привлекательным даже в тех областях, где ранее не применялись микроконтроллеры. Например, таймеры, замена жесткой логики в больших системах, сопроцессоры.

Приведем краткий обзор характеристик МК:

- 111 базовых команд;

- Большинство команд (94) имеют формат один или два байта и выполняются за один или два машинных цикла;

- рабочая частота 12 МГц

- -байтное АЛУ и схемы аппаратурной реализации команд умножения и деления;

- 14 - битовые команды;

- двунаправленная 8-битная шина;

- стираемое программируемое ПЗУ программ емкостью 64 Кбайт;

- ОЗУ данных емкостью 128 байта;

- два 16-битных таймера/счетчика;

- программируемые схемы ввода/вывода (32 линий);

- блок двухуровневого векторного прерывания от пяти источников;

- асинхронный канал дуплексного последовательного ввода/вывода информации со скоростью до 375 Кбит/с;

- генератор, схему синхронизации и управления;

- 8 х 4 регистров общего использования;

- 128 программно-управляемых флагов;

- прямая, косвенная и относительная адресация данных и команд;

- четыре источника прерывания:

Структурная схема микропроцессора

Рассмотрим структурную схему микроконтроллера Intel87C51FB рисунок 3.2.

Рис 3.2.

Основу структурной схемы образует внутренняя двунаправленная 8-битная шина, которая связывает между собой все основные узлы и устройства: резидентную память, АЛУ, блок регистров специальных функций, устройство управления и порты ввода/вывода. Рассмотрим основные элементы структуры и особенности организации вычислительного процесса.

Арифметическо-логическое устройство

8-битное АЛУ может выполнять арифметические операции сложения, вычитания, умножения и деления; логические операции И, ИЛИ, исключающее ИЛИ, а также операции циклического сдвига, сброса, инвертирования и т.п. В АЛУ имеются программно недоступные регистры T1 и T2, предназначенные для временного хранения операндов, схема десятичной коррекции и схема формирования признаков.

Простейшая операция сложения используется в АЛУ для инкрементирования содержимого регистров, продвижения регистра-указателя данных и автоматического вычисления следующего адреса РПП. Простейшая операция вычитания используется в АЛУ для декрементирования регистров и сравнения переменных.

Простейшие операции автоматически образуют "тандемы" для выполнения в АЛУ таких операций, как, например, инкрементирование 16-битных регистровых пар. В АЛУ реализуется механизм каскадного выполнения простейших операций для реализации сложных команд. Так, например, при выполнении одной из команд условной передачи правления по результату сравнения в АЛУ трижды инкрементируется СК, дважды производится чтение из РПД, выполняется арифметическое сравнение двух переменных, формируется 16-битный адрес перехода и принимается решение о том, делать или не делать переход по программе. Все перечисленные операции выполняются в АЛУ всего лишь за 2 мкс.

Важной особенностью АЛУ является его способность оперировать не только байтами, но и битами. Отдельные программно-доступные биты могут быть установлены, сброшены, инвертированы, переданы, проверены и использованы в логических операциях. Эта способность АЛУ, оперировать битами, столь важна, что во многих описаниях Intel87C51FB говорится о наличии в нем "булевского процессора". Для управления объектами часто применяются алгоритмы, содержащие операции над входными и выходными булевскими переменными (истина/ложь), реализация которых средствами обычных микропроцессоров сопряжена с определенными трудностями.

Таким образом, АЛУ может оперировать четырьмя типами информационных объектов: булевскими (1 бит), цифровыми (4 бита), байтными (8 бит) и адресными (16 бит). В АЛУ выполняется 51 различная операция пересылки или преобразования этих данных. Так как используется 11 режимов адресации (7 для данных и 4 для адресов), то путем комбинирования "операция/ режим адресации" базовое число команд 111 расширяется до 255 из 256 возможных при однобайтном коде операции.

Резидентная память

Память программ и память данных, размещенные на кристалле физически и логически разделены, имеют различные механизмы адресации, работают под управлением различных сигналов и выполняют разные функции.

Память программ (ПЗУ или СППЗУ) имеет емкость 64 Кбайта и предназначена для хранения команд, констант, управляющих слов инициализации, таблиц перекодировки входных и выходных сменных и т.п. РПП имеет 16-битную шину адреса, через которую обеспечивается доступ из счетчика команд или из регистра-указателя данных. Последний выполняет функции базового регистра при косвенных переходах по программе или используется в командах, оперирующих с таблицами.

Память данных (ОЗУ) предназначена для хранения переменных в процессе выполнения прикладной программы, адресуется одним байтом и имеет емкость 128 байт. Кроме того, к адресному пространству РПД примыкают адреса регистров специальных функций (РСФ), которые перечислены в табл. 3.1.

Память программ, так же как и память данных, может быть расширена путем подключения внешних БИС.

Аккумулятор и ССП. Аккумулятор является источником операнда и местом фиксации результата при выполнении арифметических, логических операций и ряда операций передачи данных. Кроме того, только с использованием аккумулятора могут быть выполнены операции сдвигов, проверка на нуль, формирование флага паритета и т.п.

Таблица 3.1.

41.Многопроцессорные и многомашинные системы.

4.1. Концепция комплексирования однопроцессорных ЭВМ

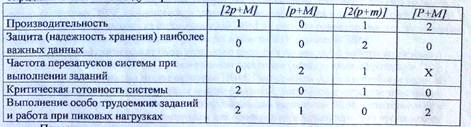

В основе этой концепции лежит сравнительная оценка возможностей однопроцессорных ЭВМ, многомашинных и многопроцессорных систем. Рассмотрим некоторую стандартную однопроцессорную ЭВМ, которую обозначим через [р+т]9 где р и т - ее стандартные процессор и оперативная память соответственно. Пусть теперь Р -процессор с удвоенной производительностью по сравнению с р, а Л/- оперативная память с удвоенными емкостью и пропускной способностью каналов по сравнению с т. Рассмотрим, кроме стандартной ЭВМ, однопроцессорную ЭВМ со стандартным процессором р и удвоенной памятью М и однопроцессорную ЭВМ с процессором удвоенной производительности Р и удвоенной памятью А/, которые обозначим через [р+М] и [Р+М] соответственно. Наконец, рассмотрим совокупность двух стандартных ЭВМ, которую обозначим через [2(р+т)], и/двухпроцессорную систему, состоящую из двух стандартных процессоров р и общей для них оперативной памяти удвоенной емкости А/, которую обозначим через [2р+М].

Результаты сравнительной оценки четырех последних системных структур приведены в таблице 4.1. В этой таблице использованы следующие условные обозначения для качества системных структур по указанным в таблице критериям:

• 0 - обычные возможности,

• 1 - улучшенные возможности,

• 2 - самые лучшие возможности;

Которые обеспечиваются рассматриваемыми структурами (оценки 0, 1 и 2 не содержат смыслового значения конкретных чисел). Из данных таблицы видно, что двухпроцессорная конфигурация [2р + М] обладает некоторыми преимуществами в определенных областях, однако надо иметь в виду, что ер производительность не достигает удвоенной производительности конфигурации [р+т],т. е. производительности конфигурации [Р+Л4]. Следует отметить, что двухпроцессорная конфигурация с общей памятью [2р I М} равноценна другим конфигурациям или превосходит их по критериям критической готовности, выполнения особо трудоемких заданий и работы в условиях кратковременных перегрузок, т. е. при пиковых нагрузках. Недостаток этой конфигурации по критерию частоты перезапуска системы является следствием повышенной сложности ее операционной системы и других управляющих механизмов, что может приводить к необходимости относительно более частых перезапусков, Наконец, меньшая надежность хранения данных в такой конфигурации по сравнению с парой продублированных машин

Приведенные качественные сравнительные оценки относятся к таким системам, для которых не ставится цель достижения сверхвысокопроизводительной обработки информации. В последнем случае, начиная с некоторого уровня производительности, обработку могут обеспечить только те или иные параллельные системы.

В современных однопроцессорных ЭВМ могут предусматриваться четыре уровня комплексирования:

• на уровне процессоров для синхронизации и управления,

• на уровне каналов ввода-вывода при помощи адаптеров,

• на уровне оперативной памяти (за счет возможностей много входовой памяти),

• на уровне внешней памяти.

При этом может допускаться любая или некоторые комбинации уровней комплексирования. При комплексировании на уровне оперативной памяти основной является двухпроцессорная конфигурация, хотя возможны конфигурации с большим числом процессоров.

Исторически первыми были созданы однопроцессорные системы, хотя идеи параллелизма обработки информации возникли практически одновременно с идеями построения самих вычислительных машин. Так, еще в середине прошлого века Ч. Бэббидж отмечал возможность совмещения длинных серий идентичных вычислений.

4.2. Многомашинные комплексы

Многомашинный вычислительный комплекс (ММВК) - комплекс, включающий в себя две или более ЭВМ (каждая из которых имеет процессор, ОЗУ, набор периферийных устройств и работает под управлением собственной операционной системы), связи между которыми обеспечивают выполнение функций, возложенных на комплекс.

Цели, которые ставятся при объединении ЭВМ в комплекс, могут быть различными, и они определяют характер связей между ЭВМ. Чаще всего основной целью создания ММВК является или увеличение производительности, или повышение надежности, или одновременно и то и другое. Однако при достижении одних и тех же целей связи между ЭВМ могут существенно различаться.

По характеру связей между ЭВМ комплексы можно разделить на три типа:

• косвенно-, или слабосвязанные;

• прямосвязанные;

• сателлитные.

В косвенно-, иди слабосвязанных, комплексах ЭВМ связаны друг с другом только через внешние запоминающие устройства (ВЗУ). Для обеспечения таких связей используются устройства управления ВЗУ с двумя и более входами. В косвенно-связанных комплексах связь между ЭВМ осуществляется только на информационном уровне. Обмен информацией осуществляется в основном по принципу «почтового ящика», т.е. каждая из ЭВМ помещает в общую внешнюю память информацию, руководствуясь собственной программой, и соответственно другая ЭВМ принимает эту информацию, исходя из своих потребностей. Такая организация связей обычно используется в тех случаях, когда ставится задача повысить надежность комплекса путем резервирования ЭВМ. В этом случае ЭВМ, являющаяся основной, решает заданные задачи, выдает результаты и постоянно оставляет в общем ВЗУ всю информацию, необходимую для продолжения решения с любого момента времени. Вторая ЭВМ, являющаяся резервной, может находиться в состоянии ожидания, с тем чтобы в случае выхода из строя основной ЭВМ по сигналу оператора начать выполнение функций, используя информацию хранимую в общем ВЗУ основной ЭВМ.

При такой связи может быть несколько способов организации работы комплекса.

1. Резервная ЭВМ находится в выключенном состоянии (ненагруженный резерв) и включается только при отказе основной ЭВМ. Естественно, для того чтобы резервная ЭВМ начала выдавать результаты вместо основной, потребуется определенное время, которое определяется временем, необходимым для включения ЭВМ, вхождением ее в режим, а также временем, отводимым для проверки ее исправности. Это время может быть достаточно большим. Такая организация возможна, когда система, в которой работает ЭВМ, не критична по отношению к некоторым перерывам или остановкам в процессе решения задач. Это обычно имеет место в случаях, когда ЭВМ не выдает управляющую информацию.

2. Резервная ЭВМ находится в состоянии полной готовности и в любой момент может заменить основную ЭВМ (нагруженный резерв», причем либо не решает никаких задач, либо работает в режиме самоконтроля, решая контрольные задачи. В этом случае переход в работе от основной к резервной ЭВМ может осуществляться достаточно быстро, практически без перерыва в выдаче результатов. Однако следует заметить, что основная ЭВМ обновляет в общем ВЗУ информацию, необходимую для продолжения решения, не непрерывно, а с определенной дискретностью, поэтому резервная ЭВМ начинает решать задачи, возвращаясь на некоторое время назад. Такая организация допустима и в тех случаях, когда ЭВМ работает непосредственно в контуре управления, а управляемый процесс достаточно медленный и возврат во времени не оказывает заметного влияния. При организации работы по первому и второму вариантам ЭВМ используются нерационально: одна ЭВМ всегда простаивает. Простоев можно избежать, загружая ЭВМ решением каких-то вспомогательных задач, не имеющих отношения к основному процессу. Это повышает эффективность системы - производительность практически удваивается. 3. Для того чтобы полностью исключить перерыв в выдаче результатов, обе ЭВМ, и

основная и резервная, решают одновременно одни и те же задачи, но результаты выдает только основная ЭВМ, а в случае выхода ее из строя результаты начинает выдавать резервная ЭВМ. При этом общее ВЗУ используется только для взаимного контроля. Иногда такой комплекс дополняется устройством для сравнения результатов с целью контроля. Если при этом используются три ЭВМ, то возможно применение метода голосования, когда окончательный результат выдается только при совпадении результатов решения задачи не менее чем от двух ЭВМ. Это повышает и надежность комплекса в целом, и достоверность выдаваемых результатов. Разумеется, в этом варианте высокая надежность и оперативность достигается весьма высокой ценой -увеличением стоимости системы.

Следует обратить внимание, что при любой организации работы в слабосвязанном ММВК переключение ЭВМ осуществляется либо по командам оператора, либо с помощью дополнительных средств, осуществляющих контроль исправности ЭВМ и вырабатывающих необходимые сигналы. Кроме того, быстрый переход в работе с основной на резервную ЭВМ возможен лишь при низкой эффективности использования оборудования.

Существенно большей гибкостью обладают прямосвязанные ММВК. В прямо связанных комплексах существуют три вида связей:

• общее ОЗУ (ООЗУ);

• прямое управление, иначе связь процессор - процессор;

• адаптер канал - канал (АКК).

Связь через общее ОЗУ гораздо сильнее связи через ВЗУ. Хотя первая связь также носит характер информационной связи и обмен информацией осуществляется по принципу «почтового ящика», однако, вследствие того что процессоры имеют прямой доступ к ОЗУ, все процессы в системе могут протекать с существенно большей скоростью, а разрывы в -выдаче результатов при переходах с основной ЭВМ на резервную сокращаются до минимума. Недостаток связи, через общее ОЗУ заключается в том, что при выходе из строя ОЗУ, которое является сложным электронным устройством, нарушается работа всей системы. Чтобы этого избежать, приходится строить общее ОЗУ из нескольких модулей и резервировать информацию. Это, в свою очередь, приводит к усложнению организации вычислительного процесса в комплексе и в конечном счете к усложнению операционных систем. Следует отметить также и то, что связи через общее ОЗУ существенно дороже, чем через ВЗУ.

Непосредственная связь между процессорами, канал прямого управления, может быть не только информационной, но и командной, т. е. по каналу прямого управления один процессор может непосредственно управлять действиями другого процессора. Это, естественно, улучшает динамику перехода от основной ЭВМ к резервной, позволяет осуществлять более полный взаимный контроль ЭВМ. Вместе с тем передача сколько-нибудь значительных объемов информации по каналу прямого управления нецелесообразна, так как в этом случае решение задач прекращается: процессоры ведут обмен информацией.

Связь через адаптер канал - канал в значительной степени устраняет недостатки связи через общее ОЗУ ивместе с тем почти не уменьшает возможностей по обмену информацией между ЭВМ по сравнению с общим ОЗУ. Сущность этого способа связи заключается в том, что связываются между собой каналы двух ЭВМ с помощью специального устройства -адаптера. Обычно это устройство подключается к селекторным каналам ЭВМ. Такое подключение адаптера обеспечивает достаточно быстрый обмен информацией между ЭВМ, при этом обмен может производиться большими массивами информации. В отношении скорости передачи информации связь через АКК мало уступает связи через общее ОЗУ, а в отношении объема передаваемой информации - связи через общее ВЗУ. Функции АКК достаточно просты: это устройство должно обеспечивать взаимную синхронизацию работы двух ЭВМ и буферизацию информации при ее передаче, однако большое разнообразие режимов работы двух ЭВМ и необходимость реализации этих режимов существенно усложняет устройство АКК.

|

|

|

|

|

Дата добавления: 2015-04-23; Просмотров: 1678; Нарушение авторских прав?; Мы поможем в написании вашей работы!