КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Триггеры. Теория

|

|

|

|

PRIME

STARAN

CEDAR

LCAP (loosely Coupled Array Processors

Данная система состоит из нескольких машин FPS 164, которые контролируются одной управляющей машиной. В демонстрационных образцах было использовано семь FPS 164, каждая из которых имела по 4 Мбайта основной памяти. Управляющей машиной служила IBM 4381.

Cm*

Основной компонентой этой системы является "вычислительный модуль", состоящий из микропроцессора DEC LSI-11 с 64Мбайтами dynamic MOS memory. Данный модуль может работать как отдельный компьютер. В то же время до 14 таких модулей могут быть подключены к шине (intracluster bus), формируя таким образом сильносвязанную систему (кластер - tightly-coupled cluster). Внутри этого кластера передача данных происходит путем прямого доступа к памяти. Построенные таким образом кластеры можно связать в более сложную систему через две соединяющие кластеры шины (intercluster buses). При этом получается слабо связанная сеть (loosely-coupled network), в которой обмен данными происходит путем коммутации пакетов (packet switching techniques).

В состав системы входит шестнадцать кластеров по восемь процессорных элементов (ПЭ) в каждом. Кластеры связаны через расширенную сеть типа Omega (extended Omega global switching network) с 256 модулями глобальной памяти. Каждый модуль памяти имеет объем от 4 до 16 мегаслов. Процессорные элементы, составляющие кластер, имеют по 16 мегаслов локальной памяти. Все процессорные элементы конвейерного типа и связаны между собой через локальную коммутационную сеть (local switching network).

В ее состав входят четыре матричных модуля, управляемых последовательной машиной PDP-11. Каждый модуль содержит 256 ПЭ и общую память емкостью от 64 Кбит до 64 Мбит. Связь между ПЭ и памятью осуществляется через гибкую коммутационную сеть.

|

|

|

PEPE (Parallel Element Processor Ensemble)

Это система из 288 ПЭ с низкой степенью связности. Каждый процессорный элемент содержит по три процессора (каждый процессор предназначался для выполнения определенной функции, связанной с задачей радиолокации), управляемых в синхронном режиме тремя устройствами управления (по одному на каждый тип процессора в ПЭ). Эти три устройства управления подключались к трем стандартным каналам ввода-вывода машины CDC 7600, которая была главной для всей системы. Связь между ПЭ осуществлялась через блоки памяти устройств управления.

Система состоит из пяти процессоров. Каждый процессор через матричный коммутатор имеет доступ к блокам памяти (количество блоков варьируется от одного и более). Через сеть внешнего доступа процессоры соединяются с памятью на внешних носителях и устройствами ввода--вывода. В каждый момент времени некоторый процессор с памятью работает как управляющий процессор (монитор), регулируя активность остальных рабочих процессоров.

В отличие от комбинационных логических цепей триггеры - это логические устройства с памятью. Их выходные сигналы в общем случае зависят не только от сигналов, приложенных к входам в данный момент времени, но и от сигналов, воздействовавших на них ранее. В зависимости от свойств, числа и назначения входов триггеры можно разделить на несколько видов.

Типы триггеров.

Все современные серии цифровых микросхем, как правило, включают различные типы триггеров, представляющих устройство с двумя устойчивыми состояниями, содержащее бистабильный запоминающий элемент (собственно триггер) и схему управления. Входы, как и сигналы, подаваемые на них делятся на информационные и вспомогательные. Информационные сигналы через соответствующие входы управляют состоянием триггера. Сигналы на вспомогательных входах служат для предварительной установки триггера в заданное состояние и его синхронизации. Вспомогательные входы могут при необходимости выполнить, роль информационных. По способу приема информации триггеры подразделяют тактируемые и нетактируемые триггеры. Изменение состояния нетактируемого (асинхронного) триггера происходит сразу же после соответствующего изменения потенциалов на его управляющих входах. В тактируемом (синхронном) триггере изменение состояния может произойти только в момент присутствия соответствующего сигнала на тактовом входе.

|

|

|

Тактирование может осуществляться импульсом (потенциалом) или фронтом (перепадом потенциала). В первом случае сигналы на управляющих входах оказывают влияние на состояние триггера только при разрешающем потенциале на тактовом входе. Во втором случае воздействие управляющих сигналов проявляется только в момент перехода единица - нуль или нуль - единица на тактовом входе.

Существуют также универсальные триггеры, которые могут работать как в тактируемом, так и в нетактируемом режиме. Основные типы триггеров в интегральном исполнении носят следующие названия: RS-триггеры, D-триггеры, Т-триггеры и JK-триггеры.

Условные обозначения триггеров имеют вид прямоугольников, внутри которых пишется буква Т и к которым слева подводятся входные сигналы, Обозначения входов триггера пишутся на дополнительном поле в левой част и прямоугольника. Тактовый вход обозначается буквой С. Динамические входы, т. е. такие входы, которые оказывают воздействие на триггер только в момент перепада на них потенциала, обозначаются дополнительно косой чертой в месте соединения линии входа с обозначением триггера. При этом черта идет снизу вверх, если последний срабатывает от перепада 0/1, и сверху вниз, если рабочим является перепад 1/0. Принимается, что статические входы могут повлиять на состояние триггера тогда, когда на этих входах присутствует потенциал "единица". Если же устанавливающим по какому-то входу является сигнал "нуль", то этот вход дополнительно обозначается кружком. Выходы триггера показываются с правой стороны прямоугольника, причем инверсный выход также обозначается кружком.

RS-триггер.

Асинхронный триггер RS-типа (рис 1) имеет два информационных входа R и S. Входы S и R названы по первым буквам английских слов set - установка и reset - сброс. При S=1 и R=0 на выходах триггера появляются сигналы: на прямом выходе Q=1, на инверсном Q =0. При S=0 и R=1 выходные сигналы триггера принимают противоположные состояния (Q=0, Q =1). Этот триггер не имеет тактового входа.

|

|

|

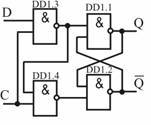

Простейший RS-триггер можно реализовать на логических элементах ИЛИ-НЕ или И-НЕ, как показано на рисунке 1.

Рис. 1.Асинхронный RS-триггер на логических элементах ИЛИ-НЕ и И-НЕ.

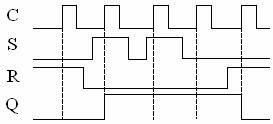

Проиллюстрировать работу такого асинхронного триггера можно с помощью таблиц истинности или временных диаграмм (рис.2). Обратите внимание, что простейший триггер при S=1 и R=0 устанавливается в состояние логического нуля (и наоборот). Здесь Q – состояние выхода до установки входных сигналов (режим хранения).

| На элементах ИЛИ-НЕ | На элементах И-НЕ | ||||||

| Вход S | Вход R | Прям. Q | Инвер. Q | Вход S | Вход R | Прям. Q | Инвер. Q |

| Q | Q | ||||||

| Q | Q |

При одновременном поступлении сигнала 1 или 0 на входы R и S выходные сигналы триггера не определены, поэтому в устройствах на основе RS-триггера необходимо исключать такие режимы (запрещенное состояние). Существуют разновидности RS-триггера, носящие название Е-, R- и S-триггеров, для которых сочетание S=1 и R=1 не является запрещенным.

|

Рис. 2.Синхронный RS-триггер. Справа – его временные диаграммы.

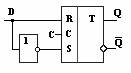

Синхронный одноступенчатый RS-триггер рис. 2 отличается от асинхронного наличием С-входа для синхронизирующих тактовых импульсов. Синхронный триггер состоит из асинхронного RS-триггера и двух логических элементов на его входе.

Переключение этого триггера происходит только при появлении высокого уровня на тактовом входе С, что хорошо видно на временной диаграмме, рис. 2.

Триггер RS используется как устройство памяти в других типах триггеров.

D-триггер.

D-триггер - триггер задержки (от английского delay-задержка), при разрешающем сигнале на тактовом входе C устанавливается в состояние, соответствующее потенциалу на входе D. Если обозначать выходной сигнал триггера буквой Q, то для D – триггера можно написать следующее равенство: Qn=Dn-1. Индексы n и n-1 указывают на то, что выходной сигнал Q изменяется не сразу после изменения входного сигнала D, а только с приходом разрешающего тактового сигнала, т.е. существует задержка.

|

|

|

| Dn | Qn+1 | Qn+1 |

Тактирование D-триггера может осуществляться уровнем или фронтом. Более простым является D-триггер первого типа, который реализуется на основе RS-триггера (рис. 3). Он состоит из синхронного RS-триггера и инвертора. Благодаря инвертору невозможно запрещенное соотношение сигналов на входах S и R.

а)

в)

в)

Рис. 3.D-триггер: а) и б) синхронизируемый уровнем, в) синхронизируемый фронтом.

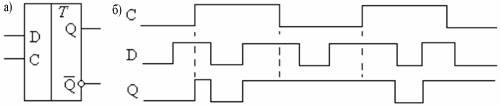

Рис. 4.D-триггер синхронизируемый уровнем (статическое управление). Условное обозначение и временные диаграммы

На анализ работы и временная диаграмма (рис. 4) показывают, что сигнал с входа D проходит на выход Q только при условии высокого уровня на тактовом входе C.

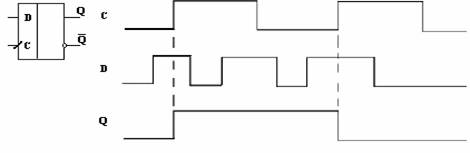

В тактируемом фронтом D-триггере (рис.5) изменение потенциала на входе D, синхронное с тактовыми импульсами, повторяется на выходе Q по перепаду уровня (в данном случае с низкого на высокий) с задержкой относительно тактовых импульсов.

Рис. 5.D-триггер синхронизируемый фронтом (динамическое управление). Условное обозначение и временные диаграммы.

Выходной сигнал Q сохраняется до прихода очередного тактового импульса. При чем эта информация хранится в D-триггере, пока не придет следующий бит (0 или 1) информации. По сути это ячейка памяти.

Если вход D замкнуть с инверсным выходом, то останется только один вход С. При подаче на вход С импульсов триггер переключается в противоположное состояние. Таким образом, триггер осуществляет деление частоты входных импульсов на 2. В таком режиме D-триггер работает счетным или Т-триггером.

JK-триггер

Он имеет также два управляющих входа J и K. Подобно RS-триггеру, в JK-триггере J и K-это входы установки триггера в единицу и нуль. В отличие от RS-триггера в JK-триггере наличие двух единичных управляющих сигналов (J=K=1) приводит к переходу триггера в противоположное состояние, т. е. в данном случае JK-триггер работает как T-триггер. JK-триггеры тактируются только перепадом потенциала на тактовом входе. Находят применение также JK-триггеры, которые изменяют свои состояния под воздействием перепадов сигналов на входах J и K. Уравнение для JK-триггера выглядит следующим образом: Qn=(J Q + K Q)n-1. На рис.6 указаны основные принципы построения и обозначения JK-триггеров.

Рис. 6 Принципы построения (а, в, г) и обозначения (б, д) JK-триггеров.

Практические микросхемы триггеров обычно содержат различные вспомогательные входы. В качестве примера на рис. 6 д показана схема триггера К155ТВ1. Здесь кроме тактируемых входов J и K имеются также нетактируемые инверсные входы S и R. Для того чтобы упростить построение счетчиков, в этих триггерах предусмотрено по три входа J и К, объединенных посредством ячеек И (J=J1J2J3. K=K1K2K3).

В таблице ниже перечислены режимы работы JK-триггера. Напоминаем, что переключение происходит только при поступлении тактового импульса на вход C.

| J | K | Q | Режим работы |

| Q | Хранение | ||

| Установка в 1 | |||

| Сброс в 0 | |||

| Qinv | Счет |

|

|

|

|

|

Дата добавления: 2015-05-09; Просмотров: 901; Нарушение авторских прав?; Мы поможем в написании вашей работы!