КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Счетчики

|

|

|

|

Счетчиком называется узел ЭВМ, предназначенный для подсчета числа входных сигналов. Счетчики используются в ЭВМ для образования последовательностей адресов команд, для подсчета числа циклов выполнения операций и т. п. Счетчики принято подразделять на суммирующие, вычитающие и реверсивные.

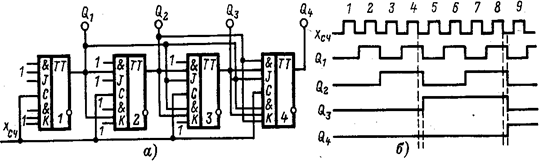

На рис. 2.20 показаны схема несинхронизируемого четырехразрядного двоичного суммирующего счетчика с последовательным переносом и временная диаграмма его работы. Таблица 2.5 показывает состояния, в которых находятся триггеры счетчика при воздействии серии входных сигналов хсч.

Рис. 2.20. Несинхронизируемый двоичный счетчик с последовательным переносом:

а — функциональная схема; 6 — временная диаграмма

Здесь на входы J и К JK-триггеров подаются сигналы 1. Выход каждого предыдущего триггера Q n-1 соединен с входом синхронизации Сn последующего триггера. Каждый JK-триггер в счетчике выполняет функцию несинхронизируемого триггера со счетным входом. По спаду единичного выходного сигнала изменяется состояние триггера младшего разряда счетчика на противоположное (т.е. реализуется сложение по модулю 2 в этом разряде). В последующих разрядах аналогичное действие производит сигнал переноса

Таблица 2.5. Таблица состояний двоичного счетчика

| Хсч | Q4 | Q3 | Q2 | Q1 | Хсч | Q4 | Q3 | Q2 | Q1 |

| о | |||||||||

|

|

|

Обычно счетчик имеет цепь установки в нулевое состояние (сброс триггеров в 0). Однако начальное состояние счетчика необязательно нулевое. Начальное состояние может устанавливаться передачей в счетчик кода некоторого числа, и с него уже будет начинаться операция счета единиц. Такой режим работы счетчика необходим, например, при образовании последовательности адресов команд при заданном исходном адресе. С ростом разрядности счетчика понижается предельная частота его работы. Это объясняется тем, что с ростом разрядности счетчика п будет возрастать задержка поступления сигнала на вход С некоторого j-го разряда относительно времени поступления входного сигнала Хсч на вход С младшего разряда счетчика. Из временной диаграммы видно, что такая задержка может привести к искажению информации в счетчике (моменты времени 4 и 8). Для повышения быстродействия счетчики выполняют с параллельным переносом,

На рис. 2.21 изображена функциональная схема счетчика с параллельным переносом. Отличительной особенностью данной схемы является то, что выходы всех предшествующих разрядов подаются на входы J и К j-го триггера. Длительность переходного процесса в таком счетчике равна длительности переключения одного разряда. Из схемы видно, что с возрастанием порядкового номера триггера увеличивается число входов в элементах И JК-триггеров. А так как число входов J и К и нагрузочная способность выходов триггеров ограничены, то и разрядность счетчика с параллельным переносом невелика и равна обычно четырем. Поэтому при числе разрядов счетчика, большем максимального числа входов J и К, счетчик разбивают на группы и внутри каждой группы строят цепи параллельного переноса

.

Рис. 2.21. Синхронизируемый двоичный счетчик с параллельным переносом:

а—функциональная схема; б—временная диаграмма

Такой подход удобен и потому, что счетчики реализуют в виде интегральной микросхемы в отдельном корпусе. В этом случае при последовательном переносе просто осуществляется увеличение разрядности счетчика.

|

|

|

Вычитающие счетчики и реверсивные (настраиваемые на суммирование или вычитание) строятся аналогичным образом.

|

|

|

|

|

Дата добавления: 2015-05-09; Просмотров: 647; Нарушение авторских прав?; Мы поможем в написании вашей работы!