КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Электрические параметры цифровых ИМС

|

|

|

|

Основные электрические параметры логических микросхем определяют возможность совместной работы ИМС разных серий в составе аппаратуры. К таким параметрам отно-сятся: быстродействие, потребляемая от источника питания мощность РПОТ, помехоус-тойчивость UПОМ, коэффициент разветвления по выходу (нагрузочная способность) КРАЗ; коэффициент объединения по входу КОБ.

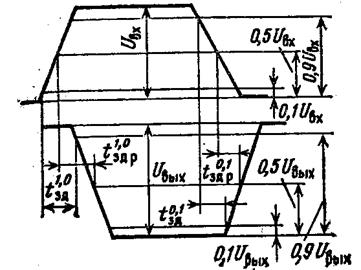

Быстродействие определяется динамическими параметрами цифровых ИМС:

t 0,1 – время перехода от логического уровня «1» к логическому уровню «0»;

t1,0 – время перехода от логического уровня «0» к логическому уровню «1»;

tЗД1,0 – время задержки включения;

tЗДР0,1 – время задержки выключения;

tЗДР1,0 – время задержки распространения при включении;

tЗДР0,1 – время задержки распространения при выключении;

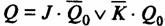

tЗДР СР = 0,5(tЗДР1,0 + tЗДР0,1) – среднее время задержки распространения сигнала.

На рисунке 4.9 показаны уровни отсчёта, относительно которых определяются перечисленные выше динамические параметры

Рисунок 4.9 – Уровни отсчёта, относительно которых определяются

динамические параметры цифровых микросхем

Потребляемая от источника питания мощность различна для состояний «1» и «0»:

Р0ПОТ – мощность, потребляемая микросхемой в состоянии «0».

Р1ПОТ – мощность, потребляемая микросхемой в состоянии «1».

В динамическом режиме, то есть в режиме переключений, потребляемая от источника питания мощность увеличивается. У некоторых ИМС, например ТТЛ, она увеличивается незначительно и определяется по выражению:

РПОТ СР = (Р0ПОТ + Р1ПОТ).

У микросхем КМОП эта мощность значительно увеличивается в динамическом режиме и поэтому определяется на максимальной частоте переключений.

Помехоустойчивость определяется уровнями входного сигнала, которое не вызывает ложного срабатывания. Различают статическую и динамическую помехоустойчивость.

Статическая помехоустойчивость определяется низким U0ПОМ и высоким U1ПОМ уровнями помехи по предельным передаточным характеристикам, снятым при

различных температурах (см. рисунок 4.10).

U1ПОМ определяется как разность минимального напряжения высокого уровня U1 вх min и напряжения в точке перегиба верхней кривой (точка В). Параметр U0ПОМ определяется как разность напряжений в точке перегиба нижней кривой (точка А) и максимального напряжения низкого уровня U0 вхmax.

Динамическая помехоустойчивость зависит от длительности, амплитуды и формы сигнала помехи, а также от запаса статической помехоустойчивости и скорости переключения ЛЭ.

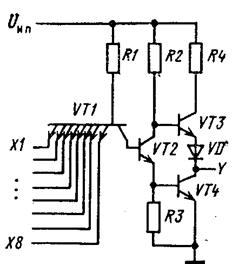

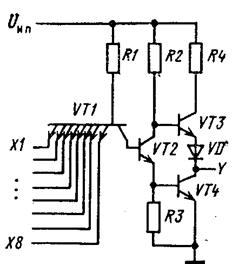

Рисунок 4.10 – Предельные пере- Рисунок 4.11 – Схема 8-входового

даточные характеристики ЛЭ НЕ, логического ТТЛ элемента И-НЕ

полученные при различных (с коэффициентом объединения

температурах по входу КОБ = 8)

Коэффициент разветвления по выходу (нагрузочная способность) КРАЗ определяется как число входов аналогичных элементов, которое может быть подключено к выходу данного ЛЭ без нарушения его работоспособности.

Коэффициент объединения по входу КОБ определяется как максимальное число входов ИМС. На рисунке 4.11 приведена схема ЛЭ И-НЕ с КОБ = 8.

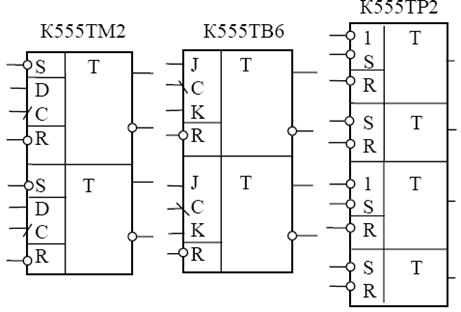

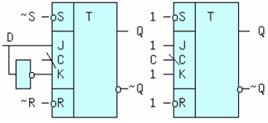

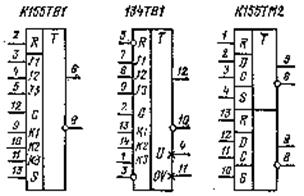

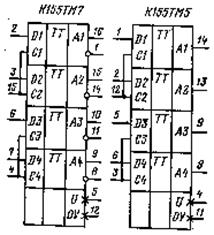

Рисунок 4.1 – Интегральные микросхемы широкого применения 555-й серии: К555ТМ2 – два синхронизируемых по фронту D – триггеров в одном корпусе с раздельными инверсными входами установки R и S; К555ТВ6 - два синхронизируемых по срезу JK – триггеров в одном корпусе с раздельными инверсными входами установки R и S; К555ТР2 - четыре асинхронных RS – триггера с инверсными входами в одном корпусе, два из которых имеют по два входа НЕ-S, объединённых по ИЛИ

в

в

г

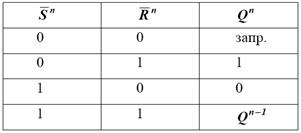

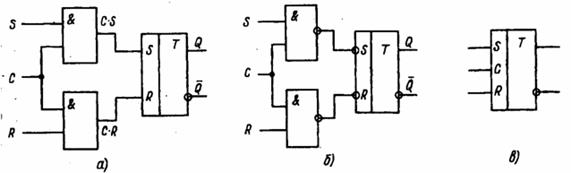

Рисунок 4.2 – Асинхронный RS – триггер с прямыми потенциальными входами:

а) логическая схема; б) условное графическое обозначение; в)таблица переходов

г) логическое выражение функционирования

в

в

г)

Рисунок 4.3 - Асинхронный RS – триггер с инверсными потенциальными входами:

а) логическая схема; б) условное графическое обозначение; в) таблица переходов

г) логическое выражение функционирования

г)

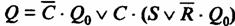

Рисунок 4.4 – Синхронный RS – триггер со статическим управлением: а) на основе

статического RS - триггера с прямыми входами; на основе статического RS - триггера

с инверсными входами; в) УГО; г) логическое выражение функционирования

д)

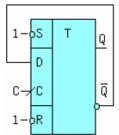

Рисунок 4.5 – Синхронный D – триггер со статическим управлением: а) таблица функционирования; б) на основе статического RS - триггера с прямыми входами; в) на основе статического RS - триггера с инверсными входами; г) УГО; д) логическое выражение функционирования

д)

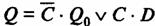

Рисунок 4.6 – JK –триггер: а) логическая схема на двух синхронных RS – триггерах; б) упрощённая логическая схема; в) УГО; д) логическое выражение функционирования

а б а б

а б а б

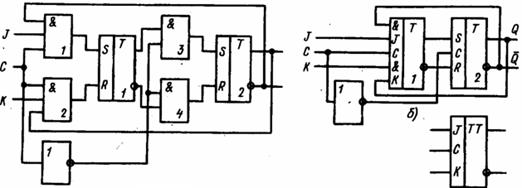

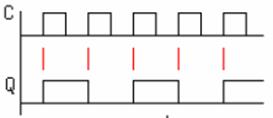

Рисунок 4.7 – Преобразование Рисунок 4.8 – Преобразование D-триггера в

JK –триггера: а) в D-триггер; Т – триггер (а); графики работы Т – триггера (б)

б) в Т – триггер

ЭКСПЛУАТАЦИОННЫЕ ЭЛЕКТРИЧЕСКИЕ ПАРАМЕТРЫ ИМС ТТЛ

Рисунок 4.9 – Уровни отсчёта, относитель- Рисунок 4.10 – Схема 8-входового

но которых определяются динамические логического ТТЛ элемента И-НЕ

параметры цифровых микросхем (КОБ = 8)

t 0,1 – время перехода от логического уровня «1» к логическому уровню «0»;

t1,0 – время перехода от логического уровня «0» к логическому уровню «1»;

tЗД1,0 – время задержки включения;

tЗД0,1 – время задержки выключения;

tЗДР1,0 – время задержки распространения при включении;

tЗДР0,1 – время задержки распространения при выключении;

tЗДР СР = 0,5(tЗДР1,0 + tЗДР0,1) – среднее время задержки распространения сигнала.

Р0ПОТ – мощность, потребляемая микросхемой в состоянии «0»;

Р1ПОТ – мощность, потребляемая микросхемой в состоянии «1»;

РПОТ СР = (Р0ПОТ + Р1ПОТ) – мощность, потребляемая ИМС ТТЛ в динамическом режиме.

КРАЗ – коэффициент разветвления по выходу (нагрузочная способность) – число входов аналогичных элементов, которое может быть подключено к выходу данного ЛЭ без нарушения его работоспособности.

КОБ – коэффициент объединения по входу – максимальное число входов ИМС

Рисунок 4.11 – Условные графические обозначения ИМС триггеров

ПРАКТИЧЕСКАЯ РАБОТА № 7

Цель: Получить и отработать навыки пользования справочными материалами,

синтеза принципиальных схем цифровых устройств на ИМС и их анализа

Задание. Разработать принципиальные схемы RS-триггеров с прямыми и

инверсными входами и проанализировать их работу.

Указания и рекомендации по выполнению работы.

1. Используя справочные материалы, выбрать ИМС логических элементов

И-НЕ, ИЛИ-НЕ, занести в отчёт УГО выбранных ИМС с номерами их выводов.

2. Занести в отчёт параметры выбранных микросхем и объяснить их смысл.

3. Составить принципиальные схемы триггеров, соединив логические выводы

ИМС в соответствии с логической схемой.

4. Показать подключение ИМС к источнику питания.

4. Проанализировать работу триггеров и составить таблицы функционирования.

Содержание отчёта: Тема, цель, УГО выбранных ИМС и их параметры, разра-

ботанные принципиальные схемы триггеров с прямыми и инверсными входами, составленные на основе ИМС И-НЕ и ИЛИ-НЕ с указанием поданного питания.

Литература.

1. Конспект лекций по микросхемотехнике.

2. Мизерная З.А.Цифровая схемотехника: Метод. пособие –М.: Маршрут, 2003.

3 Мизерная З.А. Цифровые устройства. Микропроцессоры и их программи-

рование: Учебное пособие. Альбом схем. – М.: Маршрут, 2002.

6 Калабеков Б.А. Цифровые устройства и микропроцессорные устройства –М.:

Горячая линия - Телеком2002

7 Цифровые и аналоговые интегральные микросхемы: Справочник.

Под ред. С.В. Якубовского. – М.: Радио и связь, 1989.

ПР 7 Разработка и анализ принципиальных схем RS-триггеров

ПРАКТИЧЕСКАЯ РАБОТА № 8

Цель: Получить и отработать навыки использования справочных материалов,

синтеза принципиальных схем цифровых устройств на ИМС и их анализа

Задание. Разработать принципиальные схемы синхронных RS-триггеров на

основе асинхронных RS-триггеров с прямыми и инверсными входами и про-анализировать их работу.

Указания и рекомендации по выполнению работы.

1. Используя конспект, начертить логические схемы синхронных RS-триггеров.

2. Используя приводимые ниже УГО, выбрать ИМС логических элементов

И-НЕ, ИЛИ-НЕ и занести в отчёт их УГО с номерами логических выводов.

3. Составить принципиальные схемы синхронных RS-триггеров, соединив

логические выводы ИМС в соответствии с логической схемой.

Допускается использование результатов, полученных на предыдущей

практической работе.

4. Показать подключение ИМС к источнику питания, учитывая что для ИМС в

корпусе с 14 (16) выводами вывод 7 (8) – ОV (общий); 14 (16) – UИП (+5В);

5. Проанализировать работу триггеров и составить таблицы функционирования.

Содержание отчёта: Тема, цель, две логические схемы синхронных RS-триггеров;

УГО выбранных ИМС; две принципиальные схемы синхронных RS-триггеров, раз-

работанные на основе асинхронных RS-триггеров с прямыми и инверсными входами

и составленные из ИМС логических элементов И-НЕ и ИЛИ-НЕ с указанием подан-

ного питания; таблицы функционирования синхронных RS-триггеров.

Литература.

1. Конспект лекций по микросхемотехнике.

2. Мизерная З.А. Цифровые устройства. Микропроцессоры и их программи-

рование: Учебное пособие. Альбом схем. – М.: Маршрут, 2002.

3. Цифровые и аналоговые интегральные микросхемы: Справочник.

Под ред. С.В. Якубовского. – М.: Радио и связь, 1989.

ПР 8 Разработка и анализ принципиальных схем синхронных RS-триггеров

ПРАКТИЧЕСКАЯ РАБОТА № 9

Цель: Получить и отработать навыки использования справочных материалов,

синтеза принципиальных схем цифровых устройств на ИМС и их анализа.

Задание. Разработать принципиальные схемы синхронных Т- и D-триггеров

на основе асинхронных RS-триггеров и проанализировать их работу.

Указания и рекомендации по выполнению работы.

1. Используя конспект, начертить логические схемы синхронных Т- и D-триггеров.

2. Используя приводимые ниже УГО, выбрать ИМС логических элементов

И-НЕ, ИЛИ-НЕ и занести в отчёт их УГО с номерами логических выводов.

3. Составить принципиальные схемы синхронных Т- и D-триггеров, соединив

логические выводы ИМС в соответствии с логическими схемами.

Допускается использование результатов, полученных на предыдущих

практических работах.

4. Показать подключение ИМС к источнику питания, учитывая что для ИМС в

корпусе с 14 (16) выводами вывод 7 (8) – ОV (общий); 14 (16) – UИП (+5В);

5. Проанализировать работу триггеров и составить таблицы функционирования.

Содержание отчёта: Тема, цель, две логические схемы синхронных D-триггеров и логическая схема Т-триггера; две принципиальные схемы синхронных D-триггеров и принципиальная схема Т-триггера, разработанные на основе синхронных RS-триггеров с указанием поданного питания; таблицы функционирования Т- и D-триггеров.

Литература.

1. Конспект лекций по микросхемотехнике.

2. Мизерная З.А. Цифровые устройства. Микропроцессоры и их программи-

рование: Учебное пособие. Альбом схем. – М.: Маршрут, 2002.

3. Цифровые и аналоговые интегральные микросхемы: Справочник.

Под ред. С.В. Якубовского. – М.: Радио и связь, 1989.

ПР 9 Разработка и анализ принципиальных схем синхронных Т- и D-триггеров

|

|

|

|

|

Дата добавления: 2015-06-27; Просмотров: 2309; Нарушение авторских прав?; Мы поможем в написании вашей работы!