КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Структура логической памяти ПК

|

|

|

|

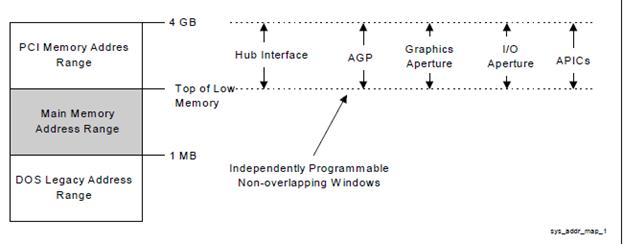

Для ПК характерно стандартное распределение непосредственно адресуемой памяти между ОЗУ, ПЗУ и функционально ориентированной информацией. (рис. 1)

Основная память в соответствии с методами доступа и адресации делится на отдельные, иногда частично или полностью перекрывающие друг друга области, имеющие общепринятые названия. В частности, укрупнено логическая структура основной памяти ПК общей емкостью, например, 16 Мбайт представлена на рисунке 1.

| Стандартная память 640 Кбайт | Верхняя память 384 Кбайт | ||

| 64 Кбайта Область служебных программ и данных ОС | 576 Кбайт Область программ и данных пользователя | 256 Кбайт Область видеопамяти дисплея и служебных программ | 128 Кбайт Область программ начальной загрузки ОС и др. |

| ОЗУ | ПЗУ | ||

Рис. 1. Распределение 1-Мбайтной области ОП

| Непосредственно адресуемая память | Расширенная память | ||

| Стандартная (обычная) память (СМА) | Верхняя память (блоки UMA) | Высокая память (HMA) | |

| 640 Кбайт | 384 Кбайта | 64 Кбайта |

Рис. 2. Логическая структура основной памяти

Прежде всего основная память компьютера делится на две логические области: непосредственно адресуемая память, занимающую первые 1024 Кбайта ячеек с адресами от 0 до 1024 Кбайт - 1, и расширенную память, доступ к ячейкам которой возможен при использовании специальных программ-драйверов.

Драйвер - специальная программа, управляющая работой памяти или внешним устройством ЭВМ и организующая обмен информацией между МП, ОП и внешними устройствами ЭВМ.

Стандартной памятью (CMA - Conventional Memory Area) называется непосредственно адресуемая память в диапазоне от 0 до 640 Кбайт.

Непосредственно адресуемая память в диапазоне адресов от 640 до 1024 Кбайт называется верхней памятью (UMA - Upper Memory Area). Верхняя память зарезервирована для памяти дисплея (видеопамяти) и постоянного запоминающего устройства. Однако обычно в ней остаются свободные участки - "окна", которые могут быть использованы при помощи диспетчера памяти в качестве оперативной памяти общего назначения.

Расширенная память - это память с адресами 1024 Кбайта и выше.

Непосредственный доступ к этой памяти возможен только в защищенном режиме работы микропроцессора.

|

|

|

В реальном режиме имеются два способа доступа к этой памяти, но только при использовании драйверов:

== по спецификации XMS (эту память называют тогда XMA - eXtended Memory Area);

== EMS (память называют EM - Expanded Memory).

Доступ к расширенной памяти согласно спецификации XMS (eXtended Memory Specification) организуется при использовании драйверов XMM (eXtended Memory Manager). Часто эту память называют дополнительной, учитывая, что в первых моделях персональных компьютеров эта память размещалась на отдельных дополнительных платах, хотя термин Extended почти идентичен термину Expanded и более точно переводится как расширенный, увеличенный.

Спецификация EMS (Expanded Memory Specification) является более ранней. Согласно этой спецификации доступ реализуется путем отображения по мере необходимости отдельных полей Expanded Memory в определенную область верхней памяти. При этом хранится не обрабатываемая информация, а лишь адреса, обеспечивающие доступ к этой информации. Память, организуемая по спецификации EMS, носит название отображаемой, поэтому и сочетание слов Expanded Memory (ЕМ) часто переводят как отображаемая память. Для организации отображаемой памяти необходимо воспользоваться драйвером EMM386.EXE (Expanded Memory Manager) или пакетом управления памятью QEMM.

Расширенная память может быть использована главным образом для хранения данных и некоторых программ ОС. Часто расширенную память используют для организации виртуальных (электронных) дисков.

|

|

|

Исключение составляет небольшая 64-Кбайтная область памяти с адресами от 1024 до 1088 Кбайт (так называемая высокая память, иногда ее называют старшая: HMA - High Memory Area), которая может адресоваться и непосредственно при использовании драйвера HIMEM.SYS (High Memory Manager) в соответствии со спецификацией XMS.HMA обычно используется для хранения программ и данных операционной системы.

Логическая организация памяти или логическая память вычислительной системы является предметом рассмотрения уровня операционной системы и рассмотренная в качестве примера структура логической памяти ПК является частным случаем ее организации. Но тем не менее можно отметить общие черты, характерные для логической структуры памяти независимо от того будь это ПК или мейнфрэйм.

Во-первых любая вычислительная система,а точнее ее операционная система имеет так называемые постоянно- распределенные области памяти, о которых мы уже упоминали. Эти области обычно располагают в начале памяти и обращение к ним непосредственно по реальным или физическим адресам. В этих областях размещают системные данные: таблицы преобразования для виртуальных адресов, таблицу векторов для обработки прерываний (ПК), старые и новые слова состояния программ обработки всех видов прерываний(PSW системы IBM), управляющую информацию для системы ввода вывода и информацию о ее состоянии, информацию о состоянии процессора и самой памяти и т.д.

Во-вторых, это области памяти, предназначенные для программ операционной системы и программ пользователей, размеры и число которых зависит от архитектуры самой системы. А также области памяти,выделенные системе ввода вывода для хранения состояния всех текущих операций ввода вывода для каждого устройства.

На выше приведенных рисунках приведены схемы распределения областей физической памяти по функциональному назначению(структура логической памяти)

Дадим краткую характеристику некоторым областям.

VGA и MDA области памяти (0A000-0BFFFF)

Видео карты используют эти полученные в наследство области адресного пространства для маркировки своих буферов. По умолчанию доступ к этим областям передается на хаб- интерфейс, связывающий северный мост(MCH) c южным мостом (ICH), на котором расположены контроллеры всех интерфейсов ввода вывода. Однако,если биты доступности к VGA установлены в конфигурационном регистре северного моста, то транзакции из этих областей пересылаются в графический адаптер AGP, подсоединенный к северному мосту то есть эти области передаются в распоряжение AGP. Но если в системе при конфигурации обнаружен монохромный адаптер, то область адресного пространства в памяти MDA передается безусловно этому адаптеру и все транзакции направленные в эту область переадресуютcя в MCH в южный мост.

|

|

|

Область 0C0000-FFFFFF

Эта область памяти разбивается на три части

- расширенная область для ISAшины(000C0000-000D0000)

-расширенная область BIOS (000E 0000-000E FFFF)

-область системного BIOS (000F0000-000FFFFF) по умолчанию после сброса эта область закрыта для чтения и записи и все обращения к ней транслируются на хаб – интерфейс к микросхеме BIOS.

Однако MCH может копировать BIOS в свою память при установке соответствующего режима в контроллере памяти.

Распределение областей памяти выше 1МГБ.

ISA HOLE MEM. SPASE (окно в памяти для ISA)

BIOS может открыть окно между 15мгб и 16мгб для переадресации транзакций на хаб- интерфейс, вместо того чтобы завершить на системной памяти.

TSEGSMM (Сегмент области памяти для режима SMM)

Эта область памяти находится под управлением программного обеспечения, осуществляющего режим SMM в системе,этот регион памяти может быть размером от 128клб до1мгб. Доступ в эту область возможен, если она открыта или MCH получает специальный код транзакции на системной шине. В случае если область открыта, а агент на шине пытается обратится с несанкционированным для него обращением в эту область, транзакция аннулируется.

Верхняя область памяти для режима SMM (FEDA0000-FEDBFFFF)

Эта кэшируемая область адресного пространства дает возможность переадресации при обращении к ней в совместимую некэшируемую область между 000A 0000-000BFFFF.

Область AGP/PCI

Технология горячей замены выделяет дляAGP достаточное пространство для всех устройств, расположенных за мостом PCI-PCI,соединяющим AGP c системной шиной. Все обращения в эту область декодируются и передаются в AGP.

|

|

|

Область памяти I/O APIC (FEC00000-FEC7FFFF)

Эта область используется для связи контроллеров прерывания APIC, которые могут быть размещены на системной шине. Ввиду использования технологии горячей замены возникают трудности с идентификацией их на шине,поэтому для них отводится область фиксированных адресов в памяти,то есть используется технология адресации внешних устройств с отображением на адресное пространство памяти. Все обращения в область I/O APIC со стороны процессора пересылаются на хаб- интерфейс в южный мост.

Область для фиксации прерываний на системной шине (FEE00000-FEEFFFF)

Эта область используется для передачи прерываний на системную шину. Любое устройство на AGP или на хаб- интерфейсе может формировать цикл обращения по записи в память по адресу 0FEEх хххх. MCH принимает эту запись совместно с данными на шине согласно протокола шины PCI и продвигая дальше на шину как сообщение о прерывании, блокируя цикл записи в память.

Лекция N 3

Тема лекции:

1.Физические структуры адресных запоминающих устройств и их классификация.

2. Динамическая память DRAM. Функционирование, физические процессы при записи /считывании данных, временные параметры и характеристики

3.Средства повышения производительности памяти. Модульное построение памяти. Регенерация динамической памяти.

В основу концепции физической организации адресных запоминающих устройств заложен принцип однозначного соответствия между каждым элементом данных из области данных и соответствующим ему элементом(адресом) из области адресного пространства.

Значение адреса выражают величиной двоичного n-разрядного числа, то есть всевозможные комбинации этого числа, определяемые как N=2*n будут определять число элементов данных по- другому ее объем.

Так что же представляет собой элемент данных в памяти

Минимальным элементом в двоичном коде является бит значение которого принимает 0или1.

Вычислительная система а по другому ее программно –аппаратный комплекс оперирует в основном не каждым битом (хотя такие операции существуют) а над их группами(символы,байты, слова) поэтому в качестве минимального элемента к которому организуют обращение со стороны процессора к памяти почти во всех современных вычислительных системах используют байт.

И так обращаясь за байтом в оперативную память мы в тоже время обращаемся ко всем битам входящим в состав байта а это возможно только в случае,если все биты байта адресовать одним и тем же значением адреса.

В случае обращения за группой байт мы обязаны откинуть (не учитывать) младшие разряды адреса в количестве p=logn по основанию2 а n-количество одновременно выбираемых байт.

Технологически решить эту задачу можно по разному.

Можно организовать физическую структуру, в которой происходит обращение к одному биту и объединить несколько таких структур с запараллеливанием их соответствующих адресных входов.

А можно организовать обращение к нескольким элементам памяти одновременно внутри самой структуры путем их подключения к одной и той же линии выборки.

В первом случае физическая организация памяти строится по матричному способу подобно декартовой системе координат которой как известно каждой точке определены значения координат X и Y, так и в матричной структуре местонахождение элемента данных (бита) определяется однозначно на пересечении двух линий выборки по X и Y.Активизация этих линий происходит при дешифрации значений, поступающих на ДШX и ДШY, которые представляют части значения адреса.

Во втором случае используется один дешифратор то есть все биты значения адреса подают на него, который вырабатывает лишь один активный сигнал в каждом случае. Эти сигналы подаются по шинам в память, каждая шина активирует сразу несколько элементов,подключенных к ней.

В зависимости от применения одного из способов или их совместного применения классифицируют различные структуры учитывая при этом еще и количество шин управления подводимых к элементам данных в памяти.

Исходя из выше сказанных замечаний рассмотрим различные физические структуры адресных запоминающих устройств.

Для того чтобы осуществить запись или чтение в адресные ЗУ к каждому элементу этого ЗУ хранящему минимальную информацию (бит) необходимо подавать управляющую информацию в виде адресных и информационных (данных) сигналов в зависимости от количества физических линий, используемых для этих целей и их использование для передачи логических значений сигналов различают структуры 2D,3D, 2.5D, 2DM.

Где D (dimension)- размер

А число - определяющее число линий адресных, и линий записи/считывания подводимы к каждому элементу памяти. Причем при подсчете линий записи и линий чтения принимают за 1. Структура 2D,3D, 2.5D характерны были при использовании элементов на магнитные сердечники, которые мы и рассмотрим.

Структура 2DM характерна для современных памятей, при организации матриц из элементов собираемых на базе транзисторов, в которых в качестве запоминающего элемента используется емкость изолированного стока, выполняющая функцию конденсатора.

Запоминающее устройство типа 2D имеет двух координатную выборку, причем только одна координата связана со значением адреса, который определяет адрес выбираемого слова, то есть структура построенная по второму способу. Вторая координата

не связанная с шиной адреса используется для управления разрядом в слове при записи и считывании. Координата представляет две гальванически развязанные шины шину записи и шину считывания, к которым подключены усилители записи и считывания соответственно.

| ||||||||||

| ||||||||||

| ||||||||||

| ||||||||||

Запись Чтение

В режиме записи и считывания в координатную обмотку подаются токи разного направления, причем ток осуществляющий считывание по величине в два раза больше и должен осуществлять

перемагничивание сердечника (перевод его в нулевое состояние)

В случае единичного состояния сердечника при считывании в обмотке считывания наводится ЭДС величина тока которой определяет считывание единицы. Если сердечник находился в состоянии нуля, то ток в обмотке считывания отсутствует, так как отсутствует изменение магнитного потока, а ток помехи, возникающий от перемагничивания по частичному циклу усилителем чтения не воспринимается.

Ток записи должен быть по амплитуде равным 1/2

тока чтения и быть направлен в противоположном направлении и только в случае тока записи, подаваемого в обмотку записи разряда и имеющего то же направление, что и ток записи в адресной обмотке по сумме двух токов осуществляется перевод сердечника в состояние “1”.

В случае записи нуля ток в обмотке записи отсутствует, а величина тока записи в адресной обмотке не достаточна чтобы перевести сердечник в состояние ‘1’.

Анализируя вышесказанное можно сделать следующий вывод:

Данная структура при использовании в качестве элемента памяти магнитный сердечник при каждом обращении независимо от вида операции (запись или чтение) реализует два смежных цикла ЧТЕНИЕ-ЗАПИСЬ, с той лишь разницей, что при чтении считанные данные возвращаются обратно в память, а при записи, в предварительно обнуленные ячейки в цикле чтения, новые данные

управляют усилителями записи.

Функциональная схема элемента памяти в структуре 2DM.

Структура 2DM

Структура 2DM стала представлять дальнейшую модификацию уже существовавших ранее структур 2D и 2,5D.

От архитектуры 2D в 2DM использована возможность одновременной активизации n элементов (слова, страницы); от 2,5D взята возможность управления поразрядного считывания и записи из матрицы, другими словами говоря в матрице 2DM стали размещать элементы не одного разряда а нескольких как в 2D при чем объединив гальванически три шины в одну,а именно, координатную Y, разрядной записи и разрядной шины считывания

благодаря использованию в качестве запоминающего элемента транзистора с изолированным стоком, используемого в качестве обкладки накопительного конденсатора. Отметим еще раз что структура 2D на магнитных элементах,функционирующих на принципе закона электромагнитной индукции такого объединения не допускает.

Выбор той или иной физической структуры, рассмотренные нами выше, является только частью этапа проектирования памяти. Структура определяет только топологию накопительного блока памяти, число адресных и управляющих шин подводимых к каждому элементу для хранения данных, но не определяет временных параметров и соотношений сигналов, поступающих по этим шинам к элементам. Для того чтобы устанавливать эти параметры(длительность сигналов и и их задержки относительно друг друга) необходимо знать физические процессы, происходящие в накопительном блоке при считывании и записи данных.

Проектирование временных диаграмм, определение вида и числа сигналов,управляющих работой накопительного блока это и есть разработка протокола связи (интерфейса) памяти с вычислительной системой (процессором). Протокол реализуется блоком управления памятью. Конструктивно блок управления памятью может находиться как в составе процессора, так и на системной плате внедренным в системный чипсет, а может находиться и в самой микросхеме (внутренний контроллер). Поэтому прежде чем рассматривать организацию современных памятей с повышенным быстродействием рассмотрим основные моменты работы DRAM и процессы происходящие в ней при считывании и записи данных.

1.В режиме хранения ЛВ пассивна транзистор закрыт.

При выборке элемента на линию выборки подается напряжение, открывающее транзистор.

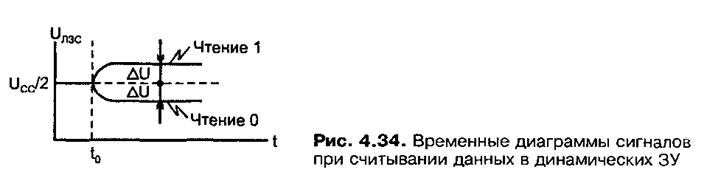

2. Перед активизацией выборки элемента на линию ЛЗС через ключ 3 подается напряжение V/2. Как только будет подан сигнал на линию выборки (ЛВ) ключ к3 размыкается.

С момента подключения С заряда к линии записи/считывания начинается процесс перезаряда выравнивание потенциалов между С лзс и С заряда. Предположим что С заряда была разряжена до 0(запись 0) тогда т.к С лзc была заряжена напряжением V/2 то

Qлзс=Слзс*V/2

После перезаряда исходя из закона сохранения заряда Qлзс=(Cлзс+С3)*(V/2-∆U)

Откуда величина ∆U=V*Cзаряда/2*Слзс

Величина ∆U тем больше, чем меньше Слзс. В случае записи 1 в элементе Слзс будет подзаряжено до величины V/2+∆U

Для повышения уровня ∆U в технологии изготовления матриц в структуре 2DM с элементом памяти полупроводников также используют следующие технологические приемы:

А) увеличение емкости С заряда за счет диэлектрика, имеющего высокую диэлектрическую постоянную.

Б) уменьшение емкости ЛЗС за счет разрезания ЛЗС на 2 части и распределение запоминающих элементов поровну между ними. При этом для считывания данных из элементов памяти в разрыв включают дифференциальный усилитель, формирующий выходной сигнал считывания на значении разности потенциалов поступающих на его 2 входа.

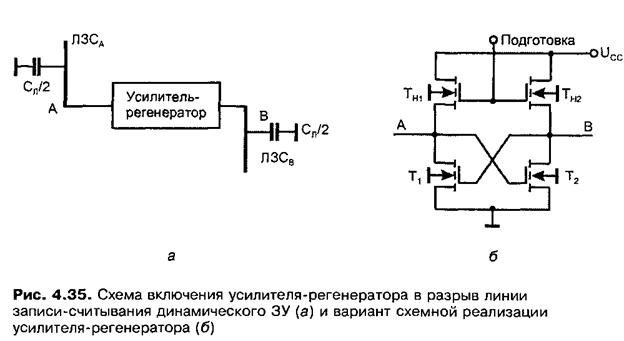

В качестве примера рассмотрим работу схемы усилителя-регенератора используемого в памяти 2DM.

В качестве примера рассмотрим работу схемы усилителя-регенератора используемого в памяти 2DM.

Схема представляет триггерный усилитель, функционирующий при подачи на затворы Т1П и Т2П сигнала «Подготовка», который формируется при считывании данных из запоминающего элемента с линий ЛЗСА или ЛЗСВ. Переключение триггера будет зависеть от значений потенциалов формирующихся при считывании, т.к. активной будет только одна линия, другая всегда будет сохранять значение предварительного перезаряда, которым были заряжены обе линии перед считыванием.

И так если с ЛЗСА если 1 то

Vлза=V/2+∆i

Vлзсв=V/2

Триггер принимает состояния Т2-отрытый, Т1- закрытый, формируя на Vлзсв=0, Vлзса=V, осуществляя регенерацию на линии считывания ЛЗСА, откуда производилось считывание, т.е. элемент считывания будет дозаряжен до значения V. Если с ЛЗСА был считан 0, то триггер принимает состояние противоположное выше описанному. Т1 будет открыт, а Т2 закрыт т.к. Vлзса=V/2-∆U, Vлзсв=V/2

И запоминающий элемент будет разряжен до 0. При считывании информации с линии ЛЗСВ например 1

Vлзсв=V/2+∆U, Vлзса=V/2 и состояние триггера будет такое же как при считывании 0 к линии ЛЗСА и при считывании 0 будет такое же как при считывании 1 с ЛЗСА.

Для того чтобы иметь однозначные значения триггера независимо от считываемой линии организуют инверсионную запись информации в одну из линий, Таким образом фиксируя значения триггера при считывании 0 или 1 независимо от линий считывания

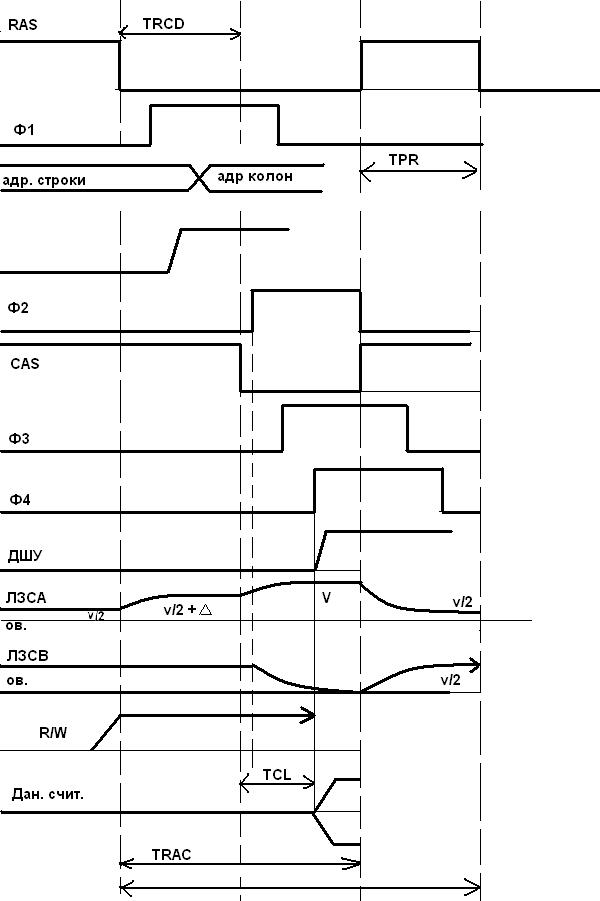

Ознакомившись с процессами, происходящими в памяти при записи и считывании, рассмотрим ее функционирование и временную диаграмму ее работы.

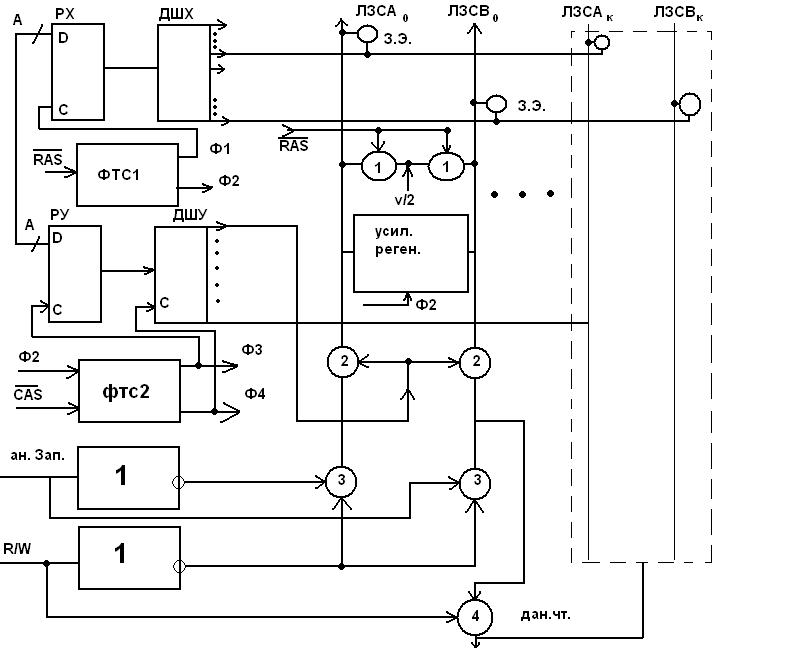

Современная архитектура памяти с произвольным доступом имеет матричную организацию массива запоминающих элементов. Адрес для выбора соответствующего элемента, хранящего информацию, подаётся на модуль памяти за 2 такта (адрес строки, и адрес столбца) с целью экономии числа адресных имен, использую мультиплексирование.

1. Выбор (доступ к элементу памяти) начинается с подачи  , по которому во внутреннем контроллере памяти запускается формирователь ФТС1, формирующий

, по которому во внутреннем контроллере памяти запускается формирователь ФТС1, формирующий  и

и . По

. По  осуществляется приём адреса строки в буферный регистр и активация ДШХ, на выходе которого активизируется одна из линий выборки в результате чего осуществляется подключение запоминающих элементов к линиям ЛЗСА или ЛЗСВ

осуществляется приём адреса строки в буферный регистр и активация ДШХ, на выходе которого активизируется одна из линий выборки в результате чего осуществляется подключение запоминающих элементов к линиям ЛЗСА или ЛЗСВ

2. Одновременно сигнал  блокирует ключи КЛ1

блокирует ключи КЛ1

1) Снимая  с ЛЗСА и ЛЗСВ, потенциал одной из которых будет определяться значением потенциала,которым обладает информационная емкость С, а другая (пассивная) сохранять значение

с ЛЗСА и ЛЗСВ, потенциал одной из которых будет определяться значением потенциала,которым обладает информационная емкость С, а другая (пассивная) сохранять значение

3. Формируется сигнал  по которому подается питание на усилитель- формирователь триггерного типа. С этого момента начинается процесс регенерации и потенциал активной линии ЛЗСА

по которому подается питание на усилитель- формирователь триггерного типа. С этого момента начинается процесс регенерации и потенциал активной линии ЛЗСА  V, а пассивной ЛЗСВ

V, а пассивной ЛЗСВ 0 (считывание 1 с ЛЗСа)

0 (считывание 1 с ЛЗСа)

4. К моменту  должен при высоком

должен при высоком  запускается ФТС2 и формируются

запускается ФТС2 и формируются  в результате действия которых осуществляется прием кода столбца его дешифрация в результате чего на одном из выходов дешифратора появится активный уровень,открываются ключи 2 и считанная информация при условии, что открыт ключ 4 поступает на внешнюю шину.

в результате действия которых осуществляется прием кода столбца его дешифрация в результате чего на одном из выходов дешифратора появится активный уровень,открываются ключи 2 и считанная информация при условии, что открыт ключ 4 поступает на внешнюю шину.

5.Состояние триггерного усилителя- формирователя сохраняется в течении длительности  , которая должна быть достаточной для приёма информации из модуля следующим звеном передачи информации в процессор.

, которая должна быть достаточной для приёма информации из модуля следующим звеном передачи информации в процессор.

6. Сигнал

6. Сигнал  выполнив свою функцию совместно с

выполнив свою функцию совместно с  становятся высокими,, подготавливая модуль памяти для следующего обращения.

становятся высокими,, подготавливая модуль памяти для следующего обращения.

Время между двумя  должно быть достаточным для того, чтобы восстановить на ЛЗСА, ЛЗСВ значение

должно быть достаточным для того, чтобы восстановить на ЛЗСА, ЛЗСВ значение  . Для того, чтобы можно было обратиться к

. Для того, чтобы можно было обратиться к  строке.

строке.

Дадим определения основным временным параметрам работы памяти.

ТRСD- время,определяющее задержку подачи сигнала CAS относительно RAS.Эта задержка необходима для дешифрации адреса строки, активизации линии выборки и отключения линий ЛЗС от источника предзаряда.

TCL- время появления данных на линиях записи считывания от начала активизации сигнала CAS. Время отводимое для приема адреса столбца на дешифрацию и переключение ключа КЛ4,разрешающего выдачу данных с шин ЛЗС

TRAS-полное время цикла записи считывания данных из памяти.

TPR- время предзаряда шин ЛЗС, по другому, время необходимое для восстановления значения напряжения на линиях ЛЗС до величины V/2 в нашем случае, определяется временем срабатывания ключей КЛ1 и постоянной заряда линий ЛЗС

TRAS + TRP- минимальное время, через которое возможно следующее обращение к памяти.

.

1. Одним из первых методов повышения быстродействия памяти была технология расслоения данных в физической структуре памяти и применения метода чередования адресов обращения за данными в такой памяти. Поэтому прежде чем рассматривать другие методы, а в частности те,что используются в современных архитектурах, отдавая дань первым разработкам, остановимся подробнее на этом методе.

Этот метод основан на модульном построении памяти,технологию которого рассмотрим позже, и является одним из частных случаев построения памяти с физической организацией памяти в банки. Физическим банком принято считать модуль или группу модулей памяти, которые устанавливаются одновременно для обеспечения ширины выборки данных из памяти на системную шину.

Такая организация позволяет управлять размером области информационного пространства системной памяти, добавляя или удаляя модули из памяти.

При построении памяти с использованием банков из разрядной сетки адреса выделяют разряды для адресации номера банка, к которому производится обращение. В зависимости от весов этих разрядов (местоположения в адресной сетке) формируются различные конфигурации банков.

Так,например, выбрав для адреса банков младший разряд адреса обращения к памяти мы размещаем четные элементы в одном банке а нечетные в другом а используя технологию чередования адресов обращения к памяти повышаем ее производительность.

И так - расслоение оперативной памяти.- это метод многомодульного построения с веерной адресацией (чередованием) при которой смежные адреса информационных единиц, соответствующих ширине выборки (слова, двойные слова, и т.д.) принадлежат (размещаются) разным модулям.

Следовательно, размещая четные слова в одном, а нечетные в другом модуле при записи и организуя чтение их одновременно, при выборке получим в случае последовательного обращения по адресам увеличение производительности работы памяти. При этом будет необходим коммутатор (мультиплексор) который будет выдавать по системную шину требуемое слово.

|

| |||

| |||

Как следует из анализа работы схемы, и временной диаграммы работы памяти строка находится в активном состоянии на протяжении всего времени длительности сигнала  , а величины потенциалов

, а величины потенциалов  определяются значениями выходов триггера усилителя - регенератора пока на него подаётся питание во время длительности Ф2.

определяются значениями выходов триггера усилителя - регенератора пока на него подаётся питание во время длительности Ф2.

V

V

ЛЗСА ЛЗСВ

Ф2

И так если предположить, что оставляя состояние  длительное время, строка будет активной и Ф2 зафиксировать на триггере, а подавая серию

длительное время, строка будет активной и Ф2 зафиксировать на триггере, а подавая серию  , и адреса столбцов в модуль памяти, получим увеличение быстродействия. Именно в таком режиме работает FPM.

, и адреса столбцов в модуль памяти, получим увеличение быстродействия. Именно в таком режиме работает FPM.

| ||

|

FPM

FPM

CAS

счит.данных

Частота следования  , определяет время необходимое для передачи данных из памяти в процессор.

, определяет время необходимое для передачи данных из памяти в процессор.

Так вот если ввести буферный регистр, который будет сохранять данные, то частоту следов.  можно увеличить.

можно увеличить.

RAS

| |||

| |||

CAS

CAS

|  | ||||

| |||||

шА ROW

шА ROW

буфер

Данные считываются и принимаются в буфер

row col1 col2

ШД

ШД

date1 date2

В памяти ЕДО серия  поступает из контроллера памяти в модуль.

поступает из контроллера памяти в модуль.

Дальнейшее увеличение быстродействия было реализовано BEDO- Best External Data Out путём введения в модуль счётчика

Дальнейшее увеличение быстродействия было реализовано BEDO- Best External Data Out путём введения в модуль счётчика  число импульсов которого определяется длинной пакета, а адрес колонки передается в память только при первом обращении.

число импульсов которого определяется длинной пакета, а адрес колонки передается в память только при первом обращении.

| |||

| |||

| |||

RAS

ROW

ROW

CAS ВЕDО

CAS ВЕDО

. col1

. col1

ША

ША

| ||||||||||||

| ||||||||||||

|  | |||||||||||

|  | |||||||||||

|  | |||||||||||

внутренний счетчик CAS

внутренний счетчик CAS

ШИНА ДАННЫХ

Архитектура памяти SDRAM.

Хотя SDRAM содержит внутри память DRAM, работающую как EDO, принцип управления модулем SDRAM совершенно другой, а улучшение производительности достигнуто путем “ скрытой” внутренней работы DRAM специальными методами по другому внедрением аппаратных средств, а именно:

1.Синхронизация всех операций в памяти тактовой частотой системной шины.

2.Разделение микросхемы SDRAM на внутренние банки (логические). Такое решение позволило реализовать режим чередования страниц, давший возможность исключить задержки, связанные с регенерацией, и организовать непрерывность потока данных.

3.Конвейерная обработка данных позволила производить обращение по новому адресу столбца в каждом тактовом цикле, кроме того подобно EDO микросхема SDRAM имеет внутренний счетчик потока, определяющий количество слов в потоке, и устанавливаемый из регистра режима.

4.Регистр режима предназначен не только для хранения размера потока но и информации о типе потока(последовательное считывание или с чередованием) то есть SDRAM является устройством с программируемыми параметрами, которые и заносятся в выше упомянутый регистр.

Запись в него осуществляется в специальном цикле из внешнего контроллера памяти, данные передаются по адресной шине.

После такта записи в регистр режима следует обязательно пустой такт NOP. По окончании двух тактов инициализации начинается цикл обращения к памяти с команды “активизация”, во время выполнения которой из внешнего контроллера в SDRAM передается адрес внутреннего банка по шинам адреса и адрес строки в банке.

Указав на архитектурные особенности SDRAM,остановимся на них подробнее. Ну, во-первых, в архитектуре SDRAM вводится понятие логического банка. Вначале мы упоминали о модульном построении памяти, так вот распространяя выше упомянутую технологию на внутреннюю архитектуру самой микросхемы памяти мы приходим к понятию логический банк.

По сути физическая организация микросхемы, в которой хранятся данные (матрица) в случае организации логических банков с технологической точки зрения можно представить как набор независимых друг от друга матриц,на которые разрезали одну большую матрицу микросхемы,сохранив подачу одних и тех разрядов адреса строк и колонок на их дешифраторы, дополнительно подавая значения номера банка для активизации суббматрицы,хранящей информацию того или иного банка.

Возникает вопрос. Так почему же эти внутренние банки микросхемы назвали логическими.

Ответить можно на него ссылаясь, например, на аналогичное понятие как логический диск. Логический диск-это часть дискового пространства(цилиндры или несколько дорожек) физического диска видимых вышестоящему уровню операционной системы как независимый управляемый объект, так же и логический банк, находящийся внутри микросхемы для программы видится как отдельный объект со своей памятью, к которой можно производить обращение.

Такое разрезание сделало независимыми строки разных банков, что позволило открывать последовательностью команд “активизация” их в банках в каждом цикле работы памяти и производить независимые обращения.

Если внешний контроллер “знает,” какие данные следует передать в банк, и в каком банке они находятся в случае их размещения в одном и том же физическом банке, то он может организовать обмен данными между логическими банками с задержкой в один цикл.

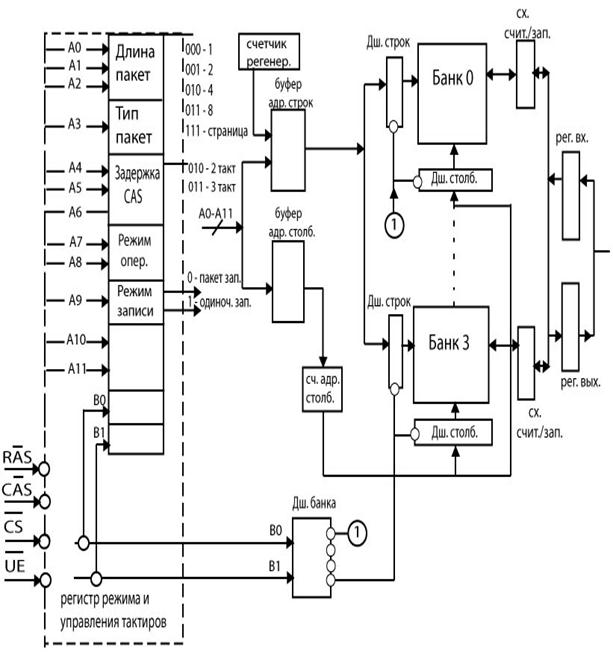

Реализация конвейера при считывании данных из памяти иллюстрируется на вышеприведенной схеме и временной диаграмме. Суть заключается в том что прием адреса столбца в буферный регистр и активизация дешифратора осуществляются двумя сериями синхронизации, смещенными во времени на такт поэтому регистр адреса столбца, передав информацию на входы дешифратора в течение текущего такта, становится свободным для приема следующего адреса колонки к началу фронта следующего синхроимпульса; а в это же время начинается дешифрация адреса предыдущей колонки таким образом данные из памяти будут выдаваться в каждом следующим такте системной шины.

Как видно из схемы для организации пакетного режима из внешнего контроллера необходимо передать адрес первой колонки(начало пакета) и значение загружаемое в счетчик(длину пакета). Из вышесказанного следует что для организации пакетного режима требуется подготовительная операция,которая и осуществляется в специальной команде “установка регистра режима”из внешнего контроллера.

Внешний контроллер в свою очередь для реализации протокола связи с модулем памяти имеет свой регистр режима, управляемый как внутренней аппаратной логикой, так и выше стоящим уровнем (программой) через процессор из которого и поступает тот или иной приказ на установку режима работы.

Каким образом осуществляется связь процессора с внешним контроллером памяти мы разберем в дальнейшем, а сейчас отметим то,что регистр режима внешнего контроллера реализует следующие режимы по коду получаемому из программы или от внутренней логики

сброс(cаморегенерация)-000

nop(нет операции) -001

все банки закрыть -010

уст регистра режима -011

регенерация - 110

нормальная операция - 111

МОДУЛЬНОЕ ПОСТРОЕНИЕ ПАМЯТИ

Так как микросхемы памяти по глубине своего адресного пространства, которое определяется числом входов подаваемых на адресные входы микросхем не обеспечивает в большинстве случаев объем системной памяти, то при расчете в первую очередь проводят расчет субмодуля - узла из количества микросхем, обеспечивающих ширину выборки.

:

:

:

m

m

|  | ||

L/m – количество микросхем,

емкость субмодуля

емкость субмодуля

:

: m

|  |

Ввиду того, что из памяти считывается L разрядов одновременно, где количество считываемых байт равно L/8, а в памяти адресуется каждый байт, то для адресации одновременно считываемых байт из памяти мы обязаны откинуть справа в адресной сетке «Р» разрядов.

. Или

. Или  - количество одновременно считываемых байт. Оставшиеся разряды будут использованы следующим образом:

- количество одновременно считываемых байт. Оставшиеся разряды будут использованы следующим образом:

- число субмодулей

- число субмодулей

- емкость микросхем

- емкость микросхем

- шина выборки

- шина выборки

+

+ - емкость субмодуля

- емкость субмодуля

|

|

t разрядов k p

А[0÷k-1]

|

|

Старшие

t разрядов::

t разрядов::

|

::

::

|

РЕГЕНЕРАЦИЯ ПАМЯТИ

Динамическая память требует восстановления информации после обращения в неё за данными и в процессе хранения ввиду саморазряда конденсаторов, которые используют в качестве запоминающего элемента.

Как было рассмотрено при анализе DRAM и SDRAM, для регенерации достаточно активизировать только строки, при этом происходит автоматическое восстановление информации во всей строке. Т.е. через определённое время каждый элемент памяти требует к нему обращения с целью восстановления хранимой в нём информации. Различные системы реализуют этот процесс по-разному.

Так в системах с шинной организацией, где на шине данных и адреса кроме данных находятся другие агенты шины, контролер шины вынужден через определенные промежутки времени организовывать запрос к процессору на владение шиной.

Так в свое время в режиме регенерации был задействован один из каналов DMA (прямого доступа памяти), в котором хранилась информация адреса, на котором останавливался предыдущий цикл.

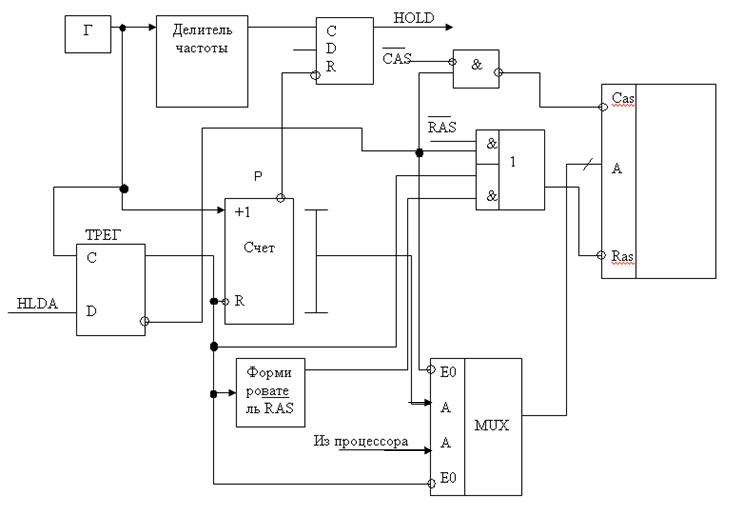

Блок-схема

Блок-схема

Генератор вырабатывает импульсы и через делитель частоты организует импульсы запросов на регенерацию процессор. В случае подтверждения устанавливает ТРЕГ=1, разрешая работу счетчика, формирующего адреса регенерации (строк) и сопровождающиеся сигналом RAS. На время регенерации блокируются сигналы RAS и CAS от процессора. Цикл регенерации определяет время работы счетчика и заканчивается по сигналу переполнения. Для подачи адреса строки на модуль используется мультиплексор, управляющий триггером регенерации.

В архитектуре современных компьютеров с шинной организацией, в которых интегрированная память, контроллер выделен. Схема управления регенерацией организована как во внешнем контроллере, так и частично во внутреннем контроллере (микросхема памяти). Внешний контроллер выдает только команду регенерации CBR, которая формируется через определенное время, обозначенное циклом регенерации.

Поскольку обращение к памяти к различным ее ячейкам происходит в случайном порядке, то для динамической памяти для сохранности информации необходимы циклы регенерации.

Memory Refresh.

Циклы регенерации могут быть организованы различными способами. Классическим способом является цикл без импульса CAS, сокращенно ROR (RAS only refresh)

Вторым распространенным способом является CBR (CAS before RAS). Данный способ в частности используется в SDRAM, т.к. последовательный ROR в этой памяти воспринимается как команда «АКТ» - активизация строки. Кроме организации циклов регенерации со стороны внешнего контроллера используется режим само регенерации. Адрес регенерируемой строки берется из внешнего контролера для цикла ROR и из внутреннего счетчика регенерации для цикла CBR. Т.е. для SDRAM адрес регенерируемой строки хранится в самой микросхеме памяти. Активизация циклов CBR из внешнего контролера происходит через определенные промежутки времени.

Само регенерация.

Режим само регенерации организуется в микросхеме при переводе сигнала CKE(clock enable) в низкий уровень со стороны внешнего контролера.

В режиме само регенерации микросхемы периодически выполняют циклы регенерации по внутреннему таймеру и не реагируют на внешние сигналы, поэтому внешняя синхронизация может быть остановлена. Причинами остановки синхронизации могут быть следующие обстоятельства:

1) выполнение инструкции HULT в процессоре. В результате процессор переходит в состояние S1

S1 – останавливает таймеры системной платы, но сохраняются данные в системной памяти.

2) S2 – дополнительно отключается питание КЭШ, системной платы и процессора, но сохраняется состояние оперативной памяти

3) S3 – обесточиваются все компоненты системной платы, кроме оперативной памяти

Примечание: выполнение ‘SLEEP’ [S1, S2, S3] может произойти в случае ‘shut down’, когда операционная система обнаруживает аварийную ситуацию.

Лекция N4.

Кэш память. Принцип организации кэш. Виды КЭШей.

Механизм LRU замены строк в кэш.

КЭШ ПАМЯТЬ

Тенденция к повышению производительности работы В.С. привела к необходимости ввода в архитектуру так называемой КЭШ памяти, являющейся дополнительным буфером информации между системной памятью и процессором. КЭШ память по объёму намного меньше, чем системная память и хранящая копии её ячеек, помимо накопительного блока, для данных, должна содержать индексный или тэговый блок по адресному объёму равный накопительному. В этом индексном блоке должна храниться информация однозначно определяющая какие конкретные ячейки оперативной памяти отражаются в тех или иных ячейках накопительного блока КЭШ.

Так как системная память является адресным устройством с произвольным доступом, то в качестве тэгов используются адреса ячеек системной памяти (полный или частичный в зависимости от архитектуры КЭШ)

Различают в основном 3 типа КЭШ:

- полностью ассоциативная,

- прямого отображения

- наборно-ассоциативная.

Полностью ассоциативная КЭШ.

Этот тип КЭШ в своей тэговой части содержит полный физический адрес требуемых данных, однозначно определяющий их место в системной памяти. Поэтому в КЭШ такой архитектуры содержимое любой ячейки системной памяти может быть помещено в любую ячейку КЭШ.

Но с другой стороны схема поиска о наличии данных в таком КЭШ является сложной, так как требуе

|

|

|

|

Дата добавления: 2014-01-03; Просмотров: 2015; Нарушение авторских прав?; Мы поможем в написании вашей работы!