КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Страничная организация памяти

|

|

|

|

Сегментная организация памяти

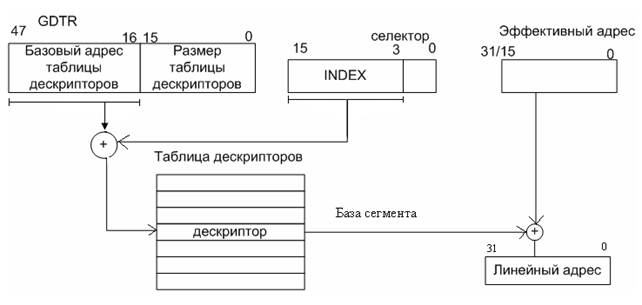

В защищенном режиме для формирования линейного адреса используется две компоненты:

1)16-тиразрядный селектор для определения базового адреса сегмента, который содержится в дескрипторе.

2)16 или 32-хразрядный эффективный адрес, который зависит от режима работы и способа адресации.

Проиллюстрируем процесс вычисления линейного адреса с помощью следующей схемы:

Для получения линейного адреса базовый адрес сегмента, содержащийся в дескрипторе, суммируется с эффективным адресом.

При отсутствии страничной организации памяти линейный адрес является физическим адресом для обращения к элементу памяти.

Страничный диспетчер памяти, имеющийся в микропроцессоре, обеспечивает следующую возможность: 1)представляет пользователю возможность работать с большим адресным пространством;

2)обеспечивает защиту ОС и программное обеспечение пользователя;

3)реализует быструю трансляцию адресов.

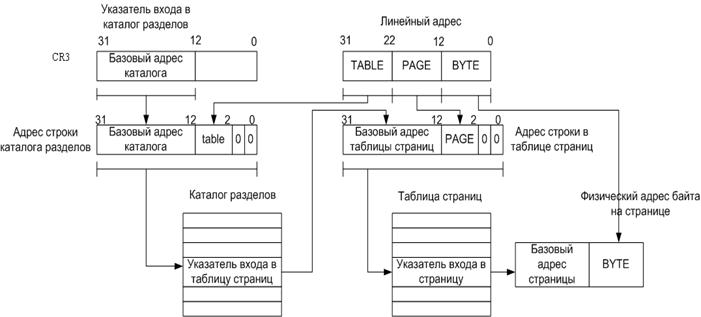

Линейное адресное пространство памяти объемом 4 Гб при страничной организации разбито на 220 страниц объемом по 4 кб каждая страница. Фиксированный размер всех страниц позволяет загружать любую требуемую виртуальную страницу в нужную физическую страницу.

Страничная трансляция включается в защищенный режим установкой в единицу 31-го разряда нулевого регистра управления CRQ и выключается сбросом этого разряда в ноль.

При страничной организации сегмент разбивается на отдельные разделы, число которых может достигнуть до 210.

В свою очередь каждый раздел может содержать до 210 страниц объемом по 4 кб каждая. Начальные (базовые) адреса страниц каждого раздела хранятся в соответствующей таблице страниц, содержащейся в памяти. Обращение к этой таблице производится с помощью каталога, в котором содержатся начальные адреса таблиц страниц для всех разделов. Таким образом, страницы могут быть рассеяны по разным частям памяти, а их размещение в памяти определяется содержимым каталогов разделов и таблиц страниц.

|

|

|

|

Линейный 32-ый адрес при страничной организации памяти является исходной информацией для формирования физического адреса с помощью каталога разделов и таблиц страниц. При этом линейный адрес рассматривается как совокупность трех полей.

TABLE – указывает относительный адрес таблицы страниц выбираемого раздела в каталоге.

PAGE – задает относительный адрес требуемой страницы данного раздела.

BYTE – содержит относительный адрес выбираемого на странице байта.

Каталог разделов занимает одну страницу памяти, где для каждого раздела содержатся 32-разрядные указатели входа в таблицу страниц этого раздела. Каждая из таблиц страниц также занимает одну страницу памяти, где для каждой страницы дается 32-хразрядный указатель входа в эту страницу.

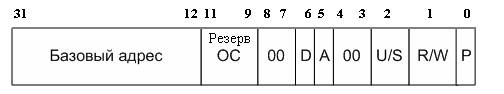

Указатели входа в раздел и в страницу имеют одинаковый формат:

Каждый указатель содержит информацию, определяющую порядок использования страниц. Старшие 20 разрядов занимает базовый адрес. Остальные разряды имеют следующий смысл.

Р – бит присутствия. Если Р=1, то разрешается использование таблицы страниц, если Р=0, то такое использование запрещается. При Р=0 попытка обращения к соответствующему разделу или странице вызывает прерывание из-за отсутствия нужной страницы в оперативной памяти. После загрузки нужной страницы в память, бит Р устанавливается в «1» и в этом случае обращение к данной странице становится возможной. Это нужно для того, чтобы ОС знала, где находится страница.

R/W - бит чтения/записи.

U/S - бит пользователь/супервизор.

Эти два бита определяют право доступа к соответствующей странице или разделу для программ пользователя. Программа пользователя обычно имеет самый низкий уровень привилегий равный 3. Если осуществляется запрос с уровнем привилегий равным 3, то при значении U/S = 0 программе пользователя запрещается доступ к разделу или странице.

|

|

|

При U/S = 1 обращение разрешается, но при этом учитывается значение бита R/W.

Если R/W = 0, то программе пользователя разрешается только чтение раздела или страницы.

Если R/W = 1, то разрешается как чтение, так и запись. Если осуществляются запросы с большим уровнем привилегий (0, 1 и 2), то допускается запись и чтение разделов и страниц при любых значениях ‘1’ и ‘2’ разрядов.

Такие уровни привилегий имеет ОС.

А - бит доступа. Этот бит автоматически устанавливается в «1» микропроцессором при обращении к данному разделу или странице для записи или чтения.

D – бит «мусора». В указателе кадра страницы этот бит устанавливают в «1» при записи на данную страницу. Для указателей таблиц страниц значение бита D является неопределенной.

Биты D и A используются ОС, поддерживающей виртуальную память, для определения в ОЗУ тех разделов и страниц, которые подлежат удалению из ОЗУ, поскольку к ним долгое время не было обращения. Проверку и сброс этих разрядов выполняет ОС.

Алгоритм формирования физического адреса:

Содержимое CR3 (регистр управления) задает старшие 20 разрядов базового адреса для входа в каталог раздела. Для получения физического адреса строки каталога разделов к этим 20 разрядам добавляется 10-тиразрядное поле TABLE линейного адреса и 2 нулевых младших разрядов. По полученному таким образом адресу обращаются к каталогу разделов, откуда выбирают указатели входа в таблицу страниц. Этот указатель содержит 20-разрядный базовый адрес таблицы страниц. К этим 20 разрядам добавляется поле PAGE и 2 нулевых младших разряда. В результате получается адрес строки таблицы страниц. В этой строке находится указатель входа в страницу, содержащий 20-разрядный базовый адрес страницы. Добавление к этому базовому адресу 12-тиразрядного поля BYTE дает физический адрес байта.

Существенное сокращение времени преобразования адресов в микропроцессоре достигается путем внутренней ассоциативной памяти, которая называется «буфером ассоциативной трансляции» и обозначается TLB.

|

|

|

|

|

Дата добавления: 2013-12-12; Просмотров: 432; Нарушение авторских прав?; Мы поможем в написании вашей работы!