КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Тактовые генераторы

Г

Я

Выход

Сумма

Сумма

| |||||

| |||||

|

|

| Линии разрешения |

|

Полный сумматор

|

Декодер

Декодер

Выход переноса

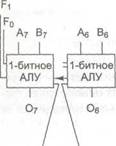

Рис. 3.18. Одноразрядное АЛУ

В верхнем левом углу схемы находится логическое устройство для вычисления А И В, А ИЛИ В и В, но по крайней мере один из этих результатов проходит через последний вентиль ИЛИ в зависимости от того, какую из разрешающих линий выбрал декодер. Так как ровно один из выходных сигналов декодера будет равен 1, то и запускаться будет ровно один из четырех вентилей И. Остальные три вентиля будут выдавать 0 независимо от значений А и В.

АЛУ может выполнять не только логические и арифметические операции над А и В, но и делать их равными нулю, отрицая ENA (сигнал разрешения А) или ENB (сигнал разрешения В). Можно также получить А, установив INVA (инверсию А). Зачем нужны ENA, ENB и INVA, мы рассмотрим в главе 4. При нормаль-

Основные цифровые логические схемы

ных условиях и ENA, и ENB равны 1, чтобы разрешить поступление обоих входных сигналов, а сигнал INVA равен 0. В этом случае А и В просто поступают в логическое устройство без изменений.

ных условиях и ENA, и ENB равны 1, чтобы разрешить поступление обоих входных сигналов, а сигнал INVA равен 0. В этом случае А и В просто поступают в логическое устройство без изменений.

Вход Выход переноса переноса

Вход Выход переноса переноса

А5 В5

1-битное АЛУ

1-битное АЛУ

О5

О5

| А4 В4 |

Аз В3

| 1-битное АЛУ |

1-битное АЛУ

О4 О3

О4 О3

А2 В2

1-битное АЛУ

1-битное АЛУ

О2

О2

А, В,

1-битное АЛУ

1-битное АЛУ

Ао Во

1-битное АЛУ

1-битное АЛУ

Оо

Оо

INC

Рис. 3.19. Восемь одноразрядных секций, соединенных в 8-разрядное АЛУ Сигналы разрешения и инверсии не показаны для упрощения схемы

В нижнем правом углу находится полный сумматор для подсчета суммы А и В и для осуществления переносов. Переносы необходимы, поскольку несколько таких схем могут быть соединены для выполнения операций над целыми словами. Одноразрядные схемы, подобные той, которая изображена на рис. 3.18, называются разрядными микропроцессорными секциями. Они позволяют разработчику сконструировать АЛУ любой желаемой ширины. На рис. 3.19 показана схема 8-разрядного АЛУ, составленного из восьми одноразрядных секций. Сигнал INC (увеличение на единицу) нужен только для операций сложения. Он дает возможность вычислять такие суммы, как А+1 и А+В+1.

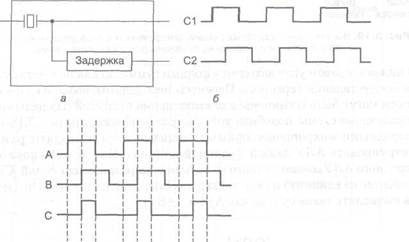

Во многих цифровых схемах все зависит от порядка, в котором выполняются действия. Иногда одно действие должно предшествовать другому, иногда два действия должны происходить одновременно. Для контроля временных отношений в цифровые схемы встраиваются тактовые генераторы, чтобы обеспечить синхронизацию. Тактовый генератор — это схема, которая вызывает серию импульсов. Все импульсы одинаковы по длительности. Интервалы между последовательными импульсами также одинаковы. Временной интервал между началом одного импульса и началом следующего называется временем такта. Частота импульсов обычно от 1 до 500 МГц, что соответствует времени такта от 1000 не до 2 не. Частота тактового генератора обычно контролируется кварцевым генератором, чтобы достичь высокой точности.

В компьютере за время одного такта может произойти много событий. Если они должны осуществляться в определенном порядке, то такт следует разделить на подтакты. Чтобы достичь лучшего разрешения, чем у основного тактового генератора, нужно сделать ответвление от задающей линии тактового генератора и вставить схему с определенным временем задержки. Таким образом порождается

Глава 3. Цифровой логический уровень

вторичный сигнал тактового генератора, который сдвинут по фазе относительно первичного (рис. 3.20, а). Временная диаграмма (рис. 3.20, б) обеспечивает четыре начала отсчета времени для дискретных событий:

вторичный сигнал тактового генератора, который сдвинут по фазе относительно первичного (рис. 3.20, а). Временная диаграмма (рис. 3.20, б) обеспечивает четыре начала отсчета времени для дискретных событий:

1. Нарастающий фронт С1.

2. Задний фронт С1.

3. Нарастающий фронт С2.

4. Задний фронт С2.

Связав различные события с различными фронтами, можно достичь требуемой последовательности выполнения действий. Если в пределах одного такта требуется более четырех начал отсчета, можно сделать еще несколько ответвлений от задающей линии с различным временем задержки.

Рис. 3.20. Тактовый генератор (а); временная диаграмма для тактового генератора (б); порождение асинхронных тактовых импульсов (в)

В некоторых схемах важны временные интервалы, а не дискретные моменты времени. Например, некоторое событие может происходить в любое время, когда уровень импульса С1 высокий, а не на нарастающем фронте. Другое событие может происходить только в том случае, когда уровень импульса С2 высокий. Если необходимо более двух интервалов, нужно обеспечить больше линий передачи синхронизирующих импульсов или сделать так, чтобы состояния с высоким уровнем импульса у двух тактовых генераторов частично пересекались во времени. В последнем_случае можно выделить 4 отдельных интервала: СТ И С2, С1 И С2, С1ИС2иС1 ИС2.

Тактовые генераторы могут быть синхронными. В этом случае время состояния с высоким уровнем импульса равно времени состояния с низким уровнем импульса (рис. 3.20, б). Чтобы получить асинхронную серию импульсов, нужно сдвинуть сигнал задающего генератора, используя цепь задержки. Затем нужно

Память

соединить полученный сигнал с изначальным сигналом с помощью логической функции И (см. рис. 3.20, в, сигнал С).

соединить полученный сигнал с изначальным сигналом с помощью логической функции И (см. рис. 3.20, в, сигнал С).

|

Дата добавления: 2013-12-13; Просмотров: 649; Нарушение авторских прав?; Мы поможем в написании вашей работы!