КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Программируемые логические генераторы

|

|

|

|

Лекция 15. Virtex-5, Virtex-5 FXT.

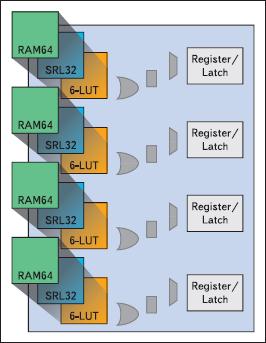

Практически стандартным решением для логического генератора являлась 4-входовая таблица истинности. Ее очевидная реализация — блок памяти 16×1, непосредственно хранящий все возможные варианты состояния выхода в зависимости от комбинаций входных сигналов. Отличительной особенностью FPGA Xilinx является возможность конфигурирования этого блока как обычной синхронной памяти с организацией 16×1, или в виде 16-разрядного сдвигового регистра. Такое решение несколько увеличивает задержки распространения сигналов, и в последних семействах возможностью подобного универсального конфигурирования обладает только половина логических генераторов. Взглянем на рис. 1.

Рис. 1. Структура логической ячейки ПЛИС Virtex-4

Итак, главное изменение более чем кардинально. Логический генератор теперь представляет собой 6-входовую таблицу истинности! Соответственно, она конфигурируется как 32-разрядный сдвиговый регистр или блок памяти с организацией 64×1. То есть добавление новых входов произошло действительно за счет увеличения объема конфигурационной памяти для таблиц истинности (причем в 4 раза!), а не за счет добавления мультиплексоров, что в ряде случаев позволяет получать в пределах логической ячейки устройства комбинаторной логики с числом входов до 8. Однако комбинация «генератор + мультиплексоры» позволяет реализовать не всякую логическую функцию, в отличие от физически увеличенного объема памяти для хранения таблиц истинности.

Значение данного нововведения трудно переоценить. Прежде всего, для сложных проектов существенно уменьшается число последовательно соединяемых логических ячеек, реализующих функцию для большого числа входов. Экономия ячеек при этом не так важна, как важен тот факт, что в цепях комбинаторной логики оказывается в среднем в полтора раза меньше ячеек, что соответственно во столько же раз уменьшает задержку распространения сигнала. Поскольку период тактового сигнала определяется максимальной задержкой внутри кристалла, очевидно, что уменьшение задержки распространения позволяет увеличить тактовую частоту проекта. Разумеется, данный вопрос требует дополнительного исследования и проведения тестов для типичных цифровых узлов, но уже сейчас становится ясно, что имеют место и количественное (65 нм вместо 90), и качественное улучшение (меньшее число последовательно включенных ячеек в цепях распространения сигнала).Что касается увеличения числа входов, то здесь важно обратить внимание на следующий факт. Добавление одного входа увеличивает объем памяти логического генератора в 2 раза. Тем не менее, рост производительности далеко не всегда пропорционален числу входов (многим цифровым узлам достаточно 4 входов), тем более он не пропорционален объему памяти, который возрастает в геометрической прогрессии, а не в арифметической. Соответственно, существует оптимальное число входов, которое при приемлемых затратах на реализацию LUT обеспечивает достаточную их функциональность. Долгое время стандартным значением было 4 входа, и переход к 6 входам заслуживает самого пристального внимания. Достаточно сравнить такое решение, к примеру, с 5-входовыми таблицами истинности, которые требуют в 2 раза меньше памяти, но имеют всего на один вход меньше. Насколько значимым окажется выигрыш от добавления одного входа? Будут ли цифровые узлы, в полной мере задействующие возможности новых ПЛИС, достаточно эффективными и востребованными в практических проектах, чтобы 6-входовые таблицы истинности оправдали свое применение? Можно подчеркнуть, однако, что серия Virtex в последнее время концентрирует в себе наиболее производительные решения в области цифровой схемотехники и системной архитектуры, поэтому решение конструкторов Xilinx остановиться именно на 6-входовых LUT вполне оправданно. Кроме того, FPGA состоит не только из конфигурационной памяти таблиц истинности, поэтому удельный вес дополнительных ресурсов в конечном итоге не так уж велик. Достаточно посмотреть на соотношение распределенной памяти (ее объем соответствует значениям, хранящимся в LUT) и общего объема конфигурационного потока, загружаемого в ПЛИС. Нетрудно убедиться, что «учетверение» коснулось относительно небольшого участка кристалла.

|

|

|

|

|

|

Какие конкретно выгоды получает разработчик от 6-входовой LUT? Обратим внимание на то, что базовая организация блочной памяти соответствует 18-разрядным данным. Такую же разрядность входных операндов имеют и выделенные умножители современных FPGA. Соответственно, программируемые логические ресурсы часто решают задачи управления высокопроизводительными блоками DSP путем формирования вспомогательных сигналов, включающих и выключающих счет, переключающих режимы и т. п. Часто это происходит именно на основании анализа значений операндов, циркулирующих в блочных ресурсах. Итого, для вычисления некоторой логической функции от 18-разрядного числа требуется не менее пяти 4-входовых LUT, или всего три 6-входовых! Для сравнения: три 5-входовые LUT имеют только 15 входов. Таким образом, новая организация логических генераторов вполне обоснована. К этому можно добавить, что для объединения выходов пяти 4-входовых LUT в общем случае недостаточно еще одной 4-входовой ячейки (!), и в ряде случаев это может приводить к формированию чрезмерно длинных цепочек из логических ячеек и цепей трассировки. Данная проблема не фатальна (к тому же в большинстве случаев САПР удается решить задачу объединения выходов LUT с помощью встроенных мультиплексоров логических ячеек), но тем не менее 6-входовые LUT даже формально могут сформировать результат вычисления комбинаторного выражения с помощью меньшего числа уровней.

Работа с семейством Virtex-5 стала возможной в САПР ISE 8.2, которая уже выпущена (несмотря на то, что сами ПЛИС пока недоступны). Для иллюстрации рассуждений, приведенных выше, рассмотрим пример реализации 18-разрядного компаратора двоичного значения (устройство, выдающее на выходе логическую единицу, если комбинация на входе равна некоторой константе). Подобные устройства достаточно характерны для целого ряда цифровых устройств, в том числе для цифровой обработки сигналов и конфигурируемых процессоров. Оба этих класса устройств способны эффективно использовать 18-разрядную память, и уменьшение задержек при операциях с числами такой разрядности весьма положительно сказывается на их характеристиках.

|

|

|

Итак, тестирование 18-разрядного устройства сравнения с константой дает предсказуемые результаты: ПЛИС Virtex-4 требует для его реализации 6 LUT, тогда как Virtex-5 — всего 4. Кроме того, задержка распространения сигнала (maximum pin delay) также существенно уменьшилась: с более чем 3 нс у Virtex-4 до 1,075 нс у Virtex-5. Как уже отмечалось, этот эффект достигается не только за счет экстенсивных мер (перехода к 65-нанометровому техпроцессу), но и за счет более компактной реализации логических функций. Тестирование возможностей Virtex-5 в более сложных проектах с большим числом сложных логических выражений также подтверждает, что наблюдается 25–30%-ное уменьшение числа логических уровней.

На рис. 2 проиллюстрирована проблема, связанная с увеличением числа уровней логики. Показано распространение сигнала от выхода первого триггера к входу второго. При этом сигнал последовательно проходит через 2 LUT, получая в каждой задержку tπ. Кроме того, при прохождении по трассировочным цепям добавляется задержка tтр. Чем большее число LUT будет вовлечено в процесс обработки, тем больше времени придется выделить на распространение сигнала до входа следующего триггера. Время распространения сигнала в самой длинной цепи определяет минимально допустимый период тактового сигнала, следовательно, даже для ПЛИС с высокой максимальной тактовой частотой возможна ситуация, когда слишком сложные логические выражения приведут к использованию большого числа последовательно соединяемых LUT, что сильно снизит реальную частоту проекта.

|

|

|

Рис. 2. Иллюстрация к проблеме увеличения числа уровней логики

Можно также обратить внимание на материалы сайта Xilinx, иллюстрирующие переход к памяти, состоящей из 64 ячеек вместо 16. Для предыдущих семейств требовалось 4 блока, объединяемых к тому же двумя уровнями мультиплексоров (что вносило дополнительную задержку и вызывало необходимость использования дополнительных мультиплексоров). В семействе Virtex-5 блок памяти 64×1 реализуется в единственной LUT, что исключает проблемы, связанные с объединением блоков. Таким образом, «минимальный размер» распределенной памяти увеличился ровно в 4 раза.

Схемы секций семейств Virtex-4 представлены соответственно на и 4. Для Virtex-4 показаны верхние секции и часть общей логики. Назначение этих рисунков — продемонстрировать общую схожесть архитектуры семейства ПЛИС.

Рис. 4. Схема секции ПЛИС Virtex 4

|

|

|

|

Дата добавления: 2014-01-07; Просмотров: 397; Нарушение авторских прав?; Мы поможем в написании вашей работы!