КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Регистры процессора

|

|

|

|

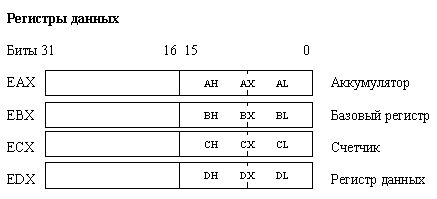

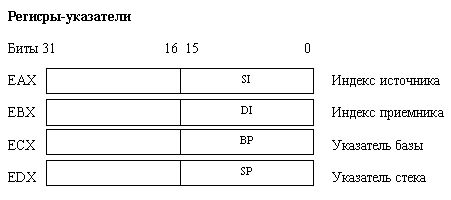

Рис. Основные регистры 32-разрядных процессоров.

Как видно из рис. 4.1, регистры общего назначения и регистры-указатели отличаются от аналогичных регистров МП 86 тем, что они являются 32-разрядными. Соответственно, к их мнемоническим обозначениям добавлена буква Е (от extended, расширенный).

Для сохранения совместимости с ранними моделями процессоров допускается обращение к младшим половинам всех регистров, которые имеют те же мнемонические обозначения, что и в МП 86 (АХ, ВХ,СХ, DX, SI, DI, ВР и SP). Естественно, сохранена возможность работы с младшими (AL, BL, CL и DL) и старшими (АН, ВН, СН и DH) половинками регистров МП 86. Однако старшие половины 32-разрядных регистров не имеют мнемонических обозначений и непосредственно недоступны. Для того, чтобы прочитать, например, содержимое старшей половины регистра ЕАХ (биты 31...16) придется сдвинуть все содержимое ЕАХ на 16 бит вправо (в регистр АХ) и прочитать затем содержимое АХ. Все регистры общего назначения и указатели программист может использовать по своему усмотрению для временного хранения адресов и данных размером от байта до двойного слова. Так, например, возможно использование следующих команд:

mov ЕАХ,0FFFFFFFFh;Работа с двойным словом (32 бит)

mov AX,0FFFFh;Работа со словом (16 бит)

mov AL, 0FFh;Работа с байтом (8 бит)

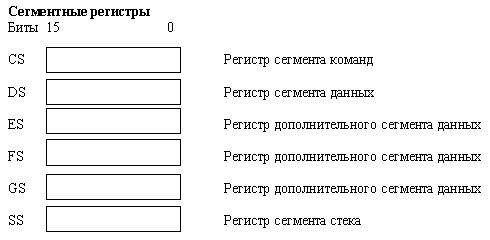

Все сегментные регистры, как и в МП 86, являются 16-разрядными. В их состав включено еще два регистра - FS и GS, которые могут использоваться для хранения сегментных адресов двух дополнительных сегментов данных. Таким образом, при использовании расширенных возможностей современных процессоров программе одновременно доступны четыре сегмента данных, а не два, как в МП 86.

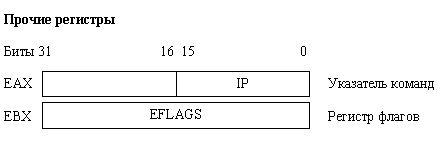

Регистр указателя команд также является 32-разрядным и обычно при описании процессора его называют EIP. Младшие шестнадцать разрядов этого регистра соответствуют регистру IP процессора МП 86. Весь регистр EIP используется только в 32-разрядных приложениях; в 16-разрядных программах адреса могут быть только 16-разрядными и, соответственно, для адресации в программном сегменте используется младшая половина регистра EIP.

Регистр флагов принято называть EFLAGS (от extended flags, расширенные флаги). Хотя он имеет длину 32 бит, только младшие 18 бит (да и то не все) содержат значащую информацию. Дополнительно к шести флагам состояния (CF, PF, AF, ZF, SF и OF) и трем флагам управления состоянием процессора (TF, IF и DF), назначение которых было описано в гл. 1, он включает новые флаги задачи, рестарта и виртуального режима, а также двухбайтовое поле привилегий ввода-вывода. Все эти биты используются только в защищенном режиме и здесь рассматриваться не будут.

3.3. Адресация в защищённом режиме МП80386

В защищённом режиме для управления памятью микропроцессор использует дополнительные «внешние» данные. Эти данные располагаются в памяти. Поэтому процессоры Intel начиная с 808386, после включения питания запускаются в реальном, а не в защищённом режиме. Системное программное обеспечение перед переключением МП в защищённый режим размещает в памяти и инициализирует все необходимые структуры данных. Ссылки на эти структуры помещаются в специальные служебные регистры МП. После этих подготовительных операций МП переключается в защищённый режим.

Сегменты и схема вычисления виртуального адреса.

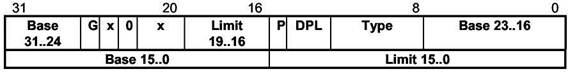

С «точки зрения» процессора память это набор блоков, которые называются сегментами. Следует отметить, что в реальном режиме СЕГМЕНТом называется параметр в формуле вычисления адреса. В защищённом режиме термин сегмент просто имеет другой смысл. Сегменты могут размещаться в любом месте 32-х разрядного адресного пространства процессора и могут иметь размеры до 4ГБ. Диапазоны адресов сегментов могут перекрываться. Характеристики каждого сегмента описываются в структуре, которая называется дескриптор сегмента. Дескриптор содержит начальный адрес сегмента, размер (limit), информацию о типе,

уровне привилегий и других атрибутах сегмента. Упрощённый формат дескриптора приведён на рисунке 1. Следует отметить, что дескрипторы используются не только для описания сегментов содержащих код, данные или стеки программ. Некоторые системные структуры, как например, локальные дескрипторные таблицы и шлюзы так же описываются дескрипторами. Форматы дескрипторов различных типов могут отличаться.

Base 32-х битовый базовый адрес сегмента.

Limit Размер сегмента в байтах или страницах (зависит от значения бита G).

G Гранулярность. Если G = 0 Limit указан в байтах, иначе в страницах (Размер

страницы 4096 байт).

Туре тип дескриптора.

DPL Уровень привилегий дескриптора.

Р бит присутствия.

Рисунок 1. Формат дескриптора.

Дескрипторы размешаются во внешней памяти в нескольких системных таблицах. Операционная система должна создать и проинициализировать некоторые из этих таблиц перед переключением МП в защищённый режим. ОС, по крайней мере, должна создать Глобальную дескрипторную таблицу (GDT) с одним или несколькими дескрипторами сегментов содержащих системный код, данные и стек. Кроме этого следует создать Дескрипторную таблицу прерываний (IDT) которая содержит дескрипторы обработчиков прерываний. Во время работы МП в защищённом режиме дескрипторы могут модифицироваться удаляться и добавляться. Обычно операционная система создаёт одну таблицу GDT и одну таблицу IDT. Дополнительно система может создать одну или несколько Локальных дескрипторных таблиц (LDT). Каждая такая таблица выделяется для дескрипторов сегментов отдельной пользовательской программы. Такой способ используется для защиты программ друг от друга. Адреса и размеры таблиц записываются в служебные регистры микропроцессора. В регистр GDTR заносится адрес GDT, в регистр IDTR адрес IDT и в регистр LDTR адрес текущей LDT. Содержимое регистра LDTR изменяется каждый раз, когда операционная система выделяет время для исполнения очередной программы. Сегментные регистры процессора используются для ссылки на дескриптор в одной из дескрипторных таблиц. Содержимое сегментного регистра называется селектором. Селектор содержит номер дескриптора в таблице и флаг, по которому определяется в какой из таблиц LDT или GDT расположен дескриптор. Кроме этого в селекторе указываются атрибуты защиты. 13 старших разрядов занимает номер дескриптора. Следовательно, каждая таблица может содержать до 2 3 = 8K дескрипторов. Бит 2 (считая с нуля) определяет таблицу, и два младших бита используются в механизме защиты памяти (Рисунок 2).

Index номер дескриптора в таблице.

TI выбор таблицы. Если TI = 0 используется GDT иначе LDT.

RPL запрашиваемый уровень привилегий.

Рисунок 2. Формат селектора.

При обращении к сегменту памяти процессор дополнительно должен считать содержимое дескриптора этого сегмента. Такой способ обмена данными с памятью может существенно снизить производительность работы системы. Однако в действительности при обращении к памяти чтение дескриптора не производится. Микропроцессор имеет так называемые теневые сегментные регистры, в которых сохраняются дескрипторы сегментов. Для каждого сегментного регистра имеется теневой регистр. Теневой регистр содержит дескриптор, на который указывает селектор, записанный в сегментном регистре. Дескриптор записывается в теневой регистр, при изменении содержимого сегментного регистра. Эта технология особенно эффективна при работе с так называемой плоской моделью памяти. В такой модели используется единственный сегмент, перекрывающий всё адресное пространство. Так как вся память доступна через этот единственный сегмент, во время работы нет необходимости изменять значение сегментных регистров.

Рассмотрим процедуру вычисления адреса в защищённом режиме на примере исполнения инструкции чтения памяти MOV AL, [EDI]. Эта инструкция считывает в регистр AL байт из ячейки памяти, адрес которой вычисляется по схеме изображённой на рисунке 3.

Рисунок 3. Схема вычисления виртуального адреса в защищённом режиме.

Заключение – до 5 мин.

Лекция разработана «___»________20__г.

_______________________(___________)

(подпись, фамилия и инициалы автора)

|

|

|

|

|

Дата добавления: 2014-01-07; Просмотров: 848; Нарушение авторских прав?; Мы поможем в написании вашей работы!