КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Триггеры

|

|

|

|

Триггер является элементом, который может находиться в одном из двух устойчивых состояний. Одному из этих состояний приписывается значение 1, а другому —0. Состояние триггера распознается по его выходному сигналу. Под влиянием входного сигнала триггер скачкообразно переходит из одного устойчивого состояния в другое, при этом скачкообразно изменяется уровень напряжения его выходного сигнала.

Для удобства использования в схемах вычислительных устройств триггеры обычно имеют два выхода: прямой Q (называется также «выход 1») и инверсный Q («выход О»). В единичном состоянии триггера на выходе Q высокий уровень сигнала, а в нулевом — низкий. На выходе Q наоборот.

В интегральных системах элементов триггер и схема, управляющая его входами («входная логика»), выполняются на одной кремниевой пластине, заключенной в корпус с выводами. При этом на одной пластине (в одном корпусе) может находиться несколько триггеров.

Схемы триггеров можно разделить на несколько типов: с установочными входами — RS-триггер, со счетным входом — Т-триггер, а также D-триггер, JK-триггер и др.

Если хотя бы с одного входа информация в триггер заносится принудительно под воздействием синхронизирующего сигнала, то триггер называется синхронизируемым (синхронным). Если занесение информации в триггер с любого входа производится без синхронизирующего сигнала, то триггер называется не синхронизируемым (асинхронным).

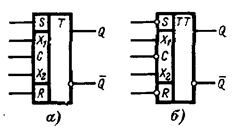

Общая форма условного обозначения триггеров показана на рис. 2.6. В основном поле ставится символ Т или символ ТТ для обозначения соответственно однотактного или двухтактного триггера. Дополнительное поле может быть разделено на две части: асинхронную и синхронную. В первой проставляются символы R и S входов несинхронизируемой установки триггера в 1 и 0, во второй — на местах X1 и Х2 символы в соответствии с типом триггера. При этом пользуются следующими обозначениями для входов:

|

|

|

S — вход установки триггера в 1;

R — вход установки триггера в 0;

Т — вход триггера со счетным входом;

D — вход D-триггера;

J — вход для синхронизируемой установки состояния 1 в JK-триггере;

К — вход для синхронизируемой установки состояния 0 в JK-триггере;

С — вход синхронизации.

Рис. 2.6. Условные обозначения интегральных триггеров:

а - синхронизируемый однотактный триггер с дополнительными входами Х и R несинхронизируемой установки; б - синхронизируемый двухтактный триггер с дополнительными входами S и R несинхронизируемой установки

Если вход отмечен кружком, это означает, что действующее значение входного сигнала —0. Например, отсутствие кружка на входе С на рис. 2.6, а указывает на то, что входная информация заносится в триггер при единичном значении синхронизирующего сигнала (действующее значение синхронизирующего сигнала равно 1); кружок на входе С (рис. 2.6, б) означает, что прием информации происходит при нулевом значении синхронизирующего сигнала (действующее значение синхронизирующего сигнала равно 0). Состояние триггера определяется сигналом Q на прямом выходе триггера (или сигналом Q на его инверсном выходе).

Законы функционирования триггеров задаются таблицами переходов с компактной записью, при которой в столбце состояний может быть указано, что новое состояние совпадает с предыдущим либо является его отрицанием.

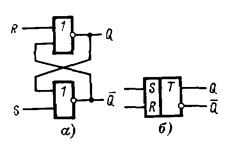

Асинхронный RS-триггер. Асинхронный (несинхронизируемый) RS- триггер на интегральных элементах ИЛИ — НЕ показан на рис. 2.7. Триггер образован из двух комбинационных схем ИЛИ — НЕ, соединенных таким образом, что возникают положительные обратные связи, •благодаря которым в устойчивом состоянии выходной транзистор одной схемы ИЛИ — НЕ закрыт, а у другой открыт..

|

|

|

Рис. 2.7. Асинхронный RS-триггер на элементах ИЛИ-НЕ:

а — функциональная схема; б — условное обозначение

Таблица переходов, определяющая закон функционирования этого триггера приведена ниже

Таблица 2.1. Таблица переходов асинхронного.RS-триггера на элементах ИЛИ — НЕ,

| R | S | Q | Примечание |

| Q | Хранение | ||

| Установка 1 | |||

| Установка 0 | |||

| - | Запрещено |

При R = 1 и S =0 триггер устанавливается в нулевое состояние Q = 0; при R = О и S = 1 он устанавливается в единичное состояние Q = 1; при R = S = 0 триггер сохраняет состояние, в котором он находился до момента поступления на его входы нулевых сигналов. При R= S = 1 на прямом и инверсном выходах устанавливается нулевой сигнал. Триггерное кольцо превращается в два независимых инвертора, и при переходе к хранению (R = S = 0) триггер может устанавливаться в любое состояние. Поэтому такая комбинация входных сигналов запрещена.

Функционирование RS-триггера можно описать выражением

Q{t+i)=S(t) v Q{t)R{t), (2.5)

причем S {t) R (t) = 0, a t- момент времени, предшествующий смене состояния.

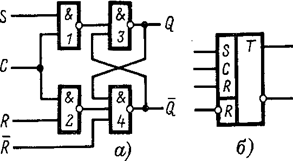

Синхронизируемый однотактный RS-триггер. На рис. 2.8 приведена схема синхронизируемого однотактного RS-триггера на элементах И — НЕ. Здесь элементы 1 и 2 образуют схему входной логики асинхронного RS-триггера, построенного на элементах 3 и 4. Такие RS- триггеры имеют два информационных входа R и S и вход синхронизации С. Кроме того, триггер может иметь несинхронизируемые входы R и S. В этом случае функционирование триггера осуществляется либо под воздействием несинхронизируемых входов при С = 0, либо под воздействием синхронизируемых входов. В последнем случае яа несинхронизируемых входах должны присутствовать сигналы, которые

не влияют на состояние схемы

.

Рис. 2.8. Синхронизируемый одно-тактный RS-триггер на элементах И-НЕ:

а — функциональная схема; б — условное обозначение

Таблица 2.2 определяет переходы RS-триггера, построенного на элементах И — НЕ, для синхронизируемых входов R и S. Работа в соответствии с данной таблицей осуществляется при сигнале несинхронизируемого входа R = 1 и при С = 1.

|

|

|

Таблица 2.2. Таблица переходов синхронизируемого одиотактного RS- триггера на элементах И—НЕ

| R | S | Q | Примечание |

| Q | Хранение | ||

| Установка 1 | |||

| Установка 0 | |||

| - | Запрещено |

Входная информация, представленная в парафазном коде, заносится в синхронизируемый однотактный RS-триггер через элементы входной логики 1 и 2 в момент поступления сигнала синхронизации С. В отсутствие сигнала синхронизации триггер может быть установлен в состоянии 0 путем подачи на несинхронизируемый вход R сигнала R=0.

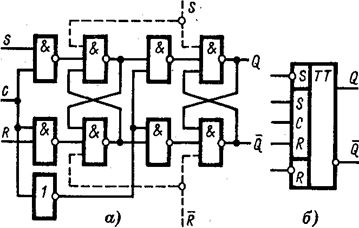

Двухтактный RS-триггер. Устойчивая работа одноактных RS-триггеров в схеме с передачей информации между триггерами возможна только в случае, если занесение в триггер информации осуществляется после завершения передачи информации о прежнем его состоянии в другой триггер. Это достаточно просто обеспечивается при использовании двух серий находящихся в противофазе синхросигналов.

Рис. 2.9. Двухтактный RS- триггер на элементах И-НЕ:

а — функциональная схема; б — условное обозначение

Такой принцип обмена информацией реализован в двухтактных RS-триггерах.Простейшая схема двухвходового двухтактного RS-триггера показана на рис. 2.9. Она состоит из двух однотактных RS-триггеров и инвертора в цепи синхронизации. При поступлении на вход RS-триггера сигнала С = 1 входная информация заносится в первый однотактный RS-триггер, а второй при этом будет хранить информацию, относящуюся к предыдущему периоду представления. По окончании действия сигнала синхронизации, когда С = О, а С = 1, первый RS-триггер перейдет в режим хранения, а второй примет то же состояние, что и первый. В результате к следующему такту на выходе двухтактного RS-триггера появится сигнал нового состояния. Таблица 3.3 задает закон функционирования такого двухтактного триггера. Такты t здесь задаются интервалами времени, в которые С = 1. Двухтактный триггер изменяет свои состояния только после окончания действия сигнала синхронизации С = 1 (переход в режим хранения информации). Поэтому из двухтактных триггеров можно строить произвольные схемы, в том числе подавать сигналы с выхода триггера на его вход.

|

|

|

Для установки триггера в состояние 0 или 1 без использования синхросигналов в схему вводят дополнительные входы R и S несинхронизируемой установки. Связи с этими входами показаны на рис. 3.9, а пунктиром. При подаче 0 на вход R (S) и 1 на вход S (R) оба однотактных триггера устанавливаются в состояние 0(1).

При подаче 1 на оба этих входа работа триггера осуществляется в соответствии с табл. 2.3.

Схема.RS-триггеров составляет основу для построения других триггерных схем, таких, как Т-, D- и JК-триггеры.

Таблица 2.3. Таблица переходов двухтактного RS-триггера на элементах И—НЕ

| t | t+1 | Прмечание | |

| R | S | Q | |

| 0 | Q(t) | Хранение | |

| Установка 0 | |||

| Установка 1 | |||

| — | Запрещено |

Т-триггер. Триггер со счетным входом (Т-триггер) в простейшем случае может быть построен с использованием двухтактного синхронизируемого RS-триггера. Т-триггер должен реализовать функцию вида

Q(t + 1) = Q(t)T(t) v Q(t)T(t). (2.6)

Простейшая схема несинхронизируемого Т-триггера представлена на рис. 2.10,а. В этой схеме поступление сигнала Т= 1 приводит к записи в двухступенчатый RS-триггер состояния, противоположного ранее хранимому. При этом, так как триггер двухступенчатый, на его выходе сигнал изменится только по завершению действия сигнала Т = 1, что исключает возникновение генерации в схеме с обратной связью. Можно считать, что в данной схеме единичный входной сигнал

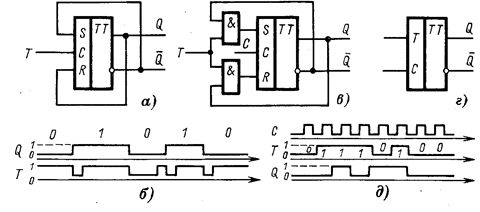

Рис. 2.10. T-триггер:

а—несинхронизируемый T-триггер; б—временная диаграмма работы несинхронизируемого T-триггера; в — синхронизируемый T-триггер; г — условное обозначение синхронизируемого Т-триггера; д — временная диаграмма работы синхронизируемого Т-триггера

Представляется спадом сигнала Т = 1, так как при любой продолжительности сигнала Т = 1 изменение состояния Т-триггера происходит только один раз - при снятии сигнала Т= 1 (рис. 2.10,6).

При необходимости представлять потенциалом последовательность единиц на входе Т-триггера используется синхронизируемая схема (рис.2.10,в, г). Здесь единичный входной сигнал представляется высоким уровнем сигнала Т при С = 1. Поэтому высоким уровнем сигнала Г можно представить последовательность 1 (рис. 2.10,д). Запись в триггер происходит при С = 1, причем смена состояния происходит после окончания действия сигнала синхронизации С==1. При Т= 1 состояние триггера изменяется на противоположное, а при-Г=0 состояние триггера не меняется. Временная диаграмма, поясняющая работу синхронизируемого Г-триггера, показана на рис. 2.10,д).

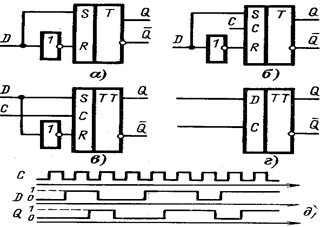

D-триггер. Одним из самых широко употребляемых триггеров является интегральный D-триггер, который реализует функцию временной задержки. D-триггер имеет только режимы установки 1 и О, В связи с этим несинхронизируемый D-триггер (рис. 2.11, в) не применяется, так как его выход будет просто повторять входной сигнал. Синхронизируемый однотактный D-триггер (рис. 2.11,6) задерживает распространение входного сигнала на время паузы между синхросигналами (задержка на полпериода). Для задержки на период (на один такт) используется двухтактный D-триггер.

Вариант построения двухтактного D-триггера показан на рис. 2.11, в. Под действием синхросигнала информация, поступающая на выход D, принимается в RS-триггер, но на выходе Q появляется с задержкой на такт:

Q{t+l)=D{t). (2.7)

Рис. 2.11. D-триггер:

a — несинхронизируемый D-триггер; б— синхронизируемый однотактный.D-триггер; в — двухтактный D-триггер; г — условное обозначение двухтактного D-триггера; д — временная диаграмма работы двухтактного D-триггера JK-триггер.

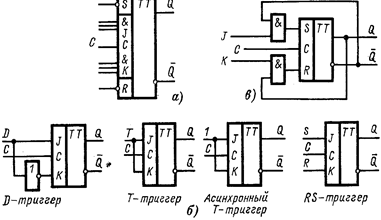

Распространенным типом триггера в системах интегральных логических элементов является двухтактный JX-триггер, условное обозначение которого показано на рис. 2.12,a.

У рассматриваемого триггера имеются входы несинхронизируемой установки R и S, с помощью которых при С = 0 триггер может быть установлен в состояние 1 путем подачи R = 1 и S=0 либо в состояние 0 путем подачи R = 0 и S = 1.

Рис. 2.12. JK-триггер:

а—условное обозначение двухтактного.JK-триггера;

б—способы использования JK-триггера; в — схема JK-триггера

При подаче сигналов R == S = 1, не меняющих состояние схемы, работа триггера осуществляется под воздействием синхронизируемых входов. В этом случае функционирование триггера может быть описано табл. 2.4, причем такты t здесь, как и ранее, задаются сигналом С= 1.

Таблица 2.4. Таблица переходов JK-триггера

| t | t+1 | Примечание | |

| R | S | Q | |

| 0 | Q(t) | Хранение | |

| Установка 0 | |||

| Установка 1 | |||

| Q(t) | Инверсия |

Здесь J=J1J2J3 и К=К1К2К3. Входы J и К соответствуют входам установки в 1 ив 0 триггера. Однако в отличие от RS-триггера в JK-триггере сигналы 1 могут одновременно прийти на входы J и К. При этом состояние триггера изменяется на противоположное, т. е. при J = К схема ведет себя как триггер со счетным входом. Функцию переходов JK-триггера можно представить в виде булевой функции: Q(t + 1) =K(t)Q(t) v J(t)Q(t) (2.8) при условии, что RS=1. JK-триггер удобен тем, что при различных вариантах подключения его входов можно получить схемы, функционирующие как RS-, D- и Т-триггеры (рис. 2.12,6). Вариант построения схемы JX-триггера дан на рис. 2.12, в.

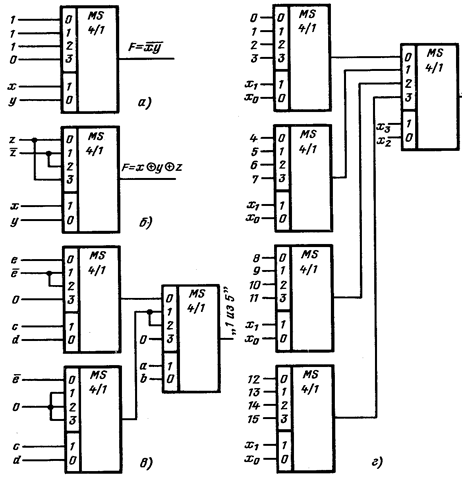

Рис 2.19. Схемы из мультиплексоров:

а-И-НЕ; б-сложение по модулю 2; в-двухкаскадное мультиплексирование; г - многокаскадный мультиплексор

.

|

|

|

|

|

Дата добавления: 2015-05-09; Просмотров: 2005; Нарушение авторских прав?; Мы поможем в написании вашей работы!