КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

I. Логические элементы

|

|

|

|

В основу всех логических операций положены три элементарные логические операции: отрицание, умножение, сложение.

Для реализации этих операций посредством логических элементов используют электрические сигналы, представленные двумя уровнями: высоким и низким.

В работе исследуют ТТЛ-элементы, для которых уровень логической единицы применяют высоким H(high). Он кодируется напряжением в пределах от 3,6 до 5В. Уровень логического нуля принят низким L(Low) и кодируется напряжением в пределах от 0 до 0,4 В.

Логическое отрицание НЕ(инверсия) подразумевает формирование на выходе логического элемента – инвертора – сигнала y, противоположного по уровню входному. Следовательно, если на вход инвертора подать сигнал логической I, то на выходе будет логический 0 и наоборот. Логическое отрицание обозначают в логических выражениях чертой над инвертируемым сигналом  Условные обозначение и передача сигналов инвертором приведены в табл. I.

Условные обозначение и передача сигналов инвертором приведены в табл. I.

Таблица I

Элементарные логические операции

| Операция | Реализуемая функция | Реализующее устройство | ||||||||

| Наименование | Обозначение | Обозначение | Передача сигналов | |||||||

|

| y | ||||||||

| НЕ | Инверсия |

|  x y x y

| - - | ||||||

| И | Конъюнкция |

|

X1

| |||||||

| ИЛИ | Дизъюнкция |

|

X1

|

Логические умножение И(конъюкция) подразумевает формирование на выходе элемента – конъюнктора – сигнала уровня логической I при наличии на всех входах сигналов логической I. Если хотя бы на одном входе будет сигнал логического 0. Операцию логического умножения, например при двух входных сигналах  и

и  , обозначают выражением

, обозначают выражением  . Условное обозначение и передача сигналов конъюнктором приведены в табл. I.

. Условное обозначение и передача сигналов конъюнктором приведены в табл. I.

При логическом сложении ИЛИ(дизъюнкции) происходит формирование на выходе элемента – дизъюнктора сигнала уровня логической I, если хотя бы один из входных сигналов имеет уровень логической I. Операцию логического сложения, например при двух входных сигналах  и

и  , обозначают выражением

, обозначают выражением  . Условное обозначение и передача сигналов дизъюнктором приведены в табл. I.

. Условное обозначение и передача сигналов дизъюнктором приведены в табл. I.

Достаточно развитыми по номенклатуре являются универсальные микросхемы ТТЛ 155-й серии. Они являются изделиями массового применения, обладают высокой стойкостью к климатическим и механическим воздействиям.

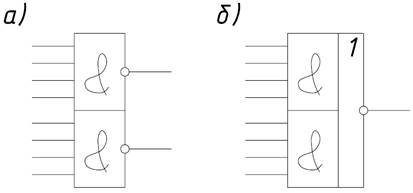

С целью упрощения схемной реализации и придания свойств универсальности логическим элементам при разработке микромодулей выполнено сочетание операций конъюнкции и дизъюнкции с операцией инверсии. Например, микросхема 155ЛА6 реализует операции 2 х 4И – НЕ, микросхема 155ЛР4 – 4И – НЕ. Функциональные схемы этих элементов показаны на рис. I, а, б.

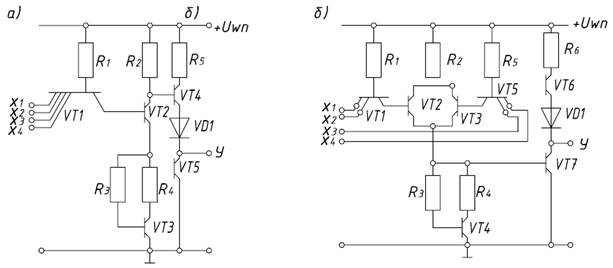

На рис. 2, а показана эквивалентная схема одного элемента модуля 155ЛА6.

Схема элемента содержит три каскада: входной (транзистор VT1 и резистор R1), фазоращепительный (транзистор VT2 и резистор R2, а также транзистор VT3 и резисторы R3, R4) выходной (транзисторы VT4, VT5, диод VD5).

Когда один или несколько входов соединены с общей шиной микросхемы непосредственно или через выходной транзистор предыдущего каскада, соответствующий эмиттерный переход транзистора VT1 смещен в прямом направлении, поскольку потенциал базы выше потенциала эмиттера. Транзистор VT2 будет заперт.

Если второй каскад (транзистор VT2) заперт, ток, протекающий по резистору №2 и базо-эмиттерному переходу транзистора VT4 и диода VD1. Уровень сигнала в этом случае составляет примерно 3,6 В и соответствует логической I. транзистор VT3 служит для повышения помехоустойчивости микросхемы.

Когда на все входы действует напряжение высокого уровня (логической I), эмиттерный переход транзистора VT1смещен в обратном направлении, а коллекторный – в прямом. Коллекторный ток транзистора VT1 отпирает транзисторы VT2 и VT5. Выходное напряжение представляет собой падение напряжения на эмиттер-коллекторном переходе транзистора VT5, оно составляет около 0,4 В и соответствует уровню логического 0.

Схема логического элемента ИЛИ НЕ образуется путем подключения параллельно транзистору VT2 аналогичной схемы со своими входными каскадами (транзистор VT3 на рис. 2, б).

Рис. 1

При разработке схемы цифрового устройства из микросхем неиспользуемые входы надо объединять с учетом выполняемых данным элементом функций. В тех случаях, когда на неиспользуемых входах должен быть уровень логического 0, их надо соединять с общей шиной источника питания. Неиспользуемые входы, на которых должна быть постоянно логическая I, допускается оставлять свободными, однако это снижает помехоустойчивость микросхем. Таким образом, неиспользуемые входы дизъюнктора надо обязательно соединять с общей шиной, неиспользованные входы конъюнктора надо обязательно соединять с общей шиной, неиспользованные входы конъюнктора допускается оставлять свободными.

Рис. 2

|

|

|

|

|

Дата добавления: 2015-05-09; Просмотров: 998; Нарушение авторских прав?; Мы поможем в написании вашей работы!

y

y X2

X2

Y y

Y y