КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Контроллер прерываний

|

|

|

|

Память

Эти процессоры содержат внутреннюю память и позволяют работать с разными типами внешней памяти.

Внутренняя

Внешняя

SDRAM до 128 Мб (синхронное динамическое ОЗУ)

Асинхронный SRAM до 4 Мб

ВШД 16 бит

Можно подключить разные типы флеш-памяти. Регистры внутренних и внешних устройств находятся в общем адресном пространстве.

Уровней запроса прерывания – 16.

Источников запроса ≈ 30.

CEC

Номер прерывания влияет на порядок обработки прерываний при одновременности событий.

Приоритет также влияет на возможность прерывания обработчика с более низким приоритетом, если вложенные … разрешены.

Нулевой уровень (EMU) в прерывании от JTAG.

Уровни 1 и 2 обычно соединены со сторожевым таймером (внешним выводом).

Большинство прерываний можно замаскировать.

Уровень 3 (EVX):

· некорректный код инструкции;

· обращение к невыравненным данным.

Прерывания общего назначения могут коммутироваться с различными внутренними и внешними устройствами, один и тот же запрос могут сгенерировать несколько разных устройств. Обработчик прерывания уточняет по содержанию спец. регистра, какое устройство его вызвало

28. Представитель семейства ЦСП Analog Devices: BF531/532/533 – блок схема процессора, контроллер ПДП, часы реального времени, сторожевой таймер, таймеры общего назначения, SPORT, SPI, UART, PPI, GPIO, управление питанием и коэффициентом умножения частоты.

Блок схема процессора.

RTC – Real Time Clock

PPI – Parallel peripheral Interface

GPIO – General purpose Input/Output

SPI – Serial Peripheral Interface

UART – Universal Asynchronous Receiver/Transmitter

SPORT – Serial Port

ПДП (DMA – Direct Memory Access).

Одна из часто встречающихся задач- пересылка, больших объёмов данных между различными устройствами.

Если осуществляется отображение на экране ТВ или монитора требуется регулярная пересылка видеоданных из буфера данных к видео ЦАПу. Аналогично с выводом звука.

|

|

|

1D, 2D

720х576

704х576

3 варианта организации пересылок:

1)Однократные

2)Повторяющиеся

3)По списку

Передачи с использованием прямого доступа к памяти поддерживают все блоки Blackfin, за исключением сторожевого таймера, таймеров общего назначения и часов реального времени.

Часы реального времени.

Счётчики часов, мин., сек., дней. 0 – 32767. 2 будильника: 1 на время дня, другой на определенный день. Будильники, если они активны, генерируют прерывание.

Сторожевой таймер - 32х битный счётчик, если он активен, то по окончанию счёта генерирует прерывания. Служит для предохранения автономных систем от зависания.

Таймер общего назначения – 32х битный, 3 режима работы:

1)ШИМ – выходной режим;

2)Режим измерения периода длит-ти импулься.

3)Режим счёта событий.

1.SPORT 0-1 (интерфейс).

8 сигналов: 4 данных, 4 синхронизации. Вх/вых – 2 канала. Всего 4 шт.

Синхроимп-с:

Первый - имп-с приёма, второй - имп-с передачи, третий – кадров-я синхронизация приёма, четвёртый - кадров-я синхронизация передачи.

Кадр-ый синхримп-с отделяет слово. Можно использовать как интерфейс общего назначения, но в основном ориентирован на передачу аудиоданных по протоколу I2S. Он служит для соединения аудиомикросхем внутри устройства. Используется АЦП иЦАП с последовательным интерфейсом, аудиокодек (АЦП+ЦАП+фильтр), приёмо-передатчики аудиоданных.

Контроллер SPORT в проц-ре Blackfin поддерживает кодир-е по А- и μ-закону.

2.SPI (интерфейс синхронный). Основное отличие от SPORT – шинная организация, а SPORT это точка-точка.

2сигнала данных: MISO, MOSI.

1) Синхросигнал; 2) Сигнал выбора.

Можно подключить АЦП и ЦАП, интерфейсные аудиомикросхемы, другие процессоры и микроконтроллеры, FLASH память, ЖК-индикаторы, ПЛИС.

3.UART (интерефейс несинхронный). Аналог комп-го сот-порта.

|

|

|

Аппаратно поддерживается только приём и передачи. При необходимости поддержание других сигналов интерфейса RS-232С их нужно обработать программно через свободные выводы GPIO. Поддерж-ся протокол передачи IrDA для устройств с ИК интерфейсом.

4.PPI – параллельный периферийный интерфейс.

Полудуплекс параллельный порт, поддерж-щий приём и передачу данных, разрядностью до 16 бит. В состав интерфейса также входит 3 сигнала синхронизации, основное назначение которых – работа с видеосинхроимп-ми. 20й сигнал - вход тактовой синхронизации. В отличии от послед-ых интерфейсов невозможно синхронизировать от внутр-го устр-ва. Важная особенность PPI поддержка стандартов видеоданных ITU-R 656. Интерфейс при необходимости позволяет генерировать синхросигналы. Есть возм-ть пропускать четные и нечетные элементы.

5.Управление питанием.

3 механизма процессора:

1)Изменение режима работы процессора:

А) режим полной мощности;

Б) активный режим - отключено умнож-е частоты;

В) режим сна;

Г) режим глубокого сна -из внутренних устройств работают только часы реального времени.

2) Управление тактовой f.

3) Упр-е напряжением питания.

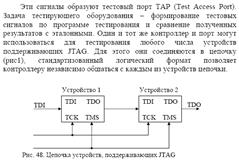

29. Отладка микропроцессорных устройств: интерфейс JTAG (IEEE 1149) – сигналы; схема соединения устройств, использующих данный интерфейс; схема сопряжения интерфейса с устройством.

Стандарт IEEE 1149.1 Boundary Scan Architecture (JTAG) предназначен для тестирования сложных логических схем, установленных в целевое устройство. 4 сигнала:

TMS (Test Mode Select) – сигнал выбора тестового режима; TDI (Test Data Input) – входные данные в последовательном двоичном коде; TDO (Test Data Output) – выходные данные в последовательном двоичном коде; TCK (Test Clock) –сигнал синхронизации последовательных данных.

(2) TDI– test data input

TDO–test data output

TCK–test clock

TMS–test mod select и необязательный TRST–test reset

BSR– ячейки располагаются на границе устр-ва м/у выводами и целевой логикой, т.к. некоторые выходы двунаправленные или с третьим состоянием и их нужно конфигурировать.BSR вкл. В себя служебные ячейки.

IR(instrument register)

DID (device Identification)доступен только для чтения

BPR (bypass register)обходной регистр, одноразрядный

30. Отладка микропроцессорных устройств: интерфейс JTAG (IEEE 1149) – регистры, инструкции. Данный интерфейс нужен для тестирования и отладки микросхем и плат, собранных в цельное устройство. При нормальной эксплуатации конечному пользователю не нужен отладочный интерфейс. Следовательно чтобы сократить “лишнюю” стоимость, число сигналов тестового интерфейса делают минимальным.

|

|

|

TDI– test data input

TDO–test data output

TCK–test clock

TMS–test mod select и необязательный TRST–test reset

BSR– ячейки располагаются на границе устр-ва м/у выводами и целевой логикой, т.к. некоторые выходы двунаправленные или с третьим состоянием и их нужно конфигурировать.BSR вкл. В себя служебные ячейки.

IR(instrument register)

DID (device Identification)доступен только для чтения

BPR (bypass register)обходной регистр, одноразрядный.

Регистры:

IR (Instruction Register)

DID (Device Identification) - Доступен только для чтения; по нему ТАВ – контроллер опознает тип и версию устройства.

BРR (Bypass Register) – обходной регистр одноразрядный; кратчайший обходной путь для продвижения данных через устройство без влияния на его работу.

Команды:

1.EXTEST (External Test)

Тест внешних относительно микросхемы цепей;

на выходные выводы МС подаются значения,

предварительно записанные в BSR; из входных сигнал идет на BSR, выходные ячейки BSR содержат 2 триггера: один хранит данные и использ. как элемент по продвижению данных;

второй - для хранения выходных данных.

EXTEST переписывает бит из первого триггера во второй. Входная ячейка ограничивается одним триггером. После команды «EXTEST» процессорам нужен перезапуск.

2. INTEST (Internal Test)

ЦСП не поддерживают эту команду

3. SAMPLE/ PRELOAD

Когда ТАР – контроллер в состоянии Capture DR это инструкция запоминает состояние входных выводов BSR положит. по форме ТСК

4. IDCODE – выдает идентиф. код устройства (TDI→OID→TDO)

5. BYPASS –(проходящие через устройство данные не будут оказывать влияние на его работу).

31. Отладка микропроцессорных устройств: интерфейс JTAG (IEEE 1149) – граф состояний и переходов. Данный интерфейс нужен для тестирования и отладки микросхем и плат, собранных в цельное устройство. При нормальной эксплуатации конечному пользователю не нужен отладочный интерфейс => чтобы сократить «лишнюю» стоимость, число сигналов тестов. Интерфейса делают минимальным:TMS (Test Mode Select) – сигнал выбора тестирующего режима

|

|

|

TDI (Test Data Input) – вход тестовых данных

TDO (Test Data Output) – выход тестовых данных

TCK (Test Clock) – сигнал синхронизации.

TRST (Test Reset)

Тестируемые устройства объединяются в цепочку.

Внутреннее устройство:

Граф состояний и переходов

TAB-контроллер представляет собой синнннннннхронный конечный автомат. Состояние Test-Logic-Restar – конроль переходит при Restarte или при удержаниии сигнала TMS=1 в течение менее 5ти тактов.Состояние сигнала изображено сверху стрелок. В этом состоянии тестовая логика отключена.

Знать соединение выделенной схемы

Run-Test-Idle промежуточное состояние, в нем регистры не мешают своего состония. В состояние Cupture, во время инструкций Extest и Sample BSR фиксируется состояние входных выводов. TDI -> TDO. Состояние Pause-DR продвижение данных временно прекращается. Состояние Update-DR данные поступают на выводы устройства. Cupture-IR регистр инструкций, загружается инструкция Sample. Состояние Shift-IR между TDI -> TDO включает регистр инструкций IR и продвигается на один разряд. Pause-IR продвижение данных ч/з регистр инструкций временно приостановлены. Update-IR фиксируется новая инструкция. Остальные состояния (6 штук) служат для служебный целей, для обеспечения функцион. Автомата. TAB контроллер может работать с различными устройствами для описания этих устройств BSDL.

1. Структура системы цифровой обработки сигналов. Влияние формы дискретизирующих импульсов на спектр дискретизированного сигнала.

2. Z-преобразование.

3. Разностные уравнения для описания дискретных систем, нерекурсивная и рекурсивная цифровая фильтрация. Структурные схемы цифровых фильтров.

4. Свертка дискретных сигналов: линейная и круговая свертка. 5. Свертка дискретных сигналов: секционная свертка. Привести пример.

6. Дискретное преобразование Фурье, растекание спектра.

8. Преобразование Уолша и его применение для обработки сигналов.

9. Интерполяция: спектральная трактовка, КИХ-фильтры для полиномиальной интерполяции 0- и 1-го порядка; использование полифазной структуры. 10. Децимация: спектральная трактовка, КИХ-фильтры для полиномиальной децимации 0- и 1-го порядка; использование полифазной структуры. 11. Квантование сигналов по уровням, шум квантования. Квантование и масштабирование коэффициентов цифровых фильтров. Привести примеры вычислений с использованием арифметики с насыщением и с переносом для трехразрядных чисел.

12. Форматы представления чисел в системах ЦОС.

14. Компандирование: А-закон. 15. Компандирование: Мю-закон

16. Кодеки с использованием линейного предсказания: структура и особенности кодирующей части вокодера.

17. Кодеки с использованием линейного предсказания: структура и особенности декодирующей части вокодера.

18. Архитектура цифровых сигнальных процессоров (ЦСП): общие принципы построения ЦСП и особенности их архитектуры; архитектура фон Неймана и гарвардская архитектура; обобщенная функциональная схема ЦСП.

19. Архитектура цифровых сигнальных процессоров (ЦСП): принципы работы кэш-памяти.

20. Конвейерное выполнение команд.

21. Архитектура цифровых сигнальных процессоров (ЦСП): CISC и RISC процессоры, основные особенности; отличия ЦСП с фиксированной и плавающей точкой. Классификация ЦСП (краткое перечисление типов).

22. Классификация ЦСП: стандартные ЦСП, улучшенные стандартные ЦСП.

23. Классификация ЦСП: суперскалярные процессоры, процессоры VLIW.

24. Основные семейства ЦСП фирм Texas Instruments, Freescale (Motorola), Analog Devices.

26. Представитель семейства ЦСП Analog Devices: BF531/532/533 – блок схема процессора, ядро процессора.

27. Представитель семейства ЦСП Analog Devices: BF531/532/533 – блок схема процессора, память, контроллер прерываний.

28. Представитель семейства ЦСП Analog Devices: BF531/532/533 – блок схема процессора, контроллер ПДП, часы реального времени, сторожевой таймер, таймеры общего назначения, SPORT, SPI, UART, PPI, GPIO, управление питанием и коэффициентом умножения частоты.

29. Отладка микропроцессорных устройств: интерфейс JTAG (IEEE 1149) – сигналы; схема соединения устройств, использующих данный интерфейс; схема сопряжения интерфейса с устройством.

30. Отладка микропроцессорных устройств: интерфейс JTAG (IEEE 1149) – регистры, инструкции.

31. Отладка микропроцессорных устройств: интерфейс JTAG (IEEE 1149) – граф состояний и переходов.

|

|

|

|

|

Дата добавления: 2015-07-02; Просмотров: 1082; Нарушение авторских прав?; Мы поможем в написании вашей работы!