КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Структура микросхем памяти

|

|

|

|

Полупроводниковые ОЗУ, ПЗУ состоят из двух основных частей: накопителя и схемы управления, или периферии. Накопитель – это основная часть ЗУ, где хранятся данные (двоичные коды). Периферия предназначена для ввода и вывода этих данных. В нее входят дешифраторы, усилители, регистры, разного рода ключевые схемы, коммутаторы и другие узлы.

Накопитель состоит из элементов памяти (ЭП), каждый из них хранит один бит информации. Основу ЭП составляют бистабильные ячейки, основным свойством которых является наличие двух устойчивых состояний – 0, 1.

На рис. 8.1 представлена типичная структура запоминающего устройства с матричной организацией накопителя и предназначенного записи и считывания информации.

Рис. 8.1. Структура микросхемы ОЗУ

На приведенной схеме используются следующие сокращения:

· ДШ х, ДШ у – адресные дешифраторы строк и столбцов;

· ФЗС – формирователь сигналов записи/считывания;

· СУ – схема управления;

· АШ х, РШ – адресные и разрядные шины;

· DI, DO – шины записи и считывания соответственно;

· БК – буферный каскад.

Накопитель представляет собой прямоугольную матрицу ЭП, содержащую nx строк и ny столбцов. Емкость накопителя N = nx · ny. Каждый ЭП подключен к адресным (АШ) и разрядным (РШ) шинам. Выбор требуемого ЭП осуществляется путем подачи определенной комбинации адресных переменных (Am … A 1 , A 0). Адресные дешифраторы строк (ДШ x) и столбцов (ДШ y) формируют сигналы выборки на соответствующих АШ, которые определяют строку и столбец накопителя, в котором расположен выбираемый ЭП. Таким образом, m адресных входов позволяют выбирать один из N = 2 m элементов памяти.

Режим работы микросхемы определяется сигналами выбора микросхемы  (CHIP SELECT) и записи-считывания

(CHIP SELECT) и записи-считывания  (WRITE/READ). При подаче низкого потенциала на вход выбора

(WRITE/READ). При подаче низкого потенциала на вход выбора  схема управления (СУ) разрешает формирование сигналов выборки на АШ x . Если при этом сигнал на входе

схема управления (СУ) разрешает формирование сигналов выборки на АШ x . Если при этом сигнал на входе  , то СУ формирует управляющий сигнал, при котором ФЗС обеспечивает запись в выбранном ЭП информации, поступающей на вход DI. Выход DO в этом случае находится в отключенном состоянии. Если сигнал

, то СУ формирует управляющий сигнал, при котором ФЗС обеспечивает запись в выбранном ЭП информации, поступающей на вход DI. Выход DO в этом случае находится в отключенном состоянии. Если сигнал  , то СУ переключает ФЗС в режим считывания, при котором информация из выбранного ЭП передается на выход DO, при этом состояние входа DI не влияет на работу микросхемы.

, то СУ переключает ФЗС в режим считывания, при котором информация из выбранного ЭП передается на выход DO, при этом состояние входа DI не влияет на работу микросхемы.

|

|

|

При  микросхема находится в режиме хранения, т. е. состояние ЭП не меняется при любых сигналах на входах (Am … A 0), DI,

микросхема находится в режиме хранения, т. е. состояние ЭП не меняется при любых сигналах на входах (Am … A 0), DI,  . Выход DO находится в отключенном состоянии.

. Выход DO находится в отключенном состоянии.

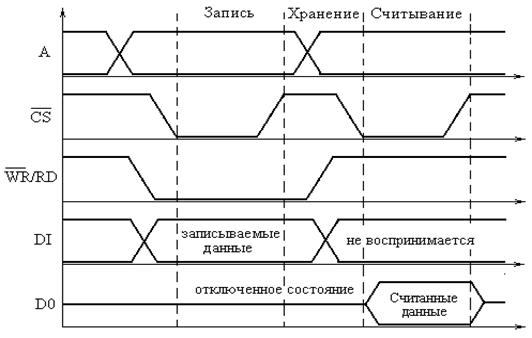

Типовые временные диаграммы, иллюстрирующие работу микросхем памяти, приведены на рис. 8.2

Рис. 8.2. Временные диаграммы работы микросхем

памяти с произвольной выборкой

Адресные сигналы A и сигнал  обычно устанавливаются на входах микросхемы до поступления сигнала

обычно устанавливаются на входах микросхемы до поступления сигнала  .

.

Микросхемы, предназначенные только для считывания информации, не содержат узлов, отвечающих за ее запись.

Запоминающие устройства с произвольной выборкой служат для оперативного запоминания информации и способны хранить ее только при включенном питании. По принципу действия различают статические и динамические ОЗУ. Элементом памяти статических ОЗУ (SRAM) служат триггеры, которые могут быть реализованы по любой технологии. В динамических ОЗУ (DRAM) носителем информации является емкость между затвором МОП-транзистора и корпусом, которая может быть заряжена или разряжена.

|

|

|

|

Дата добавления: 2014-01-15; Просмотров: 2213; Нарушение авторских прав?; Мы поможем в написании вашей работы!