КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Машинные команды

Состав машинных команд определяется системой команд микропроцессора.

[имя_метки] код_операции [операнд[,операнд]…]

MOVW A, ADB:var ADB //смена банка по умолчанию

MOVW A, var

#.5. Структурное программирование

| Условие | Описание | Истинно, если… |

| Z (EQ) / NZ (NE) | нуль (равно) / не нуль (не равно) | Z=1 / 0 |

| C (LO) / NC (HS) | перенос (ниже) / нет переноса (выше или равно) | С=1 / 0 |

| N / P | отрицательное / положительное | N=1 / 0 |

| V / NV | переполнение / нет переполнения | V=1 / 0 |

| LT / GE | меньше / больше или равно | (V or N)=1 / 0 |

| LE / GT | меньше или равно / больше | ((V xor N) or Z)=1 / 0 |

| LS / HI | ниже или равно / выше | (C or Z)=1 / 0 |

| T / NT | был перенос / не было переноса | T=1 / 0 |

В структурных операторах условие записывается в угловых скобках (например: <EQ>), или в виде условного выражения.

Условное выражение имеет два операнда, объединяемых знаком отношения.

| = = | равно | != | не равно |

| < | меньше | <= | меньше или равно |

| > | больше | >= | больше или равно |

Результат сравнения -логическое значение 1 (true) или 0 (false).

Чтобы сравнивались беззнаковые операнды, к выражению добавляется классификатор.u (например: A <=.u #210).

Первый операнд -всегда аккумулятор (А). Второй задаётся непосредственно (#imm), либо определяется с помощью прямой регистровой или косвенной адресации.

Условные выражения могут содержать несколько условий, объединяемых логическими операциями И (&&), либо ИЛИ (||) (например: A>#2 && A<=#10).

В качестве условия выбора может использоваться битовая адресация (например: PDR8:3). Для инвертирования логического значения может использоваться знак (!) (например:!PDR8:3).

.instruction[.data-size] (conditional-expression)

А) Оператор .if

,

,

где тип –тип данных для сравнения (B: байт, W: слово, L: двойное слово). По умолчанию используются байты; условие –условное выражение.

Пример:

.if(<NE>)

mov A, R1

.else

mov A, R2

.endif

Б) Оператор .switch

,

,

где оп1 –операнд с адресацией (#imm/ea).

Пример:

. switch (A)

.case (#0)

mov A, R0

.break

.case (#1)

mov A, R1

.break

.default

mov A, R2

.endsw

В) Оператор.for

,

,

где oп1, oп2, oп3 -операнды с адресацией #imm/ea; условие -условное выражение, связывающее A и оп2;

Пример:

.for(A=#0,<=.u#10,#2)

nop

.endf

Г) Оператор.repeat

Пример:

.repeat

inc A

.until (A<#10)

Д) Оператор.while

Пример:

.while(A<#05)

inc A

.endw

Е) Операторы.break и.continue

.break прерывает выполнение цикла, в котором она находится.

.while(A<#05)

inc A

.if(A<#0)

MOV A, #0

.break

.endif

.endw

.continue прерывает выполнение оставшейся части тела цикла и передаёт управление проверке условия.

.while(A<#05)

inc A

.if(A<#0)

MOV A, #0

.break

.else

.continue

.endif

.endw

Г) Манипулирование структурами данных

1) Неупорядоченные списки

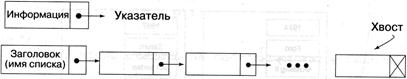

Список -последовательность размещённых в памяти элементов списка (байтов, слов и т.д.). Обычно списки содержат счётчик элементов списка. В смежных списках элементы помещаются в соседних ячйках памяти. В связных списках каждый элемент содержит указатель на следующий элемент списка. Последний элемент связного списка в указателе содержит признак конца списка.

Смежные списки обеспечивают произвольный доступ к элементам. В связных списках возможен только последовательный доступ к элементам.

а) Для добавления элемента в смежный список, его надо запомнить в конце списка и увеличить значение счётчика. В связном списке нужно изменить значения указателя в предыдущем элементе.

б) Для удаления элемента, надо сместить все последующие элементы смежного списка на одну позицию и уменьшить значение в счётчике. В связном списке указатель предыдущего элемента получает значение указателя в удаляемом элементе.

в) Для поиска заданного элемента надо сравнить каждый элемент списка с искомым значением.

г) При поиске максимального (минимального) значения в списке, первоначально предполагают, что «экстремум» соответствует значению первого элемента. Далее список последовательно просматривается до конца. Если «экстремум» меньше (больше) значения текущего элемента, то это значение становится «экстремумом».

Списки с указателями могут образовать очередь или стек.

Новый элемент добавляется в хвост очереди. Если элементы извлекаются с головы, то реализуется принцип FIFO.

При стековой организации элемент извлекается из хвоста, т.е. реализуется принцип LIFO.

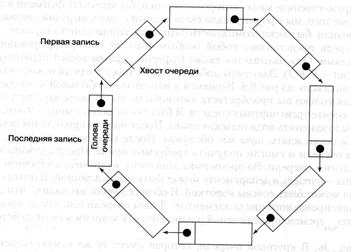

Круговая очередь –указатель хвостовой записи ссылается на головную запись.

2) Сортировка неупорядоченных данных

Сортировка позволяет разместить элементы списка по возрастающим или убывающим значениям.

3) Упорядоченные списки с произвольным доступом

а) Бинарный поиск элемента

б) Вставка элемента

-Найти место вставки элемента;

-Освободить место вставки с помощью сдвига всех бóльших элементов на одну позицию вниз;

-Поместить вставляемый элемент в освободившееся место;

-Увеличить счётчик элементов на единицу.

в) Удаление элемента

-Найти нужный элемент;

- Сдвинуть все бóльшие элементы на одну позицию вверх;

-Уменьшить счётчик элементов на единицу.

#. БЛОКИ ПАМЯТИ

#.1 Типовая структура модуля памяти

#.2. Типы элементов памяти

ПЗУ (ROM) –энергонезависимая память (ROM, PROM, EPROM)

OЗУ (RAM)–энергозависимая память (SRAM, DRAM).

#.2.1. Элемент памяти статического ОЗУ

На выходе не выбранных ЭП –«1».

#.2.2. Элемент памяти динамического ОЗУ

#.2.3. Элемент памяти масочного ПЗУ

#.2.4. Элемент памяти программируемого ПЗУ

#.2.5. Элемент памяти перепрограммируемого ПЗУ

Пороговое напряжение смещается до 14…16 В.

#.3. Разновидности выходных каскадов

#.3.1. Выход по схеме «И»

#.3.2. Монтажное «И»

#.3.3. Высокоимпедансный выход

Объединение входных и выходных информационных выводов.

#.4. Временные диаграммы работы микросхем памяти

#.5. Увеличение разрядности ячеек памяти

#.6. Увеличение ёмкости модуля памяти

Модуль памяти 8К байтов на микросхемах по 2К байтов.

#.7. Организация памяти в микропроцессорных устройствах

Принстонской архитектура

Гарвардская архитектура

Подключение внешних модулей памяти.

Противоречивость требований по ёмкости и быстродействию модулей памяти разрешается иерархической структурой модулей:

- Регистровая память (до 1 Кбайта, время обращения 1 машинный такт)

- КЭШ-память (ёмкость до 1Мбайта, время обращения 1…4 машинных такта)

- Оперативная память (ёмкость до 10 Гбайтов, время обращения 12…40 машинных тактов).

Иерархичность структуры позволяет согласовать высокую скорость микропроцессора со сравнительно медленными схемами памяти большой ёмкости.

При поиске необходимых данных, процессор обращается к регистровой памяти, затем к КЭШ-памяти и далее к оперативной памяти.

#.7.1. Регистровая память – это набор регистров общего назначения, размещаемых на одном кристалле с процессором. Регистры обычно не имеют адресов в адресном пространстве микропроцессора, и обращение к ним выполняется по встроенным именам. Регистровая память работает в темпе микропроцессора и её классифицируют как сверхоперативное запоминающее устройство.

#.7.2. КЭШ-память является буферной памятью между основной оперативной памятью и процессором. Будучи соизмеримой по быстродействию с регистровой, КЭШ-память имеет значительно большую ёмкость. Эффективность КЭШ-памяти основывается на принципах временной и пространственной локальности программ. Временная локальность состоит в том, что при считывании данных велика вероятность того, что вскоре программа обратится к тем же данным. Пространственная локальность предполагает, что высока вероятность того, что после выборки данных, программа обратится к соседней ячейке памяти.

КЭШ-память представляет собой совокупность строк, содержащих фиксированное количество адресуемых единиц памяти (байтов, слов) с последовательными адресами. Обычный размер строки n =16…256 байтов. В любую строку КЭШ-памяти могут быть скопированы n байтов из основной памяти, ёмкости M. Если КЭШ-память имеет N строк, то в i -ую строку (i =1… N) могут быть скопированы k=M /(N∙n) блоков по n байтов из ОЗУ. Для указания номера блока, размещённого в строке КЭШ-памяти, каждая строка снабжается специальным полем – тегом. В теге хранится адрес первого байта строки.

Пример. Ёмкость ОЗУ M =96 байтов, КЭШ-память имеет N =4 строк и каждая строка содержит n =8 байтов. Для адресации ячеек ОЗУ используются а =7 разрядов адреса.

В строке может размещаться один из k=M /(N∙n)=3 блоков из ОЗУ. В теге размещаются t=а - log 2(n)=4 старших разряда адреса первого байта, помещённого в строку.

Определим наличие в КЭШе байта с адресом А 1=1616:

- Сдвинуть адрес на s = log 2(n)=3 разряда вправо: А 1 S= А 1/2 n= 0216;

- Определить остаток от деления i=(А 1 S) mod N= 0216 mod 4=2;

- Сравниваем тег i -ой строки со сдвинутым адресом: с =тег i - А 1 S;

· Если с =0, то определяем смещение байта в i -ой строке КЭШ-памяти:

h = А 1- А 1 S∙ 2 n= 1616-1016=6;

· Если с =1, то в i -ую строку КЭШ-памяти из ОЗУ копируется блок, с начальным адресом А 0= А 1 S∙ 2 n= 1016.

·

Приведённая структура носит название КЭШа прямого отображения. Недостаток структуры проявляется, если последовательно выбираются байты из блоков, отображаемых на одну строку КЭШа. Например, если поочерёдно выбираются байты с адресами 2816 и 4816, после каждой выборки необходимо обновлять содержимое первой строки КЭШа. В этом случае преимущество в быстродействии КЭШ памяти теряется.

Проблема решается, если использовать ассоциативный КЭШ (точнее, частично ассоциативный КЭШ).

В частично ассоциативном КЭШе память разбивается на несколько банков. Любой блок из ОЗУ может быть скопирован в любой банк. При этом один блок одновременно присутствует в двух строках КЭШ-памяти.

При выполнении программы, данные прежде всего изменяются в КЭШе. В ОЗУ данные обновляются синхронно с изменениями в КЭШе (сквозная запись), либо перед освобождением строки для записи другого блока ОЗУ (обратная запись).

Запись в КЭШ производится сразу целым блоком из ОЗУ за один цикл чтения, даже если требуется только один байт из блока.

#.7.3. Микросхемы памяти характеризуются временем доступа taccess и временем цикла памяти tcycle. Время доступа, это время между подачей управляющих сигналов, и появлением данных на внешних выводах. Обычно tcycle> taccess, т.к. после чтения/записи данных микросхеме требуется время на восстановление состояния. Расслоение основной оперативной памяти позволяет сократить время выборки данных из памяти. Например, для выборки последовательно четырёх байтов данных требуется время ТО ≥ 4 tcycle. В случае расслоения время сокращается до ТР ≥ 4 taccess, поскольку соседние байты размещаются в разных микросхемах.

Добавочный разряд А 13 используется для выбора формата передаваемых данных (слово или байт).

#.7.4. Стековая память позволяет записывать и выбирать данные по одному предопределённому адресу, т.е. нет затрат времени на формирование адреса. Данные в стеке организованы по принципу LIFO - «последним вошёл – первым вышел» (при чтении из стека выбирается число, помещённое в стек последним), или по принципу FIFO - «первым вошёл – первым вышел» (при чтении из стека выбираются числа в порядке записи).

По способу реализации различают аппаратный и программный стек. Аппаратный стек представляет собой набор N сдвигающих регистров. Первый регистр называют вершиной стека, а N -ный –дном стека. Адресуется регистр вершины стека. Операции записи и чтения выполняются с вершиной стека. Перед записью содержимое i -го (i =1… N -1) регистра перемещается в (i+ 1) регистр (старые данные из N -го регистра теряются). Первый регистр освобождается и в него производится запись.

При чтении выполняется выборка с вершины стека, и данные из i -го (i =2… N) регистра перемещаются в регистр (i- 1).

При программной реализации в качестве регистров стека используются ячейки основной памяти. Для управления стеком используется специальный регистр – указатель стека SP. Если вершиной стека является ячейка с адресом AВ, то в регистр SP записывается число (АВ -1). При записи в стек, содержимое SP увеличивается на единицу и производится запись в вершину стека. При следующей записи SP еще раз инкрементируется и производится запись в ячейку с адресом (АВ +1) и т.д.

При чтении из стека производится выборка данных из ячейки с адресом, размещённом в SP и, после выборки, содержимое SP уменьшается на единицу.

#.7.5. Ассоциативная память осуществляет поиск информации по содержимому ячейки памяти, а не по адресу. Дополнительно к информации D, хранящейся в запоминающих ячейках (ЗЯ), добавляются разряды (АП - ассоциативный признак), характеризующие эту информацию. Например: 00 –высокочастотный диод; 01 –выпрямительный диод; 10 –n-p-n транзистор; 11 –p-n-p транзистор.

Для поиска нужной информации в регистр ассоциативного признака (РП) заносится параметр поиска – ассоциативный признак нужной информации (например, 00 –для поиска высокочастотных диодов). Для выбора нужных элементов ассоциативного признака, в регистр маски (РМ) записывается число, содержащее единицы в нужных разрядах. Например, при записи в РМ числа 10, разряд, содержащий признак частотных свойств диодов, будет замаскирован и будет произведён поиск ячеек, содержащих информацию о всех диодах.

В каждой ЗЯ логическая схема эквивалентности формирует число у, содержащее единицу в тех разрядах, в которых совпадают значения битов ассоциативного признака (s) и параметра поиска (f). Например, у ячеек, содержащих описания диодов, будут сформированы слова 11 или 10, а у ячеек с описанием транзисторов – 01 или 00. При выполнении дизъюнкции с инвертированной маской, формируются слова 11, 11, 01 или 01. В регистре совпадений (РС) устанавливаются те разряды, которые управляются словами, содержащими только единицы (11). Каждому адресу в РС соответствует один разряд. Наличие единицы в разряде РС говорит о том, что в соответствующей ячейке имеется искомая информация.

Блок формирования результата (ФР) позволяет определить, имеется ли искомая информация в модуле памяти, и если имеется, то по каким адресам. Выборка данных из памяти, производится обычным порядком с адресацией ЗЯ.

#. УСТРОЙСТВА СВЯЗИ С ОПЕРАТОРОМ В ОБСЛУЖИВАЕМЫХ СИСТЕМАХ

#.1. Светодиодные индикаторы

ID=10…15 мА,

VD=1,5 B.

VOL=0,4

R≥(VCC- VOL-VD)/ ID=(5-0,4-1,5)/15=206 Ом.

Отображение состояния на трёхстабильных выходах.

Для вывода символа используются семисегментные индикаторы.

#.2. Матричный индикатор

#.3. Графический ЖК-дисплей.

ЖК панель состоит из 128´64 точек, размером 0,48´0,48 мм.

|

Логически панель разделена на два сегмента размером 64´64 точки. Управление сегментами независимое.

Изображение хранится во встроенном ОЗУ, емкостью 2´64´8 байтов. Каждая точка изображения определяется соответствующим битом в памяти. При единичном значении бита выводится тёмная точка. Каждая точка идентифицируется четырьмя координатами:

-сегмент дисплея (А или В);

-страница (X=0¸7);

-положение на странице (Y=0¸63);

-номер разряда в байте (DB0¸DB7).

Для вывода тёмной точки на дисплей, нужно задать её координаты и записать в память дисплея байт, в котором адресованный бит установлен в единицу. При этом надо иметь в виду, что выводимый байт одновременно управляет состоянием восьми точек дисплея.

Дисплей имеет две шины –данных и управления. Восьмиразрядная шина данных и пятиразрядная шина управления:

a) две линии выбора сегментов CSA и CSB.

b) линия D/I характеризует передаваемую информацию –данные или команда.

c) линия R/W задаёт направление обмена –чтение или запись.

d) Сигналы управления воспринимаются по импульсу на линии Е

Система команд дисплея приведена в таблице.

Таблица.7.1.

| Команда | Состояние линии | Комментарий | |||||||||

| R/W | D/I | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 | ||

| Включение. | 1/0 | 1 –включить дисплей 0 –выключить дисплей | |||||||||

| Установить Х | Х=0¸7 | Запись в указатель страницы | |||||||||

| Установить Y | Y=0¸63 | Запись в счётчик позиции. | |||||||||

| Чтение состояния | 1/0 | 1/0 | Состояние дисплея: DB7 =1/0 (занят/свободен) DB5=1/0 (включён/выключен) | ||||||||

| Запись данных | Данные | Запись данных в ОЗУ. Инкремент Y | |||||||||

| Чтение данных | Данные | Чтение данных из ОЗУ Инкремент Y. |

После выполнения команды записи и чтения, данных содержимое счётчика позиций (координата Y) автоматически инкрементируется.

Перед тем, как передать команду управления адресом или обмена данными, необходимо прочитать (команда «Чтения состояния»), и проанализировать байт состояния дисплея. Бит готовности (DB7) должен быть сброшен.

#.4. Клавиатура

#. ВЗАИМОДЕЙСТВИЕ МИКРОПРОЦЕССОРА С ОБЪЕКТОМ УПРАВЛЕНИЯ

При сопряжении микропроцессора с внешними периферийными устройствами нужно учитывать их основные электрические параметры. Например, для типовых устройств:

VOH=4,2 В

VOL=0,4 В

IOH=-0,8 мА

IOL=1,6 мА

VIH=3,5 В

VIL=1,0 В

IIH=10 мкА

IIL=-10 мкА.

Входной ток приёмника не должен превышать допустимой величины выходного тока источника. В противном случае логические уровни сигналов не гарантируются.

#.1. Ввод информации с двоичного датчика. Ожидание события

В устройствах и системах логического управления объектами, события фиксируются двоичными датчиками типа да/нет (концевой выключатель).

Алгоритм ожидания замыкания ключа (размыкания ключа)

Если требуется ожидание импульсного сигнала с ключа, то можно последовательно выполнить процедуры ожидания замыкания и размыкания.

#.2. Устранение дребезга контактов ключа.

Устранения дребезга контактов может быть обеспечено аппаратными или программными средствами. При небольшом числе ключей можно использовать RS триггер.

При программном устранении часто используется подсчёт заданного числа совпадающих значений на ключе, или организация фиксированной временной задержки.

Процедура задержки DELAY может быть организована программно или аппаратно, с использованием таймера.

#.3. Вывод двоичных управляющих сигналов.

Для управления исполнительными механизмами, работающими по принципу включён/выключен на соответствующем выводе выходного регистра нужно сформировать статический сигнал 0 или 1.

При параллельном управлении группой исполнительных механизмов, на выходной регистр выводится управляющее слово (CTRL), каждый бит которого управляет своим механизмом.

При формировании управляющего слова для каждого бита управляющего слова записывается маска, содержащая единицу только в соответствующем бите.

MSK2=00000100

Для установки бита в управляющем слове выполняется операция дизъюнкции с маской:

CTRL←CTRL OR MSK2.

Для очистки бита выполняется операция конъюнкции управляющего слова с инверсией маски:

CTRL←CTRL AND NOT(MSK2).

#.4. Управление электродвигателем постоянного тока

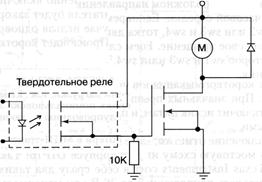

Для управления скоростью вращения двигателя применяются ШИМ преобразователи. Обычно, выходной мощности МК для непосредственного управления двигателем не достаточно. ШИМ –сигналы с МК необходимо усилить по мощности. Для усиления используются электромагнитные реле, биполярные и полевые транзисторы, тиристоры и т.п.

В схемах управления двигателями малой и средней мощности чаще всего применяют полевые МДП –транзисторы в ключевом режиме. Такие ключи могут коммутировать цепи с токами, свыше 100 А. Они обладают очень большим входным сопротивлением (малая мощность входного сигнала), большим сопротивлением канала в выключенном и малым сопротивлением во включённом состоянии (малые потери энергии в транзисторе, высокий КПД).

Резистор в цепи затвора способствует скорейшему рассасыванию заряда при переходе управляющего сигнала от единицы к нулю.

При работе электрического двигателя в цепях питания возникают значительные помехи, способные повлиять на работу управляющего МК. Рекомендуется электрически изолировать схему управления от силовых цепей устройства. Для этого можно использовать оптроны.

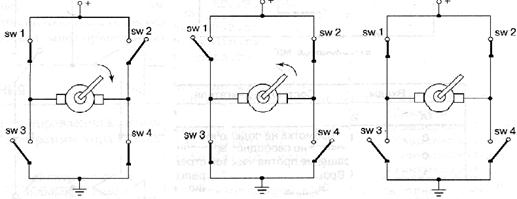

Для изменения направления вращения двигателя может быть использована схема однофазного мостового инвертора напряжения

#.5. Управление шаговыми двигателями

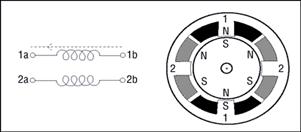

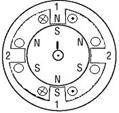

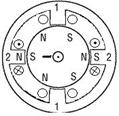

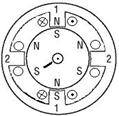

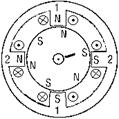

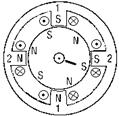

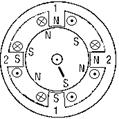

Шаговые двигатели применяются для ступенчатого поворота ротора. Минимальный угол поворота называют шагом. Роторы шаговых двигателей обычно представляют собой многополюсный магнит. Обмотки статора могут иметь отвод от средней точки.

В зависимости от числа полюсов ротора и обмоток статора величина шага может иметь величину от 900 до 0,50.

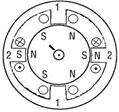

Для увеличения вращающего момента можно подавать управляющее напряжение одновременно в обе обмотки.

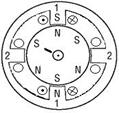

Для уменьшения шага можно использовать полушаговый режим.

Если при отсутствии тока в одной обмотке в другой обмотке ток увеличить в  раз, то вращающий момент остаётся постоянным.

раз, то вращающий момент остаётся постоянным.

При синусоидальном изменении токов в обмотках двигатель работает в микрошаговом режиме с постоянным вращающим моментом.

#.5. Подключение аналоговых датчиков

Чаще всего диапазон изменения выходного сигнала аналогового датчика не совпадает с допустимым диапазоном входного аналогового сигнала МК. Для согласования диапазонов разрабатываются схемы сопряжения, выполняющие усиление и смещение входных сигналов.

Физическая величина изменяется от Х1 до Х2. На выходе датчика напряжение изменяется в пределах U1…U2. Это напряжение усиливается с коэффициентом К. Усиленное выходное напряжение датчика смещается на величину UСМ. Допустимый диапазон изменения входного сигнала АЦП –V1…V2.

Для согласования диапазонов изменения сигналов должны выполняться соотношения:

При известных диапазонах изменения сигналов U и V, решение системы уравнений позволяет определить требуемые для согласования значения К и UCM.

Для удаления нежелательных гармоник сигнала с датчика, в схему сопряжения включают аналоговые фильтры.

#.6. Цифровая обработка сигнала.

Термин ЦОС встречается применительно к системам управления, в которых на основе ввода в систему задающих сигналов и сигналов обратной связи постоянно, в реальном масштабе времени формируются и выдаются на ОУ значения управляющего воздействия, т.е. осуществляется цифровое регулирование переменных.

Второй типовой задачей является задача получения ряда последовательных выборок значений входной переменной и преобразование этой последовательности в другую, в которой отсутствуют помехи и шумы. Такая задача называется цифровой фильтрацией сигнала.

#.6.1. Цифровые регуляторы.

Получим дискретную модель ПИД регулятора на основании его передаточной функции.

(1)

(1)

Продифференцируем (1), чтобы избавиться от интеграла:

Особенностью цифровых систем является то, что от момента получения информации о входной величине e(t), до момента выдачи сигнала U(t) и получения следующего значения входного сигнала, проходит определённое время -период дискретизации по времени Т.

Таким образом, входная информация доступна только в дискретные моменты времени

t=k∙T, где k- целое число.

Для обеспечения постоянства периода Т может использоваться таймер интервала дискретизации. Выдача вычисленного управляющего воздействия производится в начале следующего цикла выборки входного сигнала. Входной сигнал и управляющее воздействие представляют собой решётчатые функции

e(k∙T) и U(k∙T), или e(k) и U(k).

Если величина Т существенно (на порядок) меньше самой маленькой постоянной времени системы, то от дифференциального уравнения регулятора можно перейти к разностному, путём замены непрерывных величин f(t) дискретными f(k), а дифференциалов –разностями:

Перейдём к разностному уравнению, учитывая, что dt→Δt=T:

При реализации регулятора можно применить рекуррентный алгоритм:

U(k) = U(k-1) + ∆U(k),

где ∆U(k) = K0e(k) - K1e(k-1) + K2e(k-2).

Для хранения U(k) используем регистр А, а для трёх последовательных выборок –регистры R0, R1, R2.

#.6.2. Цифровые фильтры

Цифровая фильтрация сводится к обработке полученной последовательности

e(k), e(k-1), …, e(k-n)

так, что рассчитанная выходная последовательность будет обладать желаемыми свойствами, например, не будет содержать высокочастотных помех (ФНЧ) или не будет содержать гармоник в определенном частотном диапазоне (РФ) и т.п.

Фильтры, как и регуляторы, могут описываться дифференциальными уравнениями, т.е. дискретные модели фильтров и регуляторов совпадают.

Например, для фильтра n-го порядка дискретная модель представляет собой линейное разностное уравнение n-го порядка:

Если все аi=0, то фильтр не рекурсивный, в противном случае –рекурсивный, т.е. текущая величина выходного сигнала зависит от значений выходного сигнала в предшествующие моменты времени.

Применение Z-преобразования.

В общем случае, дискретные устройства описываются с помощью дискретного аналога преобразования Лапласа –Z-преобразования, устанавливающего связь между входной и выходной последовательностью в виде полиномов от переменной Z.

Например:

Задержка на один тактовый период: y(n)=x(n-1) Û Y(Z)=X(Z)∙Z-1;

Единичный скачок:  Û

Û  ;

;

Единичный импульс:  Û X(Z)=1.

Û X(Z)=1.

Это позволяет легко формально перейти от разностного уравнения к его изображению.

Например, рассмотрим рекурсивный фильтр 1-го порядка.

На основании приведённых уравнений можно составить функциональную схему.

Соответственно, передаточная функция фильтра 2-го порядка

имеет функциональную схему:

При реализации фильтров высокого порядка производительности одного процессора может оказаться недостаточно. В этом случае можно применить многопроцессорную структуру с последовательным или параллельным включением звеньев.

а) последовательное включение звеньев.

Если разложить числитель и знаменатель на сомножители не выше второго порядка, передаточную функцию можно представить в виде произведения дробей:

Каждое звено может быть реализовано на отдельном микропроцессоре.

б) параллельное включение звеньев.

Выражение может быть представлено суммой дробей:

В отличие от последовательного соединения звеньев, результаты обработки появляются с задержкой Т, а не kT.

#. ПЕРЕДАЧА ИНФОРМАЦИИ В МПС

#.1. Методы передачи информации

Используются два метода передачи: синхронный и асинхронный.

#.1.1. Асинхронная передача.

Передающее устройство устанавливает одно из возможных состояний (0, 1) и поддерживает его в течение определённого периода времени, после которого состояние на линии может быть изменено. Скорость обмена определяется самым медленным устройством.

#.1.2. Синхронная передача.

Если приёмное устройство не всегда готово к приёму информации, то можно использовать синхронную передачу с квитированием. При этом приём сопровождается передачей квитанции приёмником. При получении квитанции передатчик может изменить состояние линии данных.

#.2. Кодирование информации

Физическое представление двоичных чисел называют кодированием логических уровней. Разные способы кодирования определяют разные коды передачи информации.

а) Униполярный код без возвращения к нулю. Недостаток –обрыв не диагностируется.

б) Биполярный код без возвращения к нулю.

в) Биполярный код с возвращением к нулю. Содержит синхроимпульсы. Нельзя использовать трансформаторную развязку, т.к. при передаче длинной последовательности единиц или нулей исчезает постоянная составляющая.

г) фазоманипулированный самосинхронизирующийся код без возвращения к нулю [б) XOR (sync)].

- дополнение

а) NRZ

б) RZ

в) Манчестер (NRZ xor sync)

-1 –в середине периода переход 1→0

-0 –в середине периода переход 0→1

г) Дифференциальный Манчестер

в середине периода всегда переход

-1 –нет перехода в начале периода

-0 –переход в начале периода

д) DBP –дифференциальный бифазный код

в начале периода всегда переход

-1 –нет перехода в середине периода

-0 –переход в середине периода

е) Миллера

-1 –переход в середине периода

-0→0 –переход в начале периода

ж) Модифицированный Миллера

-1 –короткий импульс в середине периода

и) NRZI

-0 –переход в начале периода

После шести последовательных 1 дополнительно вставляется 0 (bit stuffing)

____________________________________________________________________

#.3. Форматы слов при обмене

#.4. Виды сообщений

Инициатором обмена является ведущее устройство. Ведомое устройство выполняет адресованную ему команду и передаёт ответное слово. По направлению передачи данных можно определить три основных типа сообщений.

#.5. Интерфейсы микропроцессорных систем

Совокупность цепей, объединяющих устройства в заданную структуру, должна отвечать трём принципам согласования: функциональному, электрическому и механическому. Функциональная совместимость обеспечивается формированием сигналов управления и синхронизации взаимодействующими модулями. Электрическая совместимость предполагает обмен сигналами заданного уровня и мощности. Механическая совместимость требует использования определённых конструкций разъёмов, кабелей и т.п.

Интерфейс –совокупность унифицированных аппаратных, программных и конструктивных средств, необходимых для взаимодействия различных функциональных компонентов. Интерфейсы можно разделить на системные интерфейсы и интерфейсы периферийного оборудования.

Системные интерфейсы предназначены для организации связи на платах, между платами, модулями и блоками цифровых систем. Интерфейсы периферийного оборудования предназначены для подключения к вычислительной системе периферийных устройств, построения распределённых систем управления и локальных вычислительных сетей.

Интерфейсы, в которых каждый бит информации передают по отдельному проводнику (линии связи) называют параллельными. Если биты информации передаются поочерёдно по одному проводнику, то интерфейс называют последовательным.

Параллельные интерфейсы используют для внутримодульных и межмодульных соединений. Длина линии связи параллельных интерфейсов не превышает нескольких метров. Для связи удалённых модулей используют последовательные интерфейсы.

#.5.1. Последовательный интерфейс RS-232C

Количество устройств -2

Скорость передачи –до 115 кбит/с

Расстояние –до 30 м

Информация передаётся по одной линии. Для управления обменом используют дополнительные сигналы:

RTS –«запрос передатчика»: готовность передатчика (активен до конца обмена);

CTS –«сброс передатчика»: готовность приёмника (активен до конца обмена).

Длительность передачи одного разряда определяет скорость обмена (50…115000 бод).

Формат передачи:

Формат передачи:

Бит контроля четности PAR используется для выявления одиночной ошибки в передачe. Значение бита устанавливается таким, чтобы обеспечить чётное число единиц в передаваемом слове.

Передатчик и приёмник содержат тактовые генераторы с частотой больше, чем частота следования битов (например, в 16 раз). Стартовый импульс START включает счётчик тактовых импульсов, который инициирует считывание бита после 8, 16, 16 … импульсов, т.е. в середине периода передачи бита.

В интерфейсе принята кодировка в биполярном коде без возвращения к нулю с отрицательной логикой:

«1» → -5…-15 В,

«0» → +5…+15 В.

Интерфейс может использоваться для подключения нескольких ведомых устройств к одному ведущему. При этом бит контроля чётности заменяется девятым битом данных D8. Когда ведущее устройство передаёт адрес, оно устанавливает бит D8 в единицу. Ведомые устройства анализируют адресную информацию, и адресованное устройство выполняет обмен данными с ведущим. При передаче данных бит D8 сбрасывается в нуль.

В этом режиме контроль чётности невозможен

#.5.2. Синхронный последовательный интерфейс SPI

Количество устройств –до 8

Скорость передачи –до 5 Мбит/с

Расстояние –до 3 м

Позволяет осуществлять одновременную передачу и приём данных. Используется в последовательных модулях памяти, АЦП, дисплейных адаптерах и др.

#.5.3. Последовательный интерфейс I2C

Количество устройств –до 40

Скорость передачи –до 3 Мбит/с

Расстояние –до 5 м

Двухпроводный интерфейс со скоростью передачи до 400 Кбод:

SDA –линия данных;

SCL –линия тактирования.

Каждое устройство имеет адрес. При передаче ведущее устройство сначала передаёт адрес ведомого и бит направления обмена. Выходы всех устройств имеют открытый сток или открытый коллектор.

а) начало и окончание передачи

Смена данных возможна при низком уровне SCL. Если данные изменяются на высоком уровне SCL, то опознаются состояния начала передачи (S) или окончания передачи (Р).

б) адресация

Приведём формат слова при семи битном адресе.

в) передача данных

Данные передаются побайтно. После каждого байта ведомый передаёт бит подтверждения обмена (ACK –низкий уровень). Если подтверждения нет (высокий уровень на SDA), то ведущий прерывает передачу, выставляя состояние Р. Ведомый может задержать передачу, удерживая линию SCL на низком уровне.

Данные передаются побайтно. После каждого байта ведомый передаёт бит подтверждения обмена (ACK –низкий уровень). Если подтверждения нет (высокий уровень на SDA), то ведущий прерывает передачу, выставляя состояние Р. Ведомый может задержать передачу, удерживая линию SCL на низком уровне.

г) арбитраж в протоколе I2C

На шине может появиться больше одного ведущего, при этом может возникнуть конкуренция сигналов. Арбитраж осуществляется на линии SDA при SCL=1.

Синхронизация тактовых импульсов

#. Периферийные модули МК МВ90F591G

#.1. Система прерываний

Различают четыре типа прерываний:

· аппаратные –по запросам от встроенных периферийных модулей или по сигналам с внешних выводов INT;

· программные –при выполнении специальных команд вызова прерывания (INT # номер_прерывания);

· расширенный интеллектуальный сервис ввода/вывода (EI2OS) –разновидность аппаратного прерывания, осуществляющая обмен по типу прямого доступа к памяти;

· исключения –возникающие при попытке выполнить несуществующую команду.

Система различает 256 источников прерываний. Каждому источнику соответствует фиксированный 4-байтный вектор прерывания из банка FF. Начальный адрес процедуры обработки прерывания размещается в трёх младших байтах вектора.

Для управления запросами, в управляющих регистрах периферийных устройств размещаются флаги появления запроса и биты разрешения обработки запроса.

Система поддерживает восьми уровневую систему приоритетов: 0 –высший, 7 –низший. Каждому аппаратному прерыванию должен быть установлен уровень приоритета в соответствующем регистре управления прерыванием (ICRХ). При одновременном поступлении запросов с одинаковыми приоритетами, преимущество отдаётся источнику с меньшим номером.

Пример:

Перезагружаемый таймер:

номер прерывания 23; адрес вектора 0хFFFFA0; регистр упр. ICR6; адрес 0хВ6.

АЦП:

номер прерывания 31; адрес вектора 0хFFFF80; регистр упр. ICR10; адрес 0хВА.

При одинаковых уровнях приоритета преимущество в обслуживании имеет таймер.

Запросы поступают на контроллер прерывания, который выбирает самый приоритетный запрос и передаёт его в процессор.

Для перехода к обработке запроса должно быть выполнены условия:

· не запрещены все прерывания (бит I в PS);

· содержимое маски уровня приоритета (ILM) больше уровня поступившего запроса.

Перед переходом на процедуру обработки прерывания в системном стеке автоматически сохраняются регистры A, DPR, ADB, DTB, PCB, PC, PS. Затем адрес процедуры из вектора прерывания загружается в PCB и PC, а в ILM –уровень приоритета обрабатываемого прерывания.

После этого выполняются команды процедуры обработки прерывания. Последней командой процедуры должна быть команда RETI. По этой команде из стека восстанавливаются сохранённое содержимое регистров и работа прерванной программы возобновляется.

Чтобы контроллер мог обслуживать запросы от периферийных модулей, нужно:

· задать область системного стека;

· инициировать работу модуля;

· установить уровень приоритета в ICRХ;

· установить бит разрешения прерывания в регистре управления модулем;

· записать в регистр маски уровня приоритета (ILM) число большее, чем в ICRХ;

· установить бит запрещения прерывания (бит I в PS).

#.2. Порты ввода-вывода

Предназначены для связи МК с объектом управления через внешние выводы на корпусе микросхемы.

Всего в МК девять восьмибитных портов и один шестибитный порт. Отдельные разряды портов в режиме альтернативных функций используются для связи встроенных модулей с внешней средой.

#. 3. Таймер временной базы

Таймер состоит из 18-разрядного счётчика и регистра управления. Он формирует запросы на прерывание с заданными промежутками времени. Дополнительно таймер формирует импульсы для сторожевого таймера.

#. 4. Сторожевой таймер

Сторожевой таймер состоит из селектора, двухбитного счётчика, схемы сброса и регистра управления. Счётчик таймера получает импульсы из таймера временной базы. Регистр управления позволяет определить причину появления сигнала сброса

#.5. Перезагружаемый 16-разрядный таймер

Таймер работает в режимах внутреннего или внешнего тактирования. В основе таймера -16-разрядный вычитающий счётчик. После обратного переполнения устанавливается флаг переполнения. В начале работы счётчик загружается из регистра перезагрузки. Настройка режимов работы выполняется через регистр управления.

#. 6. Таймер ввода-вывода

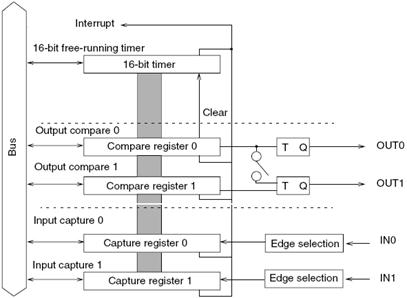

Таймер содержит 16-разрядный счётчик, три модуля двухканальных выходных компараторов, три модуля двухканальных входных фиксаторов.

Текущее значение счётчика может быть считано или установлено при обращении к регистру данных TCDT. Регистр состояния TCCS управляет работой таймера.

Сброс счётчика по переполнению:

Сброс счётчика по совпадению с регистром сравнения 0.

В модуле выходного компаратора производится сравнение текущего значения счётчика со значением в регистре сравнения ОССР0/1. При совпадении этих значений, инвертируется значение на выходном пине OUT0/1 и возможен запрос прерывания.

Управление выходным компаратором выполняется через регистр OCS0.

Диаграмма выходов при CMOD=0

Диаграмма выходов при CMOD=1

Модуль входного фиксатора определяет появление фронта внешнего входного вывода и запоминает текущее значение счётчика в регистре-фиксаторе IPCP0/1.

Управление модулем выполняется через регистр ICS01.

#.7. Аналого-цифровой преобразователь

Имеет на входе восьмиканальный мультиплексор аналоговых сигналов. Входы мультиплексора в режиме альтернативной функции делят внешние выводы с портом Р6.

Для перевода выводов в режим входа мультиплексора используются соответствующие выводы регистра ADER.

В блоке АЦП только один регистр данных и результаты перезаписываются после каждого преобразования. В режиме непрерывного преобразования следует использовать прерывание в режиме EI2OS. Предусмотрено три варианта запуска: программный, внешним сигналом и по таймеру.

Выбор режима работы обеспечивает:

· одиночное преобразование выбранных каналов (возможно с перезапуском);

Пример 1: ANS=010; ANE=010.

”start”→AN2→”остановка”.

Пример 2: ANS=000; ANE=011.

”start”→AN0→AN1→AN2→AN3→”остановка.”

∟→”start”→AN0→AN1→AN2→AN3→”ост”.

· непрерывное преобразование;

Пример 3: ANS=000; ANE=001.

”start”→AN0→AN1→AN0→AN1→…

Пример 4: ANS=010; ANE=010.

”start”→AN2→ AN2→…

· преобразование с приостановкой;

Пример 5: ANS=000; ANE=010

”start”→AN0→приост. →”start” →AN1→ приост. →”start” → AN2→…

Запрос прерывания от АЦП обрабатывается в режиме EI2OS.

#.8. Прерывание по сервису EI2OS на примере АЦП

МК может использовать 16 независимых каналов сервиса EI2OS. Каждому каналу принадлежит дескриптор сервиса (ISD). Дескрипторы содержат по восемь байтов. Начальный адрес дескриптора определяется по формуле:

0х000100+8×ICS,

где ICS –номер канала сервиса, задаваемый в регистре управления прерываниями ICRХ.

АЦП принадлежит регистр управления прерываниями ICR10, а вектор прерывания размещается в ячейках с адресами FFFFD4…FFFFD7.

а) Последовательность шагов при запуске EI2OS в режиме одиночн. преобр.

· остановить преобразование после обработки входов AN1, AN2, AN3;

· передать данные по адресам 200…205;

· запустить преобразование программно;

· использовать высший приоритет;

· использовать 0-канал EI2OS (ICR10.[7,6,5,4]=0000).

| Установка EI2OS | MOV ICR10, #08 | установить высший приоритет, активизировать EI2OS |

| MOV BAPL, #00 MOV BAPM, #02 MOV BAPH, #00 | установка адреса приёмника | |

| MOV ISCS, #0x18 | Установить передачу слов | |

| MOVW IOA,# 0x36 | Адрес регистра данных ADC (фиксирован) | |

| MOVW DCT,# 03 | Передаются три слова | |

| Установка ADC | MOV ADCS0,#0x0B | Одиночное, AN1…AN3 |

| MOV ADCS1,#0xA2 | Запуск преобразователя | |

| Последовательность прерывания | RET |

AN1→прерывание→передача

↓

AN2→прерывание→передача

↓

AN3→прерывание→передача

↓

END→последовательность прерывания

б) Последовательность шагов при запуске EI2OS в режиме непрерывного преобр.

· преобразовать входы AN3, AN4, AN5 дважды;

· передать данные по адресам 600…60В;

· внешний запуск;

· использовать высший приоритет.

| Установка EI2OS | MOV ICR10, #08 | установить высший приоритет, активизировать EI2OS и дескриптор адреса |

| MOV BAPL, #00 MOV BAPM, #06 MOV BAPH, #00 | установка адреса приёмника | |

| MOV ISCS, #0x18 | Установить передачу слов | |

| MOVW IOA,# 0x36 | Адрес регистра данных ADC | |

| MOVW DCT,# 06 | Передаются шесть слов | |

| Установка ADC | MOV ADCS0,#0x9D | Непрерывное, AN3…AN5 |

| MOV ADCS1,#0xA2 | Запуск преобразователя | |

| Последовательность прерывания | MOV ADCS1, #00 RET | Остановка ADC |

AN3→прерывание→передача

↓

AN4→прерываниеU

|

|

Дата добавления: 2014-01-11; Просмотров: 837; Нарушение авторских прав?; Мы поможем в написании вашей работы!