КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Exit PC-CAPS

|

|

|

|

Edit database

При первом запуске имеет смысл выбрать пункт «Configure PC-CAPS» и проверить там строку «Library Filename», значение которой следует задать как *.SLB или даже ещё более конкретно - TTL.SLB, ведь другие библиотеки здесь не используются. Можно и строку «Directory path» задать в виде D:\PCAD\VITYA (для нашего примера) - тем самым вы упростите файл F31.BAT, но усложните жизнь тем пользователям, которые будут работать после вас. Лучше оставить всё как есть.

Далее следует сохранить конфигурацию и, вернувшись в стартовое меню, выбрать пункт «Edit database». Здесь под «базой данных» понимается именно схема проектируемого цифрового устройства.

Процесс построения схемы описан в отдельном методическом пособии, имеющемся в компьютерном кабинете. Здесь же мы только перечислим необходимые действия (для начала работы даже этих кратких сведений может оказаться достаточно):

· убедиться, что меню отображается зелёным цветом (если отображается красным, то выбрать в меню команду DETL);

· для того чтобы отображались точки в местах соединений будущих проводов, выбрать команду VLYR и затем включить слой с именем SDOT в положение ON;

· вернувшись в экран редактора, выбрать команду ENTR и далее (из жёлтого меню) – команду COMP;

· нажать клавишу F1 (здесь это НЕ вызов помощи!) для показа списка доступных библиотек;

· выбрать TTL.SLB;

· найти в нижней части экрана команды Page Up и Page Down, а также Exit List; просматривая список, найти нужный элемент (например, 555LN1);

· выбрав элемент щелчком (левой кнопки - ЛК) мыши, переместить его в поле чертежа, затем зафиксировать в нужном месте опять же щелчком ЛК (удерживать кнопку во время перемещения мыши не следует);

· нажатием на этот раз ПК мыши (или клавиши ESC) вновь вернуться в список элементов открытой библиотеки и таким же образом выбрать все необходимые элементы;

· завершить (Exit List) работу с библиотекой элементов;

· снова выбрать команду ENTR и на сей раз – из жёлтого меню – команду WIRE (тем самым подготовив ввод соединительных проводников);

· выполнить мышью построение необходимых схемных соединений (синие крестики на выводах компонентов должны исчезнуть);

· выбрать команду NAME и далее (из жёлтого меню) – команду NET;

· выполнить ввод имён входных (например, A, B, C), выходных (например, F), а если необходимо, то и промежуточных цепей;

· сохранить схему в файле, для чего воспользоваться командой FILE и далее (из жёлтого меню) - командой SAVE (появится запрос в нижней части экрана);

· завершить работу с PCCAPS по командам SYS и далее - QUIT.

При первом сохранении из программы PCCAPS по командам FILE – SAVE следует в ответ на запрос “Enter file name:” ввести имя файла вместе с именем своего каталога, то есть не просто F31.SCH, а именно VITYA\F31.SCH. В дальнейшем, при редактировании и внесении изменений в схему, при сохранении достаточно будет нажимать Enter.

После отработки SYS – QUIT мы вернёмся в стартовое меню PCCAPS, откуда и начали работу. Файл со схемой создан и записан, теперь можно выбрать Exit PC-CAPS.

Как только мы сделаем это, управление вернётся в файл F31.BAT, будут выполнены все промежуточные этапы, будет загружен F31.CMD и отработан логическим эмулятором PCLOGS. На экране появится долгожданный результат всей работы – временная диаграмма сигналов. В противном случае, как уже отмечалось выше, придётся искать ошибку в схеме, командных файлах или даже настройках операционной системы.

Для начала работы над новой схемой создавать новые каталоги не следует. Каждая схема (проект) будет представлена в вашем одном-единственном рабочем каталоге пятью файлами с одним именем, но пятью разными расширениями (например, F31.BAT, F31.CMD, F31.SCH, F31.NLT, F31.NET), так что перекрытия проектов не произойдёт. Для следующего проекта вы выберете другое имя, которое будет дано следующим пяти файлам. Создав BAT- и CMD-файлы один раз для первого проекта, вы будете копировать их (с переименованием) для очередных проектов, а затем редактировать их содержимое.

Сделаем ещё одно важное замечание. В библиотеке TTL.SLB существует несколько элементов и узлов цифровых схем, для корректной работы с которыми в рабочем каталоге пользователя необходимо наличие копий вспомогательных файлов с расширением MDL. Изначально эти файлы находятся в каталоге D:\PCAD. Так, если в состав схемы будет включён дешифратор 555ИД4, то в ваш рабочий каталог (VITYA, например) придётся скопировать файл 555id4.MDL, а если будет применён элемент «Исключающее ИЛИ» 555ЛП5, то придётся скопировать файл 155lp5.MDL (именно 155!). Без этих файлов программа PRESIM даже не сможет построить выходной NET-файл. Следует всегда внимательно следить за возможными сообщениями об ошибках после отработки команды PAUSE, перед запуском PCLOGS в BAT-файле.

Напоминаем, что копирование в оболочке FAR осуществляется с одной панели на другую нажатием F5. Будьте внимательны, не уничтожьте файлы MDL в их первоначальном каталоге.

Сведения об использовании команды GEN

Выше мы уже использовали конструкцию вида GEN [0 0] B (S0/2 S1/2). Возможности команды GEN не исчерпываются этим – с её помощью можно задать весьма сложную конфигурацию входного сигнала, а если нужно, то и его постоянный уровень. Параметры S0 и S1 могут встречаться в тексте команды один или более раз, причём в любых сочетаниях и в любом порядке.

Число, заданное в параметрах S0 и S1 через косую черту, означает длительность (продолжительность) периода логического нуля (S0) и единицы (S1), измеряемую в так называемых машинных циклах, или просто циклах. Продолжительность самого цикла задаётся командой CYCLE. Полезно запомнить (в примерах нижеследующих разделов это будет использовано), что при значении CYCLE 5 вся диаграмма на экране (рабочая ширина экрана) составит ровно 50 циклов (следовательно, можно будет применить команду SIM 50), а при значении CYCLE 10 – соответственно вдвое меньше, то есть команда SIM 25 заполнит диаграммой весь экран.

Пусть на какой-либо вход X надо подать постоянный логический ноль на протяжении всего процесса моделирования. Сделаем это путём указания в единственном параметре S0 значения, заведомо большего того, что задано в команде SIM:

GEN [0 0] X (S0/100)

Если понадобится постоянная логическая единица, то, очевидно:

GEN [0 0] X (S1/100)

Пусть на вход Y надо подать короткий, длительностью всего в один цикл, сигнал нуля, а затем – всё остальное время – сигнал единицы, как это делается с инверсными входами начального сброса (начальной установки) цифрового узла:

GEN [0 0] Y (S0/1 S1/100)

Пусть на вход Z надо подать такую комбинацию: ноль на протяжении первых 10 циклов, далее единица в два цикла, далее ноль в три цикла, затем единица в один цикл и далее – постоянный ноль:

GEN [0 0] Z (S0/10 S1/2 S0/3 S1/1 S0/100)

Тема 4. Минимизация (упрощение) логических функций

Представление логической функции в виде СДНФ, рассмотренное выше, не единственно возможное и, как правило, не самое короткое. Чаще всего подобную формулу удаётся упростить или, как принято говорить в алгебре логики, минимизировать. Этот процесс аналогичен упрощению обычных алгебраических выражений. Безусловно, всем студентам физического факультета памятны задачи из школьного курса алгебры под общим названием «Упростить выражение», например:

Мы применили здесь известное тождество квадрата суммы и приведение слагаемых с разными знаками. Что же может предложить нам алгебра логики? Наиболее очевидный способ состоит также в последовательном применении к исходному логическому выражению (СДНФ) различных логических тождеств. Этих тождеств существует довольно много, часть из них аналогична законам обычной (классической) алгебры, другие же весьма специфичны. Автор данного пособия не планирует превращать последнее в учебник математической логики, поэтому ниже будут приведены лишь самые основные тождества, без которых, что называется, нельзя жить. Остальные тождества можно найти в более подробной учебной литературе.

Процесс минимизации состоит в том, что к исходной СДНФ применяются эти и другие подобные тождества до тех пор, пока это возможно. Возьмём, например, ранее рассмотренную функцию (Тема 2) и преобразуем её:

В результате получилась более короткая формула, чем исходная СДНФ, соответственно и логическая схема будет проще. Попробуйте построить её самостоятельно.

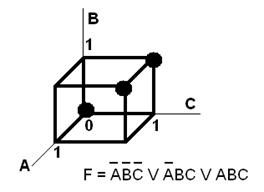

Кроме непосредственного применения логических тождеств, существуют и другие методы минимизации. В частности, довольно широко используется наглядное геометрическое представление функции трёх переменных в виде объёмной фигуры – куба. Предполагается, что куб построен с началом системы координат, расположенном в одной из вершин куба. Сами оси координат, на которых отмечены только значения 0 и 1, представляют ни что иное как значения исходных переменных-аргументов A, B, C:

Функция принимает восемь значений – у куба как раз восемь вершин. Каждая вершина изображается либо закрашенным (тёмным) кружком, если соответствующее значение функции равно 1, либо никак не отмечается, если значение равно 0. Соседние вершины, образующие одно ребро, можно склеить, представив это ребро в формуле двучленной конъюнкцией, что равнозначно применению формулы

ABC V ABC = BC · (A V A) = ВС.

Ещё лучше, если найдутся вершины, образующие целую грань – тогда можно склеить все четыре вершины, представив эту грань в итоговой формуле как одну-единственную переменную (либо её инверсию). Лишь вершины, не имеющие соседей, придётся оставить в таком виде, как они и были – в виде трёхчленных конъюнкций.

Существует и модификация этого представления для случая функции четырёх переменных – четырёхмерный гиперкуб, который в данном случае наглядно изображают в виде двух кубов, один из которых «вложен» в другой (находится внутри другого). У такой фигуры 16 вершин, отвечающих 16 значениям функции. Работа с такой фигурой выглядит уже довольно громоздко.

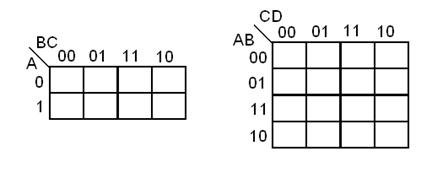

Дальнейшее развитие геометрического представления привело к появлению очень удобного метода диаграмм Вейча, или метода карт Карно, основанного на зрительном анализе развёрток многомерных кубов на плоскости, Карта Карно – это плоская таблица из восьми клеток для функции трёх переменных и из шестнадцати клеток – для функции четырёх переменных. Значения нулей и единиц над столбцами и слева от строк здесь располагаются так, чтобы при переходе от строки к строке и от столбца к столбцу всегда изменялось значение только одного разряда:

В такую таблицу сначала переносят все значения функции из таблицы истинности (все нули и единицы из столбца F), а затем приступают к построению контуров (обводов) единиц, Единицы, стоящие рядом в количестве 2, 4, или 8 и образующие один вертикальный, один горизонтальный отрезок (прямоугольник) либо квадрат, обводят общим контуром. Одна и та же единица может входить в несколько контуров:

Для каждого такого контура выписывают конъюнкцию переменных-аргументов по принципу: переменная, значение которой изменяется (с 0 на 1 или наоборот) внутри контура, НЕ ВХОДИТ в конъюнкцию (слагаемое будущей ДНФ). Сколько было контуров – столько получится и слагаемых (с учётом ни с чем не объединённых единиц). Останется только соединить эти слагаемые знаками «ИЛИ».

Тема 5. Дополнительные сведения о логических функциях

В этом разделе собраны различные полезные сведения, которые рано или поздно приходится использовать при построении логических схем.

Если в заданной таблице истинности число единиц составляет более половины общего числа строк, то сократить работу по минимизации можно за счёт того, что строить не саму функцию, а её инверсию – попросту говоря, добавить ещё один столбец, куда записать 1 в той строке, где был 0 в столбце F и наоборот. Число единиц теперь окажется существенно меньше. Построив схему для инверсной функции, надо не забыть подключить к её выходу инвертор для восстановления первоначального смысла функции.

Может случиться и так, что функция будет задана не для всех наборов исходных переменных-аргументов, которые перечислены в таблице истинности. Пусть в каком-либо календарном устройстве воскресенье кодируется как 000, понедельник – как 001 и так далее до субботы – 110. Больше дней недели нет, комбинация 111 осталась неиспользованной. При правильной работе устройства на вход блока, включающего световое табло «Сегодня мастерская не работает», никогда не будет поступать этот код 111. Для того, кто задаёт таблицу, значение функции на этом наборе безразлично.

Такого рода функции называют недоопределёнными или частично определёнными. В таблице истинности на местах неопределённых значений обычно ставят прочерки. Непосредственно построить СДНФ, а значит, и схему для такой функции нельзя. Функцию сначала надо доопределить – то есть самостоятельно заполнить позиции прочерков нулями либо единицами. Как правило, это делают так, чтобы достичь лучшей минимизации. Удобно это делать непосредственно в карте Карно – сначала перенести туда из таблицы истинности не только все нули и единицы, но и все прочерки, затем заполнить позиции прочерков так, чтобы объединялось возможно большее количество единиц.

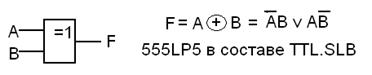

В конструкциях цифровых устройств часто находит применение ещё одна базисная функция, которую в настоящее время можно считать стандартной. Она называется «сумма по модулю 2». В случае двух (и только двух!) аргументов эта же функция именуется «Исключающее ИЛИ», «Неравнозначность», NAND. Таблица истинности этой функции была приведена выше (Тема 1). Название связано с тем, что функция в точности совпадает с результатом арифметического сложения двоичных чисел в пределах одного разряда. Отсюда широкое применение этой функции при построении разного рода счётных и суммирующих устройств, а также устройств контроля правильности передачи данных. Ниже приведено условное изображение элемента, реализующего эту функцию, и её представление в базисе И, ИЛИ, НЕ:

Если используемый логический базис дополнить этим элементом, то зачастую удаётся более экономно строить логические устройства для тех функций, которые не минимизируются или плохо минимизируются в базисе И, ИЛИ, НЕ.

Серия интегральных микросхем (ИМС) – это группа ИМС, одинаковых или схожих по используемым технологиям и имеющих одинаковые (совместимые) уровни входных и выходных сигналов, рассчитанные для совместного применения в аппаратуре. Серия, как правило, обозначается номером (например, 155, 555 или 176), а отдельные изделия – логические элементы и более крупные узлы – обозначаются сочетанием букв и цифр, например, 155ИР17 или 176ЛА1.

В библиотеке TTL.SLB размещаются модели элементов серии 555. Это отечественная серия, и её компоненты изначально обозначались русскими буквами. Однако, поскольку в библиотеках PCAD русские обозначения не допускаются, то и все обозначения, находящиеся там, получены транслитерацией (заменой русских букв на английские). Так, элемент 555ЛА3 обозначен как 555LA3, 555ИЕ7 – как 555IE7 и так далее.

Справочные данные по элементам, используемым в практикуме, и их условным обозначениям приведены в отдельном методическом пособии, которое имеется в компьютерном кабинете. Здесь же отметим, что набор логических элементов серии 555 отнюдь не исчерпывается только элементами И, ИЛИ. НЕ. Серия 555, как и другие, содержит не минимальный, а расширенный базис элементов, что позволяет более рационально строить схемы многих цифровых устройств.

Важнейшими элементами этого расширенного базиса являются инвертирующие функции (и соответственно элементы) И-НЕ и ИЛИ-НЕ. Любая из этих функций сама обладает полнотой, то есть способностью выражать какие угодно сложные логические функции только через саму себя. Таблицы истинности этих функций были приведены выше (Тема 1). Особенно часто используется сочетание элементов (функций) НЕ и И-НЕ. Есть в серии 555 и ещё более мощные комбинированные элементы, например, 555ЛР11.

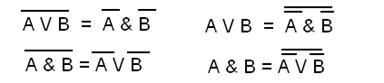

Логический элемент И-НЕ обозначается подобно элементу И, а элемент ИЛИ-НЕ – подобно элементу ИЛИ, но с очень важным (!) отличием: на выходе элемента изображается кружок – символ инверсии, как у элемента НЕ. Чтобы грамотно работать в инвертирующих базисах, надо знать логические тождества, известные как правила де Моргана.

Правила де Моргана для случая двух аргументов изображаются следующими формулами:

Формул всего две, запись справа и слева означает (по закону двойного отрицания) по сути одно и то же и приведена здесь лишь для удобства использования.

Элементы И-НЕ более эффективно реализуются интегральной технологией, чем чистые И, а также ИЛИ, поэтому после построения и минимизации логической функции имеет смысл перевести полученную формулу в базис НЕ, И-НЕ и реализовать на ИМС серии 555 именно в таком виде.

Тема 6. Пример реализации функции в инвертирующем базисе

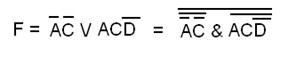

Возьмём за основу всё ту же функцию (Тема 4), получившуюся после минимизации методом Карно, и построим её схему в инвертирующем базисе.

Отметим, что функция после минимизации оказалась не зависящей от переменной В. Эта переменная является в данном случае фиктивным аргументом, то есть не влияет на результат, вырабатываемый функцией. Применяем правила де Моргана таким образом, чтобы перейти от функции ИЛИ к функции И-НЕ, для чего инвертируем каждый из операндов (слагаемых) функции ИЛИ, заменяем ИЛИ на И, после чего инвертируем весь результат.

Теперь, пользуясь другим (справочным) методическим пособием, выберем нужные элементы. С инвертором 555LN1 мы уже знакомы. Ещё нам понадобится два двухвходовых элемента И-НЕ (находим, что это 555LA3) и элемент с той же функцией, но тремя входами (это 555LA4).

Приступаем к построению схемы:

Обратите особое внимание на то, что на выходе каждого элемента присутствует кружок – символ инверсии!

Вообще с помощью правил де Моргана можно доказать справедливость следующего важного утверждения.

Если в произвольной логической схеме, состоящей только из элементов И, ИЛИ, НЕ, выполнить следующие преобразования:

· проинвертировать все входные сигналы;

· все элементы И заменить на ИЛИ;

· все элементы ИЛИ заменить на И;

· все инверторы, которые были в схеме, оставить без изменения,

· на выход схемы подключить инвертор,

то выполняемая схемой функция останется той же самой!

Следовательно, каждая логическая схема может существовать в двух вариантах - основном и двойственном (дуальном). Оба варианта логически абсолютно равноправны, но, скорее всего, окажутся различными по затратам оборудования. Какой вариант выбрать, решает сам разработчик.

Тема 7. Этапы построения логической схемы. Варианты заданий

Этап 1. Построение таблицы истинности. Формализация задания, первоначально поставленного в виде обычных фраз разговорного языка.

Этап 2.Если значения будущей функции заданы не для всех наборов, функцию придётся доопределить. Если прочерков в таблице немного, есть смысл рассмотреть все возможные варианты доопределения, иначе – доопределить нулями, чтобы по крайней мере уменьшить количество слагаемых СДНФ.

Этап 3. Выписать СДНФ прямой или, может быть, инверсной функции. Возможно, в дальнейшей работе будут участвовать несколько вариантов СДНФ.

Этап 4. Минимизировать СДНФ любыми доступными способами.

Этап 5. Реализовать построение схемы в базисе конкретной серии ИМС. Рассмотреть, если необходимо, варианты в неинвертирующем и инвертирующем базисах.

Этап 6. Оценить, если необходимо, двойственный вариант построения функции с учётом изменения числа входных и выходных инверторов.

Этап 7. Выбрать из нескольких ранее рассмотренных вариантов наилучший в определённом смысле (по оборудованию, стоимости, энергопотреблению).

Задания на разработку логической схемы для функции трёх переменных

| A | B | C | Вариант 1 | Вариант 2 | Вариант 3 | Вариант 4 | Вариант 5 | Вариант 6 |

Тема 8. Цифровые устройства без памяти

Дешифратор – устройство, преобразующее двоичный код на входах в сигнал на одном (и только одном) из нескольких выходов. Дешифратор называется полным, если он имеет N входов и 2N выходов. Если количество выходов меньше, то дешифратор называют неполным.

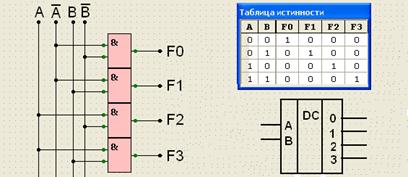

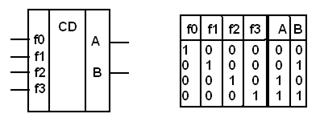

На рисунке приведена основная часть схемы (дешифрирующие элементы И) для полного дешифратора со входами A и B и четырьмя выходами, а также таблица истинности для всех выходов и условное графическое изображение дешифратора (DeCoder - DC) в целом. Видно, что единицы в таблице расположены по диагонали. При таком построении схемы (линейный дешифратор) каждый конъюнктор имеет столько входов, какова разрядность входного кода всего устройства в целом.

Дешифратор можно изготовить из отдельных логических элементов, однако существуют (в том числе и в серии 555) готовые ИМС, выполняющие эту функцию.

Задания.

1. Построить полные схемы дешифраторов «2-4» и «3-8» на логических элементах.

2. Построить схему дешифратора «2-4», имеющего (кроме входов данных) разрешающий вход E. В случае E=1 дешифратор работает как обычно, при E=0 на всех выходах дешифратора должен установиться неактивный уровень (логический 0).

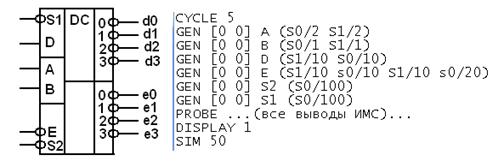

3. Исследовать работу готовой ИМС - сдвоенного дешифратора-демультиплексора 555ИД4 согласно указаниям, приведённым ниже. Не забудьте скопировать в ваш рабочий каталог файл 555id4.mdl, как было сказано выше (Тема 3).

Обсудить с преподавателем вопрос о том, почему вход разрешения D одного из дешифраторов выполнен прямым, а другого (вход E) – инверсным. Объяснить, что происходит на диаграмме (при использовании указанных на рисунке входных сигналов) на 10-м, 20-м и 30-м циклах (периодах сигнала B). Изменить CMD-файл так, чтобы на 35-м цикле работы, не изменяя сигналов D и E, одновременно выключить оба дешифратора. Переделать модель так, чтобы ИМС 555ИД4 работала как один дешифратор «3-8», Наконец, обсудить вопрос о том, почему это устройство называется также демультиплексор (после изучения мультиплексоров).

Шифратор – устройство, в определённом смысле противоположное дешифратору. Он имеет 2N входов, N выходов и преобразует сигнал на одном из входов в двоичный код на выходах. Обычно предполагается, что логическая единица может присутствовать ровно на одном из входов. Существуют также устройства, способные выделить и преобразовать в выходной код самую старшую из нескольких единиц, присутствующих во входном наборе. Такой шифратор называют приоритетным. Буквы CD в условном графическом изображении шифратора происходят от слова coder (более правильно: encoder).

Схема обычного шифратора проще схемы дешифратора в том, что первая не содержит входных инверторов, а также элементов И, поскольку нет необходимости выделять определённые сочетания нулей и единиц. Строится шифратор на элементах ИЛИ, в данном случае A = f2 V f3, B = f1 V f3. Интересно отметить, что линия f0 будет вообще никуда не подключена, так как сигналу f0 отвечает комбинация «все нули» на выходах.

Как и в случае дешифратора, существуют готовые ИМС шифраторов (как правило, приоритетных), в частности, 555ИВ1. Как и большинство других микросхем средней степени интеграции, ИМС 555ИВ1 является многофункциональным узлом, имеет вход разрешения EI (для включения в работу следует подать EI=0) и так называемый тракт групповых сигналов, выходы которого здесь рассматривать не будем.

Задания.

1. Построить схемы шифраторов «4-2» и «8-3» на логических элементах.

2. Исследовать работу готового шифратора 555ИВ1. Не забудьте скопировать в ваш рабочий каталог файл 555iv1.mdl, как было сказано выше (Тема 3).

Следует иметь в виду, что в микросхеме 555ИВ1 используется соглашение отрицательной логики, то есть уровни всех без исключения сигналов инвертированы: смысловому значению логической единицы соответствует низкий уровень напряжения (задаваемый в GEN при помощи S0), а значению логического нуля – высокий уровень (задаваемый при помощи S1). Если при работе в PCAD обозначить входные выводы как f0, f1 и так далее до f7, вход разрешения обозначить e, а выходы – a0, a1, a2, то можно для начала исследования задать следующие комбинации сигналов:

|

|

|

|

|

Дата добавления: 2014-12-07; Просмотров: 1139; Нарушение авторских прав?; Мы поможем в написании вашей работы!