КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Модуль памяти статического ОЗУ

|

|

|

|

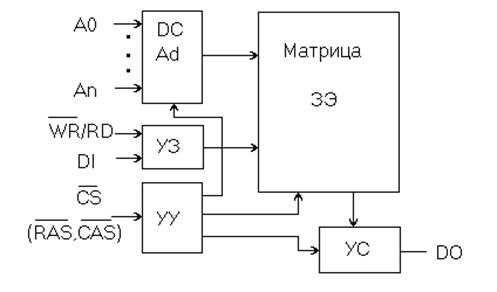

Структурная схема БИС ЗУ.

Организация БИС ЗУ.

Понятие “организация БИС ЗУ” обычно подразумевает:

─ связь между емкостью запоминающего устройства, разрядностью хранимого слова и количеством запоминаемых слов; ─ структурная и схемотехническая организация интегральной микросхемы запоминающего устройства.

Рассмотрим сначала первое понятие. Одной из важнейших характеристик микросхемы памяти является объём запоминаемой информации, который обычно задается в битах. Например: объём памяти микросхемы ─ 2048 бит. Данная характеристика дает только общее представление об объеме микросхемы. Но при этом объеме возможна различная организация:

- 2048 слов разрядностью 1 бит;

- 1024 слова разрядностью 2 бита;

- 512 слов разрядностью 4 бита;

- 256 слов разрядностью 8 бит.

В зависимости от разрядности данных (слова информации) у микросхемы будет определенное количество входов и выходов данных, количество запоминаемых слов определяет разрядность адресной шины. С другой стороны эти же характеристики микросхемы памяти однозначно связаны с ее структурной схемой.

Схема состоит из следующих основных устройств: матрица запоминающих элементов; DC Ad ─ дешифратор адреса; УЗ ─ устройство записи; УУ ─ устройство управления; УС ─ устройство считывания.

Микросхема имеет входы: A0 - An ─ адрес обращения; WR/RD ─ сигнал управления записью/чтением; DI ─ вход данных (на этот вход подаются записываемые данные); CS ─ сигнал управления доступом к микросхеме (этот сигнал характерен для статических микросхем памяти, для динамических микросхем используются сигналы RAS ─ стробирование регистра адреса строки и CAS ─ стробирование регистра адреса столбца). Имеется выход DO ─ выход данных (с этого выхода считывается выбранное слово).

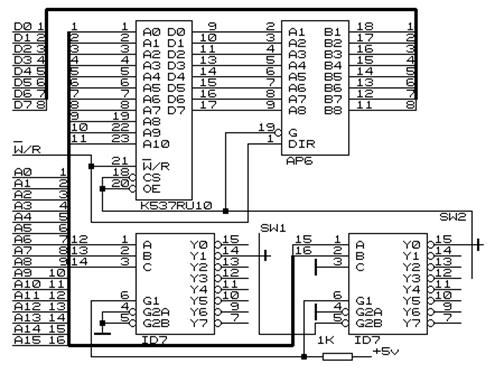

приведена схема статического оперативного запоминающего устройства на 2 килобайта, в соответствии с ранее поставленной задачей. Используемая микросхема памяти К537РУ10 имеет 11 адресных входов, два входа с обозначениями CS и OE, один вход управления записью WR/RD (низкий уровень активен для записи). Микросхема имеет двунаправленные выводы шины данных. Сигналы CS и OE, активные низким уровнем, предназначены, соответственно, для выбора микросхемы и разрешения выходов (управление третьим стабильным состоянием выходов).

Микросхема К555АП6 — двунаправленный шинный формирователь имеет двунаправленные выводы данных, сторона — А и сторона — В, вход — DIR — управление направлением передачи информации, если сигнал на этом входе имеет высокий уровень, то информация передается со стороны А на сторону В, вход G — управление выходом, если на этом входе сигнал высокого уровня, то выходы как со стороны А, так и со стороны В находятся в третьем стабильном состоянии. Это соответствует отключению модуля памяти от системной шины данных. На микросхемах К555ИД7 и переключателях SW1 и SW2 собрана схема дешифрации адресного пространства, которая позволяет расположить модуль памяти в любой части адресного пространства 16-ти разрядной шины адреса.

Разряды адресной шины А0 - А10 поданы на адресные входы микросхемы 537РУ10 для организации выбора слова, А11 - А13 поданы на входы первого дешифратора. Каждый выход первого дешифратора соответствует восьмой части адресного пространства, т.е. 8ми килобайтам. Разряды А14 и А15 поданы на входы второго дешифратора, а входы разрешения работы которого подключены через переключатель SW1 к одному из выходов первого дешифратора. Таким образом, когда первый дешифратор выбрал восемь килобайт, то два из них выбираются вторым дешифратором и переключателем SW2. Полученный сигнал подается на входы разрешения функционирования микросхемы памяти и шинный формирователь и разрешает работу схемы в конкретном адресном пространстве.

Управление записью/чтением микросхемы памяти и направлением передачи информации шинного формирователя осуществляется сигналом WR/RD, получаемым с шины управления.

Построение модуля ПЗУ отличается от рассмотренного только тем, что на него нужно подавать только управляющий сигнал RD (чтение).

|

|

|

|

|

Дата добавления: 2014-12-24; Просмотров: 2401; Нарушение авторских прав?; Мы поможем в написании вашей работы!