КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Указания и рекомендации по выполнению работы

|

|

|

|

Назначение, основные параметры и классификация СОЗУ

Тема 5.1 Оперативные запоминающие устройства статического типа СОЗУ

Тема 4.4 Регистры (1) С. 99-106.

ПР № 10 Изучение принципа работы регистров параллельного и последовательного действия

Тема 4.5 Счётчики (1) С. 106-116.

ПР № 11 Изучение принципа работы счётчика

Раздел 5 Схемотехника запоминающих устройств. (18; 6 ПР,ЛР)

ЗУ служат для хранения информации и обмена ею с другими цифровыми устройствами. Микросхемы памяти в общем объёме выпуска ИМС занимают около 40%. Важнейшие параметры ИС памяти – ёмкость, быстродействие и цена – противоречат друг другу, поэтому память организуется по многоступенчатому иерархическому принципу.

В иерархической системе памяти выделяют уровни:

- регистровые (буферные) ЗУ находятся в процессоре, имеют высокое быстродействие, но малую ёмкость и предназначены для промежуточного хранения данных при обмене между между устройствами с разным быстродействием.

- кэш-память служит для хранения копий информации, используемых в текущих операциях, размещается на кристалле, быстродействие меньше, а ёмкость больше, чем у регистровой памяти;

- основная память включает в себя оперативные, постоянные и перепрограммируемые запоминающие устройства ОЗУ, ПЗУ, РПЗУ и работает в режиме непосредственного обмена с процессором, по возможности согласована с процессором по быстродействию;

- специализированная память (многопортовая, видеопамять, ассоциативная и др.) используется в некоторых специфических архитектурах;

- внешняя память, реализуется на магнитных и оптических дисках, имеет очень большую ёмкость, но малое быстродействие.

ОЗУ подразделяются на статические СОЗУ (SRAM) и динамические ДОЗУ (DRAM). ДОЗУ по сравнению с СОЗУ имеют значительную ёмкостью и сравнительно малую стоимостью, но требуют применения регенерации (восстановления) данных.

|

|

|

Ёмкость ЗУ выражается в единицах, кратных числу 210 = 1024 = 1 К. Если ЯП состоят из одного ЗЭ, то ёмкость выражается в килобитах Kb, если ЯП содержит 8, 16, 32 ЗЭ, то ёмкость выражается в килобайтах КВ. Каждой ЯП соответствует адрес. Ёмкость ИМС

ЗУ указывается произведением двух чисел 2n×m, где 2n – число ЯП (число адресов), m – длина слова, записываемого в ЯП. Такая запись отображает организацию памяти.

2.1.2 Статические оперативные запоминающие устройства СОЗУ (Угрюмов, 221)

Запоминающими элементами СОЗУ (SRAM) служат триггеры с цепями установки и сброса. СОЗУ чаще выполняют на КМОП и n-МОП транзисторах, например ИМС серий К537 и К132.

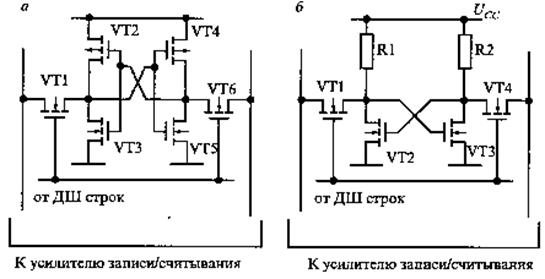

Запоминающего элемента ЗЭ КМОП (рисунок 2.1,а) содержит RS-триггер на транзис-торах VТ3 и VТ5, нагрузка которых - транзисторы VТ2 и VТ4, и ключи выборки VТ1 и VТ6. ЗЭ образуют строку, которую называют ячейкой памяти ЯП. Каждый ЗЭ через ключи VТ1 и VТ6 соединён с вертикальными линиями записи/считывания ЛЗС. Правая линия – ЛЗС в прямом коде, слева – в инверсном.

ЛЗС образуют многоразрядную шину записи/считывания, по числу ЗЭ в ЯП. Линия – «от ДШ (дешифратора) строк» - линия выборки ЛВ.

Рисунок 2.1 - а) Запоминающий элемент КМОП транзисторах; б) ЗЭ n-МОП

СОЗУ работают в режимах хранения, записи и считывания.

В режиме хранения на ЛВ поддерживается низкий потенциал, ключи VТ1 и VТ6 закрыты, RS-триггер сохраняет ранее установленное состояние.

В режиме выборки (считывания) ключи VТ1 и VТ6 открываются сигналом от ДШ строк и выходы триггера подключаются к линиям записи/считывания ЛЗС через ключи VТ1 и VТ6. Записанное в ЗЭ число «0» или «1» усиливается усилителем считывания и поступает в процессор.

В режиме записи ключи VТ1 и VТ6 открыты, выходы триггера подключены к ЛЗС, усилитель записи формирует на них сигналы, которые устанавливают триггер в соответ-ствующее состояние. При подаче «0» на правую ЛЗС Т3 запирается и открывается VТ5, который фиксирует нулевое состояние триггера. При подаче «1» - на правой ЛЗС фиксируется «1».

|

|

|

ЗЭ на n-МОП транзисторах (рисунок 2.1, б) занимают наименьшую площадь поверхности кристалла.

5.1.3 Структура, принцип построения БИС ОЗУ, УГО

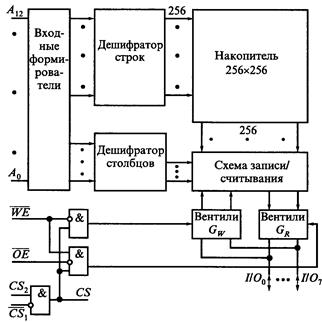

На рисунке 2.2, а приведена структурная схема БИС статического ОЗУ, содержащего 4096 однобайтовых ячеек памяти. В состав БИС входят: дешифраторы адреса строк и столбцов; входные формирователи; накопитель, содержащий 256×256 ЗЭ; схема записи /считывания; вентили ввода/вывода GW и GR; логика управления. Вентили GW, GR обес-печивают три режима работы выходных каскадов «чтение», «запись» и «отключено».

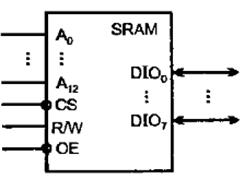

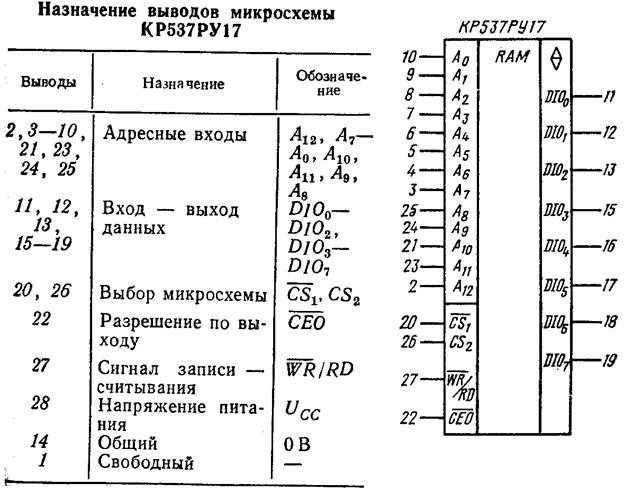

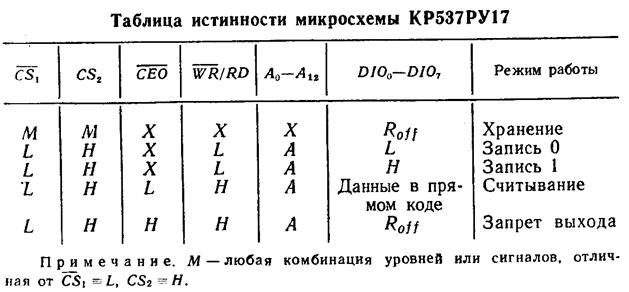

Назначение выводов и сигналов. А0…А12 – (Address) выводы шины адресы; IO0… IO7 – выводы шины данных; CS (или СЕ) – сигнал разрешения или запрета доступа к памяти; OE – сигнал разрешения чтения (считывания); WE – сигнал разрешения записи.

Выводы могут быть обозначены несколько по-другому:

DI (Data Input) - входы данных; DO (Data Out) - выходы данных; W/R (Write/Read) - сигнал записи данных при W/R = 0 или считывания при W/R = 1; CS (Chip Select) или

CE (Chip Enable) - сигнал разрешения при CS (CE) = 0 или запрета при CS (CE) = 1 работы данной микросхемы.

Рисунок 2.2 – а) Структурная схема статического ОЗУ (БИС К537РУ17); б) условное графическое изображение БИС СОЗУ

Для уменьшения числа выводов микросхем широко применяется мультиплексиро-вание, то есть одни и те же выводы ИМС могут использоваться как входные и выход-ные для адреса, данных или управляющих сигналов.

Например, 16-разрядный адрес А = А15…А0 может делиться на полуадресы: старший

байт АСТ = А15…А8 и младший байт АМЛ – А7…А0, которые подаются на одни и те же входы ИМС. В динамических ОЗУ подача старшего байта сопровождается сигналом RAS (Row Address Strobe), а младшего – сигналом CAS (Colum Address Strobe). Выводы входа DI и выхода DO также могут объединяться в общий вывод DIO.

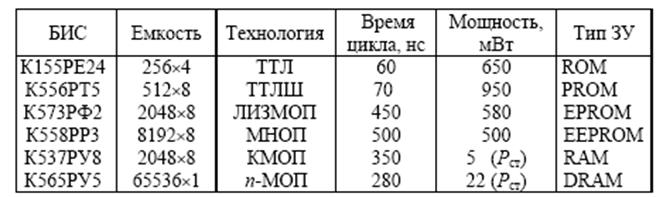

Таблица – Параметры некоторых ИМС памяти

ПРАКТИЧЕСКАЯ РАБОТА № 12

Цель: Отработать навыки синтеза схем памяти и пользования справочными

|

|

|

материалами, закрепить теоретические знания.

Задание:

1. Составить схему модуля СОЗУ ёмкостью 32 килобайт, используя ИМС

ОЗУ ёмкостью 8 Кбайт К537РУ17. Указать на схеме линии питания.

2. Привести комбинацию сигналов, необходимых для считывания байта

по адресу 1 ЕЕЕ

3. Привести комбинацию сигналов, необходимых для записи АА

по адресу 2 ВВВ.

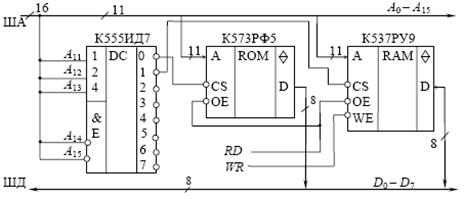

1. При составлении схемы модуля памяти в качестве образца использовать схему

организации блока памяти. На этой схеме приведён вариант подключения микросхем памяти к системной магистрали МП, имеющего 16-разрядную шину адреса и 8-раз-рядную шину данных.

Каждая ИМС образует страницу памяти ёмкостью 2 Кб, выбор нужной ячейки осуществляется с помощью адресных сигналов А0-А10. Выбор нужной страницы осуществляет дешифратор К555ИД по состоянию старших разрядов адресной шины А11-А15. В примере ячейки ОЗУ и ПЗУ занимают в адресном пространстве МП области: 0000Н – 07FFН и 0800Н – 0FFFН, соответственно.

Команды записи формирует строб WR, команды чтения – строб RD. Выходы дешифратора позволяют добавить к блоку памяти ещё шесть страниц ОЗУ или ПЗУ.

Схема организации блока памяти

2. УГО ИМС вычерчивать аккуратно, в соответствии с ГОСТ; входы и выходы

ИМС, шины, типы ИМС обозначать так же, как в приводимом примере.

3. Раскрыть обозначения управляющих сигналов.

Содержание отчёта.

Тема и цель работы, схема модуля памяти, комбинации сигналов необходимых

для считывания и записи в соответствии с заданием.

Контрольные вопросы.

1. Назначение выводов ИМС DIO; CS; CEO; WR; RD; UCC.

2. Привести комбинацию сигналов, необходимых для хранения данных.

ПР № 12. Построение модуля СОЗУ заданной ёмкости

КР537РУ17 Статическое асинхронное ОЗУ на основе КМОП-структур. Организация

памяти 8192×8 разрядов. Время выборки адреса не более 200 нс. Потребляемая мощность в режиме обращения 470 мВт, в режиме хранения 22 мВт. Совместимость по входу и выходу с ТТЛ и КМОП схемами. Выход – с тремя состояниями.

|

|

|

|

|

Дата добавления: 2015-06-27; Просмотров: 1514; Нарушение авторских прав?; Мы поможем в написании вашей работы!