КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Условное обозначение ЭСЛ приведено на рисунке 5.3

|

|

|

|

5.4 Логические элементы на МДП- транзисторах

а) схема инвертора на МДП приведена на рисунке 5.4.

Транзистор VT1 работает в ключевом режиме, VT2 – всегда в активном. VT2 является нелинейной нагрузкой.

Транзистор VT1 работает в ключевом режиме, VT2 – всегда в активном. VT2 является нелинейной нагрузкой.

При запертом VT1 транзистор VT2 ‑ в активном режиме, ближе к насыщению, при насыщенном VT1 транзистор VT2 – в активном, ближе к отсечке. При подаче на вход х низкого уровня напряжения VT1 запирается, VT2 близок к насыщению, на выходе ключа высокий уровень напряжения. При подаче на вход х высокого уровня напряжения VT1 отпирается, VT2 близок к отсечке, на выходе ключа низкий уровень напряжения. Выполняется операция  ;

;

б) в двухвходовой схеме ИЛИ-НЕ (рисунок 5.5) входные транзисторы VT1 и VT2 соединены параллельно. Если хотя бы на один из входов подан высокий уровень напряжения, соответствующий транзистор отпирается, и на выходе

б) в двухвходовой схеме ИЛИ-НЕ (рисунок 5.5) входные транзисторы VT1 и VT2 соединены параллельно. Если хотя бы на один из входов подан высокий уровень напряжения, соответствующий транзистор отпирается, и на выходе  схемы будет низкий уровень. И только при подаче на все входы схемы низкого уровня транзисторы VT1 и VT2 запрутся, и на выходе появится высокий уровень. Выполняется

схемы будет низкий уровень. И только при подаче на все входы схемы низкого уровня транзисторы VT1 и VT2 запрутся, и на выходе появится высокий уровень. Выполняется  ;

;

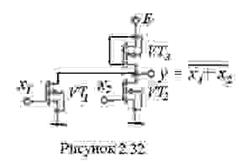

в) в двухвходовой схеме И-НЕ (рисунок 5.6) входные транзисторы VT1 и VT2 соединены последовательно. Если хотя бы на один из входов подан низкий уровень напряжения, соответствующий транзистор запирается, ток через входные транзисторы не течет, и на выходе схемы будет высокий уровень. И только при подаче на все входы схемы высокого уровня транзисторы VT1 и VT2 откроются, течет ток, и на выходе будет низкий уровень. Выполняется операция  .

.

|

|

|

|

|

Дата добавления: 2017-02-01; Просмотров: 69; Нарушение авторских прав?; Мы поможем в написании вашей работы!