КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

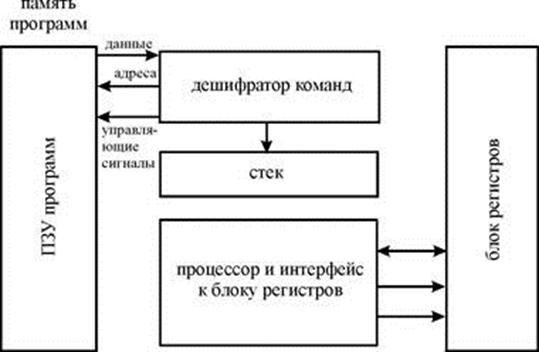

Гарвардская архитектура

Гарвардская архитектура была разработана Говардом Эйкеном в конце 1930-х годов в Гарвардском университете с целью увеличить скорость выполнения вычислительных операций и оптимизировать работу памяти.

Типичные операции (сложение и умножение) требуют от любого вычислительного устройства нескольких действий: выборку двух операндов, выбор инструкции и её выполнение, и, наконец, сохранение результата. Соответствующая схема реализации доступа к памяти имеет один очевидный недостаток — высокую стоимость. При разделении каналов передачи адреса и данных на кристалле процессора, последний должен иметь в два раза больше выводов. Способом решения этой проблемы стала идея использовать общую шину данных и шину адреса для всех внешних данных, а внутри процессора использовать шину данных, шину команд и две шины адреса. Такую концепцию стали называть модифицированной Гарвардской архитектурой.

Часто требуется выбрать три составляющие — два операнда и инструкцию(в алгоритмах цифровой обработки сигналов это наиболее встречаемая задача в БПФ и КИХ, БИХ фильтрах). Для этого существует кэш-память. В ней может храниться инструкция — обе шины остаются свободными, и появляется возможность передать два операнда одновременно. Использование кэш-памяти вместе с разделёнными шинами получило название «Super Harvard Architecture» («SHARC») — расширенная Гарвардская архитектура.

Примером могут послужить процессоры «Analog Devices»: ADSP-21xx — модифицированная Гарвардская Архитектура, ADSP-21xxx(SHARC) — расширенная Гарвардская Архитектура.

|

|

Дата добавления: 2014-01-14; Просмотров: 1565; Нарушение авторских прав?; Мы поможем в написании вашей работы!