КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Лекция 10. Статические ОЗУ. Микросхемы ПЗУ

|

|

|

|

Выход

Вход

- AH = 62H DOS 3.0+

- BX = сегментный адрес PSP выполняющейся программы

Описание:

Эта функция возвращает в BX адрес PSP текущей программы. используется, чтобы получить адрес параметров командной строки, адрес окружения DOS и другой полезной информации в PSP.

Версии:

доступна, начиная с DOS 3.0

Статические ОЗУ. Структурная схема статического ОЗУ приведена на рис. 1. Основой статического ОЗУ является накопитель или матрица памяти, состоящая из отдельных запоминающих (бистабильных) ячеек. Обычно в качестве этих ячеек используются различного рода триггеры. Двоичная информация, записанная в такую ячейку, может сохраняться в этой ячейке до тех пор, пока не будет заменена другой или не будет, снято напряжение питания.

Таблица 1. Основные классификационные параметры ЗУ

| Параметр | Обозначение | Определение |

| Информационная емкость | N | Число бит памяти в накопителе ЗУ |

| Число слов в ЗУ | п | Число адресов слов в накопителе ЗУ |

| Разрядность | т | Число разрядов в накопителе ЗУ |

| Коэффициент разветвления по выходу | Кp | Число единичных нагрузок (входов других ИМС), которые можно одновременно подключить к выходу ЗУ |

| Число циклов перепрограммирования | ncy | Число циклов запись-стирание, при котором сохраняется работоспособность ЗУ |

| Потребляемая мощность | рсс | Потребляемая ЗУ мощность в установленном режиме работы |

| Потребляемая мощность в режиме хранения | pccs | Мощность, потребляемая ЗУ при хранении информации в режиме невыбора |

| Время хранения информации | tSG | Интервал времени, в течение которого ЗУ в заданном режиме сохраняет информацию |

Таблица 2. Статические параметры ЗУ

| Параметр | Обозначение | Определение |

| Напряжение питания | Ucc | Напряжение источника питания ЗУ |

| Ток потребления | Icc | Ток, потребляемый ЗУ от источника питания в заданном режиме |

| Напряжение питания в режиме хранения | Uccs | Напряжение питания ЗУ в режиме хранения информации |

| Ток потребления в режиме хранения | Iccs | Ток, потребляемый ЗУ в режиме хранения информации |

| Напряжение логической «1» | UH | Напряжение сигнала на входе или на выходе, соответствующее логической единице |

| Напряжение логического «0» | UL | Напряжение сигнала на входе или на выходе, соответствующее логическому нулю |

При использовании такого накопителя приходится решать две задачи:

• выбор конкретной ячейки накопителя, в которую будет записана или из которой будет считана информация;

• что нужно сделать — записать или прочитать информацию в ячейке. Первая задача решается с помощью адресации всех ячеек накопителя. Вторая задача решается переводом ячейки памяти в режим записи или считывания по сигналу на входе схемы управления.

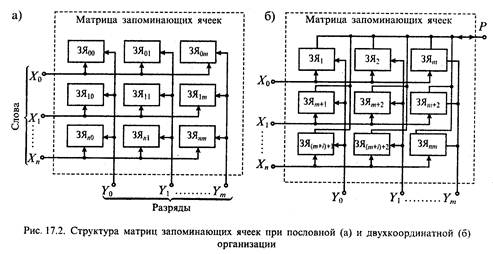

Накопитель или матрица памяти состоит из п строк. В состав каждой строки входят m запоминающих ячеек, образующих m-разрядное слово. Информационная емкость накопителя равна N=nm, где п — число строк (или слов), т — число столбцов (или разрядов). Соответствующие шины в накопителе управляются от дешифраторов строк (X) и столбцов (Y), на входы которых поступают адресные сигналы ао... An. При записи и считывании осуществляется обращение (выборка) к одной или нескольким запоминающим ячейкам одновременно. Дешифраторы строк и столбцов выполняют выбор требуемых ячеек памяти с помощью адресных сигналов Х0...Хп и Y0...Ym }"„,.

Такая матрица запоминающих ячеек (ЗЯ) может работать в двух режимах: пословном и двухкоординатном. Структура пословной матрицы приведена на рис. 17.20. Как видно из схемы, адресные шины Х0...Хп электрически связаны с каждой ЗЯ одного слова, в то время как рязрядные шины Y0...Ym, имеют связь с ЗЯ одноименного разряда всех слов. При наличии в адресной шине X, сигнала выбора i - го слова, соответствующего высокому уровню, состояние каждой ячейки в этом слове может быть считано по разрядным шинам Y0...Ym. Если необходимо записать информацию по выбранному адресу Хi, то на разрядные шины Y0...Ym подаются соответствующие электрические сигналы, которые подводятся ко всем ЗЯ i -й строки (слова).

При работе матрицы ЗЯ в двухкоординатном режиме с помощью шин строк и столбцов выбирается любая ячейка матрицы. В этом случае разрядная шина Р, которая является общей для всех ЗЯ, используется как для записи, так и для считывания информации в адресованных ЗЯ.

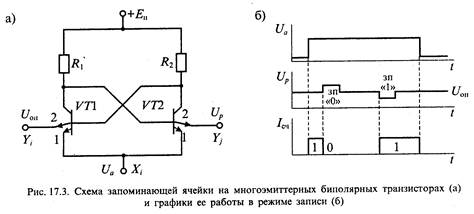

Простейшей ЗЯ является схема RS-триггера, построенная на двух многоэмиттерных биполярных транзисторах VT2 и VT1, изображенная на рис. 17.30. Первые эмиттеры обоих транзисторов соединены с адресной шиной Хi потенциал которой Uа в установившемся состоянии должен быть самым низким. Вторые эмиттеры этих транзисторов присоединены к разрядным шинам Yi и Yj. На разрядной шине Yi установлено опорное напряжение Uоп а на шину Yj подается напряжение Up. Режим работы схемы зависит от соотношения между напряжениями Uоп, Up, и Uа.

В режиме хранения информации выполняется условие Uа < Uоп = Up. В этом случае схема находится в одном из устойчивых состояний, при котором открытым может быть транзистор VT2 или VT1. Ток протекает по первому эмиттеру открытого транзистора, а вторые эмиттеры обесточены. Например, если в триггер записана логическая 1, то транзистор VT2 открыт, а транзистор VT1 закрыт. В этом случае за логическую единицу принимается наличие тока в транзисторе VT2.

В режиме считывания с помощью адресного сигнала X, на шине устанавливается напряжение Uа > Uоп = Up. Если в триггер записана логическая 1, то ток открытого транзистора VT2 потечет в разрядную шину Yj,. Наличие тока в разрядной шине соответствует считыванию 1, а его отсутствие соответствует логическому 0.

Условия режима записи зависят от состояния, в которое необходимо установить ЗЯ. Если триггер находился в состоянии 1 (транзистор VT2 открыт, транзистор VT1 — закрыт), то для записи 0 необходимо по разрядной шине Yj, подать напряжение Up > Uоп, сохраняя условие Uа > Up. При этом триггер перейдет в новое состояние, при котором транзистор VT2 закроется, а транзистор VT1 откроется. Для записи в ЗЯ логической 1 на шину Yj следует подать напряжения Up > Uоп, и обеспечить условие Ua > Uоп. Временные диаграммы работы ЗЯ в режимах записи логического нуля или единицы приведены на рис. 17.3 б.

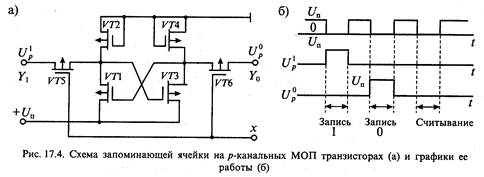

Запоминающая ячейка на RS -триггере, выполненном на n-канальных МОП транзисторах, приведена на рис. 17.4 а. Триггер образован транзисторами VT1,..., VT4. Переключение триггера для записи и считывания выполняется транзисторами VT5 и VT6. Временные диаграммы работы триггера изображены на рис. 17.4 б.

В исходном состоянии напряжения на разрядных шинах U1p и U°p равны нулю, а на шине слова Х установлено напряжение питания En. При этом транзисторы VT5 и VT6 закрыты, так как напряжение между затворами и истоками меньше порогового напряжения, и триггер находится в одном из устойчивых состояний, например, транзистор VT3 открыт, а транзистор VT1 закрыт.

Для записи логической 1 в ЗЯ на шину слова подается отрицательный сигнал, изменяющий напряжение в ней до нуля. Одновременно в разрядную шину 71 подается положительный сигнал, изменяющий напряжение в ней до напряжения питания Un. При этом транзистор VT5 открывается и положительный сигнал подается на затвор VT3, запирая его. После запирания транзистора V73 отпирается транзистор VT1 и на его стоке устанавливается положительное напряжение, что соответствует состоянию логической 1.

Для записи логического нуля в ЗЯ на шине слова устанавливается нулевое напряжение, а напряжение питания подается на разрядную шину 70. При этом транзистор VT6 открывается и положительное напряжение через него подается на затвор VT, запирая его, что приводит к отпиранию транзистора VT3.

Для считывания информации, записанной в ЗЯ, нужно подать отрицательный сигнал только на шину слова, изменив в ней напряжение до нуля. При этом оба транзистора VT5 и VT6 открываются и через транзистор, подключенный к триггеру с положительным напряжением, протекает ток, поступающий в соответствующую разрядную шину.

Устройство управления определяет режим работы схемы ОЗУ. По сигналу CS разрешаются или запрещаются операции записи и считывания. Сигнал CS позволяет выбрать требуемую микросхему памяти в ЗУ, состоящем из ряда микросхем. Подача сигнала на вход WR/RD при наличии сигнала CS = 0 выбора микросхемы позволяет выбрать режим записи, если WR/RD = 0, или считывания, если WR/RD =1. 1

Данные, подлежащие записи, поступают на вход DI, а данные, подлежащие чтению, снимаются с выхода DO. Устройства записи и считывания обеспечивают прием и выдачу сигналов информации с уровнями, согласующимися с серийными цифровыми микросхемами.

По режиму питания статические ОЗУ можно разделить на группы с активным и активно-пассивным режимами питания. При активном режиме питания накопитель и схема управления потребляют практически одинаковую мощность при всех операциях: записи, считывания и хранения информации. При активно-пассивном режиме питания некоторые узлы переходят в режим малого потребления или полностью отключаются, если микросхема находится в режиме хранения информации. В результате при хранении информации потребляемая микросхемой мощность уменьшается. При переходе в режим записи или считывания напряжения и токи питания восстанавливаются до номинальных значений. Использование активно-пассивного режима питания в несколько раз уменьшает среднюю мощность, потребляемую микросхемой. По этой причине большинство микросхем ОЗУ используют такой режим.

Постоянные запоминающие устройства. Микросхемы ПЗУ можно разделить на две группы: однократно программируемые и перепрограммируемые. В первом типе ПЗУ информация после записи меняться не может, и микросхема работает только в режиме считывания. Структурная схема ПЗУ приведена на рис. 17.6. От схемы ОЗУ, приведенной на рис. 17.1, эта схема отличается отсутствием устройства записи и линий, которые его обслуживают. Кроме того, изменяется выполнение накопителя (матрицы памяти). В настоящее время находят применение два типа накопителей ПЗУ: масочные и программируемые.

В масочных ПЗУ (МПЗУ) накопитель программируется на стадии изготовления, когда информация, записываемая в него, определяется построением одного из слоев схемы при помощи специального фотошаблона.

В программируемых ПЗУ (ППЗУ) накопитель выполняют на базе ЗЯ с плавкими перемычками; их упрощенная схема приведена на рис. 17.7. При программировании эти плавкие перемычки пережигают с помощью специального программирующего устройства. Сами плавкие перемычки изготовляют из нихрома или других тугоплавких материалов и защищают специальным диэлектриком, обеспечивающим надежность в условиях повышенной влажности. Процесс записи информации в схему представляет собой избирательное разрушение плавких перемычек током, обеспечиваемым устройством программирования. На рис. 17.7 плавкие перемычки ПП показаны в виде предохранителей, включенных в эмиттеры многоэмиттерных транзисторов УТц. -. VT^. Программируемые элементы включены между эмиттерами транзисторов матриц и разрядными шинами. Наличие перемычки соответствует логическому 0 на выходе усилителя считывания, а отсутствие перемычки — логической единице. Пережигание перемычек в режиме программирования выполняется серией импульсов по специальной программе.

Для повышения надежности работы ПЗУ методика программирования предусматривает подачу серии 40... 100 импульсов после фиксации момента пережигания перемычки, а также, обязательную термотренировку запрограммированного ПЗУ при определенной температуре (около 100°С) в заданном электрическом режиме.

Репрограммируемыс ПЗУ (РПЗУ). Репрограммируемые ПЗУ делятся на две группы: 1) с электрическим программированием и ультрафиолетовым стиранием EPROM; 2) с электрическим программированием и электрическим стиранием EEPROM. К последней группе также относятся РПЗУ с избирательным стиранием

EAROM.

Запоминающие ячейки РПЗУ строятся на п-МОП или КМОП транзисторах. Для построения ЗЯ используются различные физические явления хранения заряда на границе между двумя различными диэлектрическими средами или проводящей и диэлектрической средой.

В первом случае диэлектрик под затвором МОП транзистора делают из двух слоев: из нитрида кремния и двуокиси кремния. Такая структура называется МНОП: металл — нитрид кремния —окисел — полупроводник. В такой структуре при высоком напряжении на затворе (около 30 В) происходит туннельное перемещение носителей заряда через слой двуокиси кремния, который делается очень тонким (до I ohm), к границе двух диэлектриков, вблизи которой имеется много ловушек

для носителей заряда. В результате внутри МОП структуры образуется некоторый заряженный слой, который приводит к изменению порогового напряжения МОП транзистора. При постоянном напряжении на затворе в режиме считывания информации это приводит к изменению тока считывания.

Во втором случае затвор МОП транзистора делают плавающим, т. е. не связанным с другими элементами схемы. Такой затвор заряжается током лавинной инжекции при подаче на сток транзистора высокого напряжения (также около ЗОВ). В результате плавающий затвор начинает влиять на ток стока, что и используется при считывании информации. Такие РПЗУ обычно называют выполненными по структуре ЛИПЗ (лавинно-инжекционные с плавающим затвором).

Поскольку затвор транзистора со всех сторон окружен изолирующим слоем, ток утечки очень мал и хранение информации достаточно длительное (десятки лет). Для стирания информации в таких приборах пользуются облучением кристалла через специальное прозрачное окно в корпусе микросхемы ультрафиолетовым светом. Облучение ультрафиолетовыми лучами приводит к резкому увеличению тока утечки, что способствует рассасыванию носителей заряда. Такие микросхемы получили название РПЗУ УФ или EPROM.

Другой способ перезаписи информации используется в РПЗУ с электрическим программированием. Он основан на размещении над плавающим затвором второго— управляющего — затвора. Подача напряжения на управляющий затвор приводит к рассасыванию заряда за счет туннельного эффекта. Эти РПЗУ называются EEPROM и имеют несомненные преимущества перед РПЗУ УФ, так как истребуют при перепрограммировании специальных источников ультрафиолетового света. Структурная схема такого РПЗУ с шинным управлением приведена на рис. 17.8.

Интегральные микросхемы ЗУ. Промышленность выпускает большое количество различных микросхем ЗУ, отличающихся информационной емкостью, организацией, технологией изготовления. Условное схематичное изображение микросхемы статического ОЗУ приведено на рис. 17.9 а. Функциональное назначение ИМС указывается обозначением RAM.

Отдельные типы микросхем ОЗУ могут иметь выходные каскады с тремя состояниями или с открытым коллектором. Применение микросхем с тремя состояниями выхода или с открытым коллектором (открытым эмиттером) позволяет создавать модули ЗУ с различными параметрами.

Условные схематичные изображения динамического ОЗУ и ПЗУ приведены на рис. 17.9 б и в.

|

|

|

|

|

Дата добавления: 2014-01-20; Просмотров: 2585; Нарушение авторских прав?; Мы поможем в написании вашей работы!