КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Транзакции шины PCI

|

|

|

|

Факультативные сигналы шины PCI

| Сигнал | Количество Задающее линий устройство | Подчиненное Комментарий устройство |

| REQ64# | 1 X | Запрос на осуществление 64-битной транзакции |

| АСК64# | Разрешение 64-битной транзакции | |

| AD | 32 х | Дополнительные 32 бита адреса или данных |

| PAR64 | 1 X | Проверка четности для дополнительных 32 битов адреса или данных |

| С/ВЕ# | 4 х | Дополнительные 4 бита для указания, какие байты из слова нужно считать (или записать) |

| LOCK | 1 X | В многопроцессорных системах: блокировка шины при осуществлении транзакции одним из процессоров |

| SBO# | Обращение к кэш-памяти другого процессора | |

| SDONE | Отслеживание адресов, по которым произошли изменения, завершено. | |

| INTx | Запрос прерывания | |

| JTAG | „ Сигналы тестирования IEEE 1149.1 JTAG | |

| M66EN | Сигнал связывается с источником питания или с «землей» (66 МГц или 33 МГц) |

Сигналы REQ# и GNT# предназначены для арбитража шины. Они устанавливаются не тем устройством, которое является задающим в данный момент, а тем, которому нужно стать задающим. Последний обязательный сигнал, RST#, используется для перезагрузки системы, которая происходит, либо если пользователь нажмет кнопку RESET, либо если какое-нибудь системное устройство обнаружит фатальную ошибку. После установки этого сигнала компьютер перезагружается.

Перейдем к факультативным сигналам, большинство из которых связано с расширением разрядности с 32 до 64 битов. Сигналы REQ64# и АСК 64# позволяют задающему устройству попросить разрешение осуществить 64-битную транзакцию, а подчиненному устройству принять эту транзакцию. Сигналы AD, PAR64 и С/ВЕ# являются расширениями соответствующих 32-битных сигналов.

Следующие три сигнала не связаны с противопоставлением 32 бита — 64 бита. Они имеют отношение к многопроцессорным системам. Не все платы PCI поддерживают такие системы, поэтому эти сигналы являются факультативными. Сигнал LOCK позволяет блокировать шину для параллельных транзакций. Следующие два сигнала связаны с отслеживанием всех адресов, по которым происходит изменение данных. Подобное отслеживание необходимо для того, чтобы сохранить непротиворечивость кэш-памяти различных процессоров.

Сигналы ШТХ нужны для запроса прерываний. Плата PCI может содержать до четырех логических устройств, каждое из которых имеет собственную линию запроса прерывания. Сигналы JTAG предназначены для процедуры тестирования IEEE 1149.1 JTAG. Наконец, сигнал M66EN связывается либо с источником питания, либо с «землей», что определяет тактовую частоту. Она не должна меняться во время работы системы.

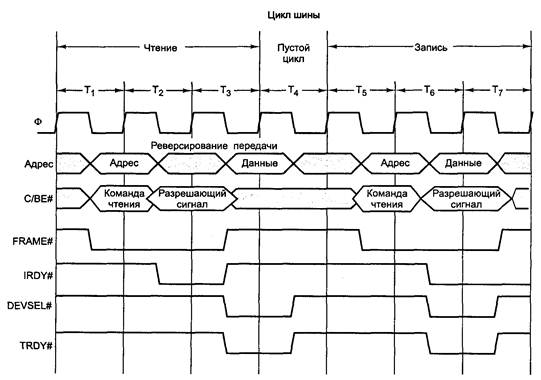

Шина PCI в действительности очень проста. Чтобы лучше понять это, рассмотрим временную диаграмму на рис. 3. Здесь мы видим транзакцию чтения, за ней следует пустой цикл и транзакция записи, которая осуществляется тем же задающим устройством.

Во время цикла Ti на заднем фронте синхронизирующего сигнала задающее устройство помещает адрес на линии AD и команду на линии С/ВЕ#. Затем задающее устройство устанавливает сигнал FRAME#, чтобы начать транзакцию.

Во время цикла Т2 задающее устройство переключает шину, чтобы подчиненное устройство могло воспользоваться ею во время цикла Тз. Задающее устройство также изменяет сигнал С/ВЕ#, чтобы указать, какие байты в слове ему нужно считать.

Во время цикла Т3 подчиненное устройство устанавливает сигнал DEVSEL#. Этот сигнал сообщает задающему устройству, что подчиненное устройство получило адрес и собирается ответить. Подчиненное устройство также помещает данные на линии AD и выдает сигнал TRDY#, который сообщает задающему устройству о данном действии. Если подчиненное устройство не может ответить быстро, оно не снимает сигнал DEVSEL#, который сообщает о его присутствии, но при этом не устанавливает сигнал TRDY# до тех пор, пока не сможет передать данные. При такой процедуре вводится один или несколько периодов ожидания.

Рис. 3. Примеры 32-битных транзакций в шине PCI. Во время первых трех циклов происходит операция чтения, затем идет пустой цикл, а следующие три цикла — операция записи

В нашем примере (часто это бывает и в действительности) следующий цикл пустой. Мы видим, что в цикле Т5 то же самое задающее устройство инициирует процесс записи. Сначала оно, как обычно, помещает адрес и команду на шину. В следующем цикле оно выдает данные. Поскольку линиями AD управляет одно и то же устройство, цикл реверсирования передачи не требуется. В цикле Т7 память принимает данные.

|

|

|

|

|

Дата добавления: 2014-01-20; Просмотров: 1328; Нарушение авторских прав?; Мы поможем в написании вашей работы!