КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Синхронные счетчики. Счетчики с цепью группового переноса

|

|

|

|

В счетчиках с групповым переносом разряды разбиваются на группы (например, n разрядов разбиваются па m групп). В пределах одной группы обычно организуется параллельный перенос, а между группами - последовательный или сквозной. По такому принципу строятся и счетчики для систем счисления с основанием K > 2. В этом случае роль групп выполняют K-ичные разряды.

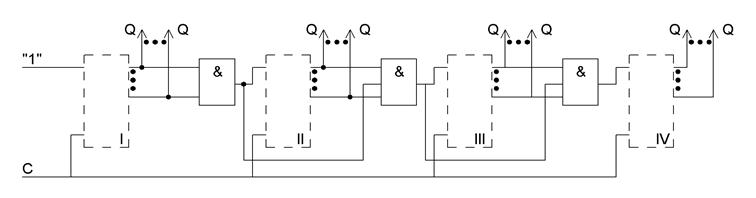

1. Суммирующий счетчик с групповым параллельным переносом на элементах И.

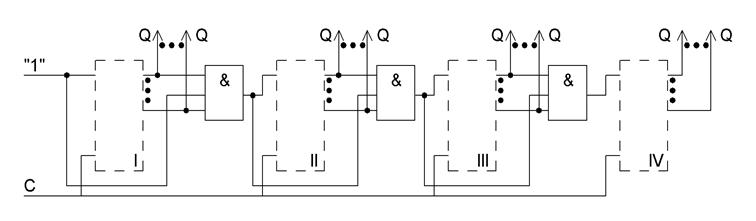

2. Вычитающий счетчик с групповым сквозным переносом на элементах И.

31. Схемотехника счетчиков с цепями переноса.

По способу организации цепей переноса (заема) между разрядами сч. подразделяются на следующие типы: с последовательным переносом; со сквозным переносом; с параллельным переносом; с групповым переносом. В сч. с последовательным переносом перенос (заем) в соседний старший разряд формируется только после переключения триггера в предыдущем разряде, т. е. триггеры переключаются не одновременно. При проектировании таких сч. возникают трудности, связанные с необходимостью анализа не только логического уровня сигналов, формирующихся в схеме, но и моментов изменения уровней сигналов. На рис. 1 предст. фун. схема n-разрядного суммирующего сч. с посл. переносом, построенного на синхронных T-триггерах, которые переключаются по отрицательному перепаду такт. сигнала. Врем. диаг. изм. сигн. на выходах Qi(i=1..3), без учета времени перекл. триг.) показана на рис. 2.

|

|

В сч. с параллельным переносом аргументами функций переносов для каждого разряда являются только сигналы на выходах триггеров соответствующих разрядов. Переносы для всех разрядов счетчика формируются одновременно (при условии, что все логические элементы в схеме имеют одинаковое время переключения). Цепи сквозного переноса организуются таким образом, чтобы функция переноса i-го разряда счетчика являлась аргументом функции переноса i+1-го разряда. В этом случае сигналы переносов для каждого разряда формируются поочередно, начиная с младших разрядов счетчика. Счетчики со сквозным переносом требуют меньшего числа входов логических элементов для организации цепей переноса, но уступают счетчикам с параллельным переносом в быстродействии. В счетчиках с групповым переносом разряды разбиваются на группы (например, n разрядов разбиваются па m групп). В пределах одной группы обычно организуется параллельный перенос, а между группами - последовательный или сквозной. По такому принципу строятся и сч. для систем счисления с основанием K > 2. В этом случае роль групп выполняют K-ичные разряды.

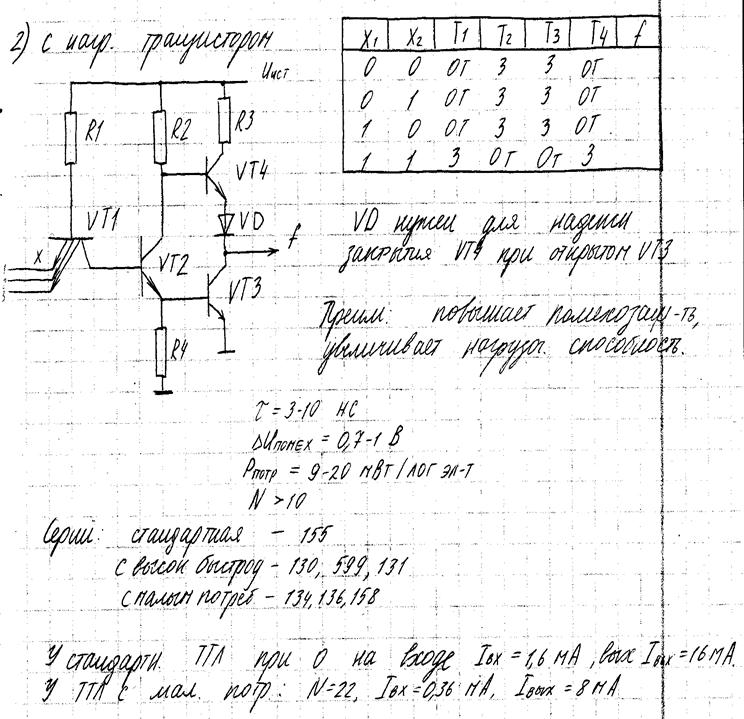

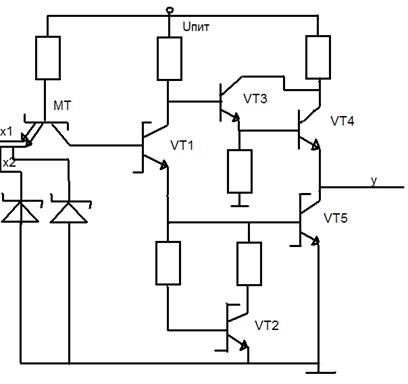

32 ТТЛ с нагрузочным ТРАНЗИСТОРОМ

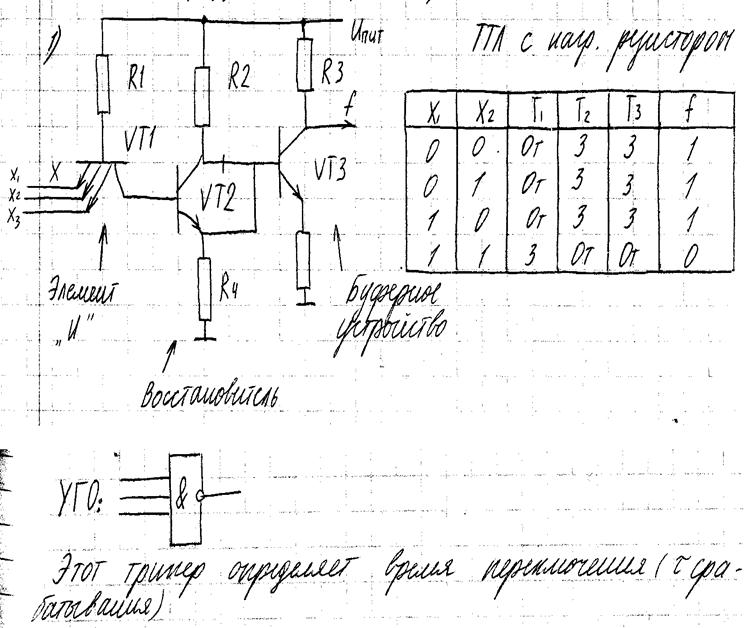

33 ТТЛ с нагрузочным РЕЗИСТОРОМ

34. ТТЛШ (транзистор Шоттки)

Элементы ТТЛ с диодами и транзисторами Шотки широко используются в качестве элементной базы быстродействующих цифровых микросхем. Вместо обычных транзисторов в этих элементах используется транзистор Шотки, параллельно его коллекторному переходу включен диод Шоттки(ДШ)

Для контакта Шотки обычно используются металлы А1 или Pt Si, которые обеспечивают напряжение отпирания диода U*ш≈0,4.. 0,5 В<U*. В случае открытого транзистора ДШ из-за действия ООС по напряжению препятствует снижению напр м/у К и Э ниже 0,3В => транзистор переключается в 3 раза быстрее.

ТТЛШ серии – 530, 531, 555. Маломощный ТТЛШ по быстродействию эквивалентно стандартным ТТЛ.

| x1 | x2 | МТ | Т1 | Т2 | Т3 | Т4 | Т5 | f |

| О | З | З | О | О | З | |||

| О | З | З | О | О | З | |||

| О | З | З | О | О | З | |||

| З | О | О | З | З | О |

Основные параметры и характеристики те же что и в ТТЛ, но быстродействие у ТТЛШ в 3-4 раза лучше.

35. Эмиттерно-связная логика (ЭСЛ)

ЭСЛ является самым быстродействующим логическим элементом и используется для проектирования быстродействующих и сверхбыстродействующих БИС в силу того, что её транзисторы работают в ненасыщенном режиме и логический перепад снижен до Uп <= Up-n.

База в ЭСЛ – дифф-й каскад переключателя тока. Основная черта – ненасыщенная работа транзисторов, засчёт строгого поддержания колл. тока в заданных пределах.

Достоинства: 1. два выхода à более широкие функциональные возможности; 2. Самое большое быстродействие; 3. постоянство тока потребления; 4. Большая нагрузочная способность (15-20).

Параметры: Uпит=-5,2 В – логика отрицания; «1»=-0,9 В; «0»=-1,65 В. Быстродействие обновления 2 нс. Мощность потребления 2,5 мВт.

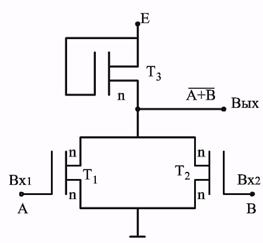

Элемент И-НЕ:

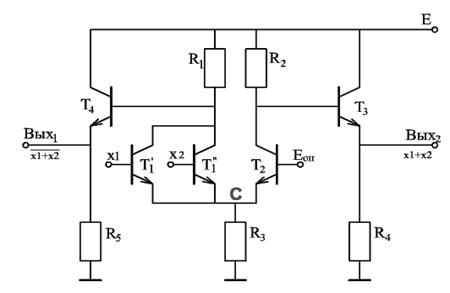

Дифференциальный каскад. Задержка дифференциального ключа уменьшается за счет эмиттерного повторителя. Чтобы R3 выполняло роль источника тока, нужно, чтобы потенциал точки С был постоянным, который можно стабилизировать используя источник опорного напряжения.

Дифференциальный каскад. Задержка дифференциального ключа уменьшается за счет эмиттерного повторителя. Чтобы R3 выполняло роль источника тока, нужно, чтобы потенциал точки С был постоянным, который можно стабилизировать используя источник опорного напряжения.

| Элемент ИЛИ-НЕ:

| Элемент ИЛИ:

|

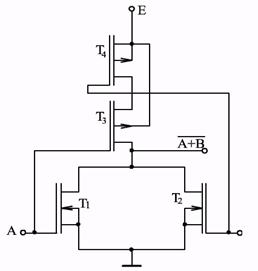

36. Интегрально-инжекционная логика.

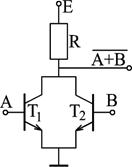

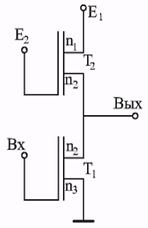

| Структуры интегрально-инжекционной логики (И2Л структуры) широко используются в маломощных запоминающих устройствах, микропроцессорах и ИС с высокой степенью интеграции. Простейшая схема инвертора на биполярном транзисторе приведена на рис. 1. Логическому нулю напряжения на входе транзистора соответствует логическая единица на выходе и наоборот. В И2Л структуре входной резистор заменяется генератором тока (транзистор Т1), поставляющим носители в базу выходного транзистора Т2. Коллекторы выходного транзистора разведены для выполнения логических функций. Принципиальная схема инвертора (вентиля) приведена на рис. 2. |

|

|

Основной логический элемент сформирован путем объединения горизонтального транзистора Т1 p-n-p типа с вертикальным транзистором n-p-n типа, который имеет несколько коллекторов, предназначенных для выполнения независимых логических операций в различных частях схемы. Коллектор транзистора Т1 служит базой транзистора Т2, а скрытый n+ слой Т2 используется как база Т1. Легко видеть, что эти конструктивные особенности совместо с ликвидацией резистора существенно повышают степень интеграции схем. Выходной транзистор работает в инверсном режиме. При Uвх= 0 носители в базу транзистора Т2 не поступают и на его выходе наблюдается высокий уровень сигнала. В случае высокого уровня входного сигнала Uвх ~ 0.8 В ток из транзистора Т1 инжектируется в базу Т2, переводя его в состояние насыщения. В этом случае с выхода логического элемента снимается низкий уровень логического сигнала Uкэ ~ 0.1 В.

Основное достоинство – большое кол-во компонентов и элементов, расположенных на кристалле. Основное назначение – БИС и СБИС. Используется для построения БИС серии К583 и К584. ИИЛ на диодах Шотки (И2ЛШ): в 2 раза больше быстродействие, чем у ИИЛ.

Вывод – по быстродействию И2Л уступает ТТЛ и ЭСЛ.

37. МОП логика.

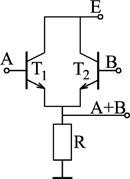

МОП - это полевые транзисторы, работающие благодаря току либо дырок, либо электронов, выполненные по технологии Металл-Окисел-Проводник. Основная принципиальная разница: транзисторы переключаются величиной тока протекающего в нужном направлении. Основные достоинства: 1. между стоком и истоком ток протекает в любых направлениях; 2. в нормально закрытом состоянии очень большое сопротивление. МОП транзисторы управляются током на базах. Подложка и исток соединяются вместе. Логика на p-МОП транзисторах дешевле в изготовлении. Основной недостаток – уступает по быстродействию в 10 раз логике на n-МОП транзисторах. Достоинства: 1. высокое входное сопротивление = 1014Ом. В закрытом состоянии I=0 (на практике около 0). Коэффициент нагрузочной способности N очень большой; 2. высокая технологичность, низкая себестоимость. Стоимость логики на МОП меньше, чем на биполярных транзисторах; 3. Высокая помехоустойчивость – (2-6)В. Недостатки: высокое напряжение питания, низкое быстродействие (меньше, чем у ТТЛ). Операция И образуется путем последовательного соединения транзисторов, а операция ИЛИ – путем параллельного соединения транзисторов. Для транзисторов с элект-й проводимостью. На транзисторах с дырочной проводимостью все наоборот.

Инвертор с квазилинейной нагрузкой

| Инвертор с линейной нагрузкой

| Инвертор с затвором, объединенным по выходу

| Реализация логического элемента ИЛИ-НЕ

Работает на положительной логике. Логическую функцию ИЛИ реализует параллельное соединение МОП-транзисторов Т1 и T2. Для создания элемента И-НЕ используют последовательное их соединение. Недостаток: площадь схемы зависит от кол. входов.

Работает на положительной логике. Логическую функцию ИЛИ реализует параллельное соединение МОП-транзисторов Т1 и T2. Для создания элемента И-НЕ используют последовательное их соединение. Недостаток: площадь схемы зависит от кол. входов.

|

38. КМОП логика.

КМОП – комплементарная МОП, предполагает одновременное использование МОП транзисторов и с p- и с n-проводимостью. Второй закрытый транзистор – резистор с большим R и не влияет на уровень выходных сигналов. В статике мощность потребления = 0, а в динамике = 2U2ипснf (зависимость от f). Работа схемы не зависит от уровня Uип(3-15В). Достоинства: высокая помехоустойчивость, допустимый уровень помех около 40-45% от Uип. Недостатки: низкое быстродействие (около 50 нс). Серия К564, К561, К764, К765. Большие возможности. Коэффициент нагрузочной способности N=15-20.

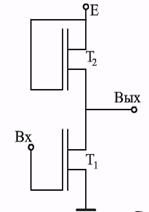

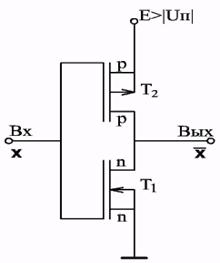

Реализация функции НЕ

В качестве нагрузочного транзистора Т2 используется р - канальный транзистор, а в качестве управляющего Т1, с каналом n -типа. КМОП инвертор работает на полож. логике. Т2 всегда закрыт по току. Мощность КМОП - инвертора меньше нем МОП - инвертора, т.е. от источника напряжения почта не происходит потр. энергии.

В качестве нагрузочного транзистора Т2 используется р - канальный транзистор, а в качестве управляющего Т1, с каналом n -типа. КМОП инвертор работает на полож. логике. Т2 всегда закрыт по току. Мощность КМОП - инвертора меньше нем МОП - инвертора, т.е. от источника напряжения почта не происходит потр. энергии.

| Реализация функции ИЛИ - НЕ

Комплементарные пары: Т1 - Т3, Т2 - Т4. Функцию ИЛИ реализует параллельное соединение n-канапьных транзисторов. Если хотя бы один из транзисторов в последовательной цепочке Тз-Т4 закрыт, то на выходе ноль.

Комплементарные пары: Т1 - Т3, Т2 - Т4. Функцию ИЛИ реализует параллельное соединение n-канапьных транзисторов. Если хотя бы один из транзисторов в последовательной цепочке Тз-Т4 закрыт, то на выходе ноль.

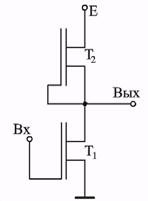

| Реализация функции И - НЕ

Комплементарные пары: Т1 - Т3, Т2 - Т4. Функцию И реализует последовательное соединение n-канальных транзисторов. Если хотя бы один из транзисторов в параллельном соединении Тз-Т4 открыт, то на выходе единица.

Комплементарные пары: Т1 - Т3, Т2 - Т4. Функцию И реализует последовательное соединение n-канальных транзисторов. Если хотя бы один из транзисторов в параллельном соединении Тз-Т4 открыт, то на выходе единица.

|

39. Монтажная логика.

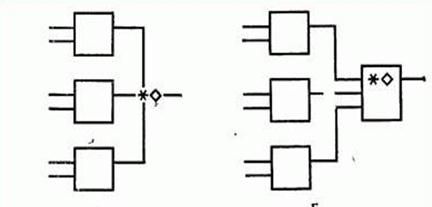

Монтажная логика - логика которая создается посредством монтажа - непосредственное соединение логических выходов нескольких элементов на общую нагрузку.

Обозначение монтажной логики.

Монтажную логику можно рассматривать условно как элемент, который изображают в виде УГО элемента монтажной логики (черт.15б).

1. Термину «элемент монтажной логики» соответствует термин «элемент DOT».

2. В зависимости от вида выполняемой логической функции знак «*» следует заменять знаком «&» («монтажное И») или знаком «1» («монтажное ИЛИ»).

|

|

|

|

Дата добавления: 2014-01-20; Просмотров: 1625; Нарушение авторских прав?; Мы поможем в написании вашей работы!