КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Концепция защиты

|

|

|

|

Режим виртуального процессора 8086

Назначение защищенного режима микропроцессоров IA-32

Общие сведениия

Защищенный режим

Компоненты архитектуры системного уровня

Архитектура системного уровня процессоров IA-32

Задачи архитектуры системного уровня (system-level architecture)

– управление памятью (Memory management);

– защита программных модулей (Protection of software modules);

– поддержка многозадачности (Multitasking);

– обработка прерываний (Exception and interrupt handling);

– поддержка мультипроцессорных систем (Multiprocessing);

– управление кэшированием памяти (Cache management);

– управление аппаратными ресурсами и электропитанием (Hardware resource and power management);

– управление отладкой и производительностью (Debugging and performance monitoring).

– порты ввода-вывода (I/O ports);

– регистры системного управления (Control registers);

– регистры управления памятью (Memory management registers);

– регистры отладки (Debug registers);

– регистры контроля границ диапазонов памяти (Memory type range registers – MTRR’s);

– модельно-зависимые регистры (Machine specific registers – MSR’s);

– регистры контроля состояния процессора (Machine check registers);

– счетчики мониторинга производительности (Performance monitoring counters).

Protected Mode или Protected Virtual Address Mode (защищенный режим виртуальной адресации)

Обеспечивает:

– независимость выполнения нескольких задач, что подразумевает _________ ____________ одной задачи ___ _______________ ________________ _________;

– средства ____________ __________________ _______.

Является основным режимом работы 32-разрядных процессоров.

Адресуемая память – до _ _______ (64 Гбайт в Р6+) физической памяти, посредством которой при использовании механизма страничной адресации могут отображаться до __ _______ виртуальной памяти каждой задачи.

Virtual 8086 Mode или V86:

– является _________ _______________ _________ защищенного режима;

– процессор функционирует как 8086 с возможностью использования 32-разрядных адресов и операндов.

Защищаемые ресурсы:

– _________, в которой хранятся коды, данные и различные системные таблицы;

– совместно используемая _______________, взаимодействие с которой происходит посредством:

– операций ввода-вывода;

– прерываний.

Основа системы защиты: ________________ _ _______________.

Ограничения на:

– ___________________ сегментов (пример: запрет записи в только читаемые сегменты данных или попытки исполнения данных как кода);

– _________ _ сегментам (через правила привилегий);

– межсегментные вызовы и передачу управления;

– выполнение _________________________ _______________ или операций, требующих определенного _________ _______________.

Дескрипторы и таблицы дескрипторов. Системные сегменты

Дескрипторы – восьмибайтные структуры данных, определяющие структуры и свойства программных элементов (сегментов, шлюзов (Gates) и таблиц):

– _____________ ____________ _ _________;

– _________ _______________ _____________ __________ (лимит, предел);

– _______________ ____________;

– _____________________ _________.

Дескрипторы хранятся _ ________________ _________, группируясь в таблицы, обращение к которым поддерживается процессором аппаратно.

Типы таблиц:

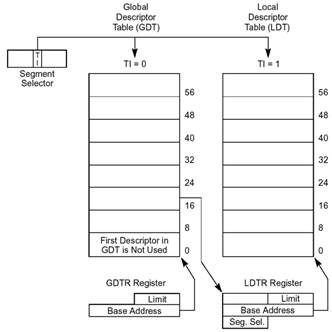

– глобальная таблица дескрипторов (GDT, Global Descriptor Table);

– локальная таблица дескрипторов (LDT, Local Descriptor Table);

– таблица дескрипторов прерываний (IDT, Interrupt Descriptor Table).

GDT содержит дескрипторы, доступные ______ __________:

– тип дескрипторов – любой, кроме дескрипторов _________ _______________ _ __________;

– нулевой элемент таблицы не используется.

LDT может быть ________________ ____ _________ _________ и содержит дескрипторы:

– сегментов;

– шлюзов задач;

– шлюзов вызовов.

Сегмент недоступен задаче, если его дескриптора нет в текущий момент ни в GDT, ни в LDT.

IDT содержит дескрипторы шлюзов:

– задач;

– _______________;

– __________.

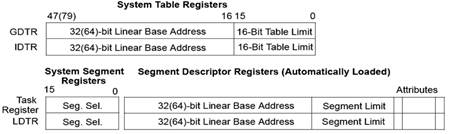

Регистры дескрипторов таблиц и системных сегментов

Механизм использования глобальной и локальной таблиц дескрипторов

Размеры таблиц:

– GDT, LDT – (8-64К) байт / (1-8К) элементов;

– IDT – (256-2К) байт.

С каждой из таблиц ассоциирован соответствующий регистр процессора. Для занесения в регистры GDTR и IDTR базового адреса и лимита своей таблицы используются привилегированные команды LGDT и LIDT, соответственно.

Системные сегменты предназначены для хранения:

– _____________ _________ __________________;

– _____________ _______ (TSS – Task State Segment).

|

|

|

|

|

Дата добавления: 2014-01-11; Просмотров: 274; Нарушение авторских прав?; Мы поможем в написании вашей работы!