КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Архитектура нейрочипа

|

|

|

|

Выбор и обоснование принципов построения нейрочипа

Лекции 14. Аппаратная реализация на примере нейрочипа NeuroMatrix NM6403.

Особенности аппаратной реализации нейросетей

При использовании нейросетевых алгоритмов плохо формализуемых задач моделирования, прогнозирования и распознавания достаточно малоразрядных представлений входов и весов и операций с фиксированной точкой. Это обусловлено тем, что значения входов нормируются (приводятся к интервалу 0, 1 или -1,1), и число различных значений каждого входа, как правило, не велико.

При решении хорошо формализуемых задач, сформулированных в нейросетевом базисе, существенна точность вычислений, что требует полноразрядных представлений чисел и операций с плавающей точкой.

Таким образом, специализация вычислительных средств на выполнение нейроалгоритмов заключается с одной стороны в повышении обмена между памятью и операционными устройствами, а с другой стороны – в уменьшении времени выполнения умножения и накопления за счет укорочения операндов.

Пример аппаратной реализации (нейрочип NeuroMAtrix NM6403 НТЦ «Модуль»)

Основными предпосылками, которыми руководствовались разработчики при создании архитектуры нейрочипа, были следующие:

· нейрочип должен быть программируемым устройством, имеющим в своем составе операционные узлы специально, разработанные для эффективной поддержки нейровычислений;

· нейрочип должен обеспечивать вычисление значений выходов нейронов как можно большего участка нейросети за один процессорный такт;

· нейрочип должен производить вычисления над данными (синапсами и весами) произвольной разрядности (от 1 до 64 бит);

· нейрочип должен иметь в своем составе средства комплексирования для создания распределенных параллельных вычислительных систем, состоящих из любого количества процессорных узлов;

· нейрочип должен иметь достаточно развитую систему команд, способную поддерживать наиболее часто используемые конструкции современных языков высокого уровня. Любая команда (кроме команд загрузки/выгрузки массивов данных) должна выполняться за один процессорный такт.

Далее описаны архитектурные решения, принятые разработчиками, удовлетворяющие приведенным выше требованиям.

Нейрочип предназначен для реализации нейросетей, имеющих следующие функциональные характеристики:

a) Каждый слой нейросети (рис.1) выполняет следующую функцию:

где:

Zi - выходной сигнал i-го нейрона (i-й нейрон),

Xj - j-й входной сигнал слоя (j-й синапс),

Ui - смещение i-го нейрона,

Wij - весовой коэффициент j-го входа i-го нейрона,

Yi - сумма взвешенных входов i-го нейрона,

f - функция активации,

N - количество входных сигналов слоя,

M- количество нейронов в слое.

б) Операнды Zi, Xj, Ui и Wij представляются в прямом и дополнительном кодах и могут иметь произвольную разрядность.

в) Количество слоев в нейросети, а также количество нейронов и сигналов в каждом слое могут быть произвольными.

г) Между входами и выходами отдельных слоев нейросети допускаются любые межсоединения. То есть выходной сигнал k-го слоя может поступать на один из входов i-го слоя, где k=1,...,K, i=1,...,K, а K - число слоев нейросети.

В основу архитектуры нейрочипа положен оригинальный метод выполнения его базовых операций с помощью операционного узла (OU), представляющего собой однородную вычислительную среду, которая позволяет производить операции над синапсами и весами произвольной разрядности (от 1 до 64 бит). Следует отметить, что принцип переменной разрядности операндов применен в нейропроцессоре фирмы Philips L-neuro 1.0, однако этот нейропроцессор использует представление данных в последовательном коде, что значительно снижает производительность, кроме того, разрядность обрабатываемых данных может выбираться только из фиксированного набора 1, 2, 4, 8, 16. Функция активации L-neuro 1.0 реализована вне чипа, что тоже отрицательно сказывается на производительности. Производительность в процессе вычислений L-neuro 1.0 чипа - 100 MCPS для 1 битного варианта и 26 MCPS для 8 битного варианта.

Взвешивание и сложение синапсов является наиболее сложной операцией и требует больших аппаратных и временных ресурсов. Поэтому данная операция является основной операцией, на которую ориентирован ОU нейрочипа. Его структурная организация позволяет выполнить взвешивание и сложение синапсов методом параллельного умножения синапсов на весовые коэффициенты.

В данном случае OU за один такт осуществляет взвешивание нескольких синапсов и вычисление их сумм одновременно для нескольких нейронов. То есть за один такт OU реализует функции фрагмента нейросети, включающего в себя несколько синапсов и несколько нейронов.

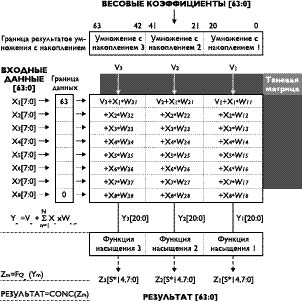

Работа OU в данном режиме иллюстрируется ниже на примере реализации функций фрагмента нейросети, включающего 2 нейрона и 3 синапса (рис.34), на OU с m=19 (суммарная разрядность выходов) и n=12 (суммарная разрядность входов). В данном примере операнды имеют следующие разрядности: X1-3, X2-4, X3-5, U1-10, U2-9, Y1-10, Y2-9, W1-5, W12-4, W13-3, W21-4, W22-3, W23-2.

Рис.34. Фрагменты слоя нейросети.

Предварительно в OU загружаются соответствующие битовые элементы матрицы весов, содержимое которой определяется на этапе обучения нейросети. В данном режиме работы элементами матрицы являются разряды весовых коэффициентов и нулевые элементы, расположенные в строго фиксированных позициях.

Такая настройка как бы разбивает OU на РхR подматриц (рис.35), где Р - количество нейронов, а R - количество синапсов в реализуемом фрагменте нейросети. Для рассматриваемого примера Р=2, R=З. Будем считать, что подматрица с координатами (p,r) соответствует р-му нейрону (р=1,...,Р) и r-му синапсу (г=1,...,R). Тогда каждая подматрица с координатами (р,1) вычисляет функцию X1Wpl+Up, а каждая подматрица с координатами (р,t) формирует произведение XtWpt и прибавляет к нему результат, полученный на выходе подматрицы с координатами (р,t-1), где t=2,...,R.

Таким образом, на выходе подматрицы (р,R) формируется результат операции.

Рис.35. Разбиение матрицы на подматрицы.

Необходимым условием работоспособности OU в данном режиме является то, что количество бит, отводимых для каждого р-го нейрона, должно быть не больше максимально возможной разрядности Yp. Только при этом условии исключается возможность прохождения сигналов переноса, возникающих в цепях сложения, через границы между соседними нейронами. С одной стороны, данное условие обеспечивает конкатенацию нескольких нейронов в единой вычислительной среде, какую представляет собой OU, а с другой, оно исключает возможность арифметических переполнений и, следовательно, необходимость дополнительного контроля. Выполнение этого условия должно обеспечиваться на этапе обучения нейросети путем введения в матрицу весов нулевых столбцов в области старших разрядов каждого нейрона.

Таким образом, количество нейронов, одновременно обслуживаемых OU, зависит от числа синапсов, их разрядности и значений весовых коэффициентов. Суммарная разрядность Yp не должна превышать значения m. Количество синапсов, одновременно обрабатываемых OU, разрядностью синапсов. Суммарная разрядность Х не должна превышать значения n. Настройка нейрочипа на работу с конкретными величинами разрядности синапсов и весов производится путем загрузки в специальные регистры управляющей информации как перед началом работы, так и в процессе вычислений. Это позволяет динамически изменять разрядность обрабатываемых данных, а следовательно скорость и точность вычислений от слоя к слою, от нейрона к нейрону, от синапса к синапсу.

В случае работы нейрочипа с одинаковой разрядностью синапсов и весов которая составляет 8 бит, за один процессорный такт OU производит 24 операции умножения с накоплением, что при частоте тактовых импульсов 30 MHz составит 720 MCPS (миллионов соединений в секунду). Другими словами, за один процессорный такт производится вычисление участка нейросети, состоящего из 3 нейронов по 8 синапсов каждый, разрядности нейронов и синапсов составляют при этом один байт.

Рис. 36. NeuroMatrix Engine.

Ядром архитектуры является регулярная структура, похожая на матричный умножитель (NeuroMatrix Engine). Матрица состоит из 64x64 ячеек, каждая ячейка содержит элемент памяти (flip-flop) и несколько логических элементов. Матрица может быть разделена на несколько подматриц двумя 64-разрядными программируемыми регистрами: MB и DB. Эти регистры определяют границы MAC и входных данных соответственно. Например, для 8-разрядных данных (Xi) и 8-разрядных коэффициентов (Wi) количество подматриц (макроячеек) составляет 24. Каждая макроячейка производит операцию умножения элементов входных данных Xi на предварительно загруженные коэффициенты Wi и накапливает результат из макроячеек, расположенных выше, и входа Vi. Таким образом, каждый столбец вычисляет 21-разрядный результат MAC-операции над восемью данными и восемью коэффициентами. В нашем случае, имеется три таких столбца, которые производят 24 MAC-операции за один процессорный такт. При значении тактовой частоты 50 МГц, производительность составляет 1,2 GMAC.

На загрузку весовых коэффициентов в матрицу, требуется 32 такта. Для снижения накладных расходов, связанных с перезагрузкой матрицы весов, применяется «теневая» матрица SM. Новые коэффициенты загружаются в «теневую» матрицу на фоне вычислений и могут быть переданы в рабочую матрицу за один процессорный такт.

Рис. 37. Функция насыщения.

Функции насыщения (Saturation Functions) (рис. 37) используются для снижения разрядности результатов и защиты от арифметического переполнения.

В примере, приведенном на рис. 36, функция насыщения снижает число значащих разрядов с 21 до 8. Ширина входов функции насыщения эквивалентна ширине колонки (выхода MAC), ширина выхода функции должна быть эквивалентна входу MAC. На первом проходе функции насыщения снижают количество значащих разрядов, на втором проходе, рабочая матрица упаковывает 8-разрядные выходы в 64- разрядные слова данных. Все параметры функций насыщения программируются.

Конфигурация матрицы может быть изменена динамически в течение вычислений. Вычисления могут быть начаты с максимальной точностью и минимальной производительностью, но при определенных условиях можно достичь пиковой производительность путем снижения точности.

|

|

|

|

|

Дата добавления: 2014-01-11; Просмотров: 808; Нарушение авторских прав?; Мы поможем в написании вашей работы!