КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Параллельные диодные ограничители

|

|

|

|

Основным недостатком последовательных диодных ограничителей является требование низкого внутреннего сопротивления Э.Д.С. источника сигнала. Для ликвидации этого недостатка разработаны параллельные диодные ограничители. Такие схемы ограничителей не требуют очень низкого выходного сопротивления источника Э.Д.С.

;

;  ;

;

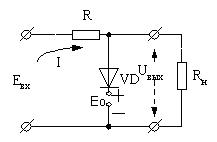

Схема диодного ограничителя сверху, приведена на рис. 10.

Рис. 10 - Параллельный диодный ограничитель сверху

В схеме (рис. 10) в исходном состоянии диод VD закрыт. Когда на вход подается сигнал положительной полярности, он передается на выход ограничителя до тех пор, пока не достигнет значения Е0, после чего диод открывается и передача сигнала на выход ограничителя прекращается вследствие шунтирующего действия открытого диода. Т.е. рассматриваемый ограничитель пропускает только те сигналы, которые меньше напряжения Е0.

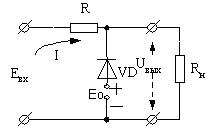

Рис. 11 - Параллельный диодный ограничитель снизу на нулевом уровне

В схеме (рис. 11) в исходном состоянии диод открыт. Когда на вход подается сигнал положительной полярности, он вследствие падения напряжения на резисторе R не поступает на выход до тех пор, пока не достигнет значения Е0, после чего диод закрывается и сигнал поступает на выход ограничителя. Т.о. пропускаются сигналы большие, чем Е0.

ВЫВОДЫ:

Параллельные диодные ограничители не критичны к  источника входного сигнала, однако обладают теми же остальными недостатками последовательных диодных ограничителей – имеют низкий коэффициент передачи, требуют большие входные сигналы

источника входного сигнала, однако обладают теми же остальными недостатками последовательных диодных ограничителей – имеют низкий коэффициент передачи, требуют большие входные сигналы  и буферный каскад для согласования с

и буферный каскад для согласования с  .

.

Для ликвидации общих недостатков диодных ограничителей разработаны транзисторные усилители-ограничители, у которых существенно более низкие входные сигналы (сотни милливольт), относительно высокое входное, и низкое выходное сопротивления и лучшая форма (коэффициент прямоугольности) выходного напряжения.

|

|

|

|

|

Дата добавления: 2014-01-13; Просмотров: 2259; Нарушение авторских прав?; Мы поможем в написании вашей работы!