КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Тайминги

|

|

|

|

Тайминги - это задержки при обращении к микросхемам памяти. Естественно, чем они меньше - тем быстрее работает модуль.

Дело в том, что микросхемы памяти на модуле имеют матричную структуру - представлены в виде ячеек матрицы с номером строки и номером столбца.

При обращении к ячейке памяти считывается вся строка, в которой находится нужная ячейка.

Сначала происходит выбор нужной строки, затем нужного столбца. На пересечении строки и номера столбца и находится нужная ячейка. С учетом огромных объемом современной RAM такие матрицы памяти не целиковые - для более быстрого доступа к ячейкам памяти они разбиты на страницы и банки.

Сначала происходит обращение к банку памяти, активизация страницы в нем, затем уже происходит работа в пределах текущей страницы: выбор строки и столбца.

Все эти действия происходит с определенно задержкой друг относительно друг друга.

Основные тайминги RAM - это задержка между подачей номера строки и номера столбца, называемая временем полного доступа (RAS to CAS delay, RCD), задержка между подачей номера столбца и получением содержимого ячейки, называемая временем рабочего цикла (CAS latency, CL), задержка между чтением последней ячейки и подачей номера новой строки (RAS precharge, RP). Тайминги измеряются в наносекундах (нс).

Эти тайминги так и идут друг за другом в порядке выполнения операций и также обозначаются схематично 5-5-5-15. В данном случае все три тайминга по 5 нс, а общий рабочий цикл - 15 нс с момента активизации строки.

Главным таймингом считается CAS latency, который часто обозначается сокращенно CL=5. Именно он в наибольшей степени "тормозит" память.

Основываясь на этой информации, вы сможете грамотно выбрать подходящий модуль памяти.

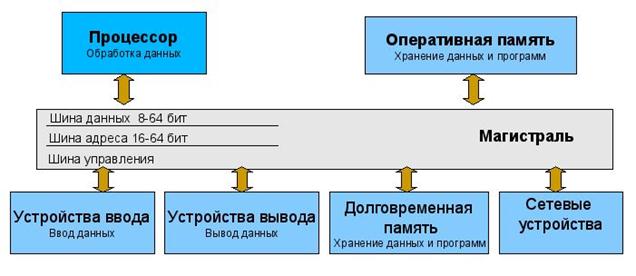

7. МАГИСТРАЛЬНО-МОДУЛЬНЫЙ ПРИНЦИП ПОСТРОЕНИЯ ЭВМ

Архитектура современных ПК основана на магистрально-модульном принципе.

Модульный принцип позволяет потребителю самому подобрать нужную ему конфигурацию компьютера и производить при необходимости его модернизацию. Модульная организация системы опирается на магистральный (шинный) принцип обмена информации. Магистраль или системная шина - это набор электронных линий, связывающих воедино по адресации памяти, передачи данных и служебных сигналов процессор, память и периферийные устройства.

Обмен информацией между отдельными устройствами ЭВМ производится по трем многоразрядным шинам, соединяющим все модули, - шине данных, шине адресов и шине управления.

Разрядность шины данных задается разрядностью процессора, т.е. количеством двоичных разрядов, которые процессор обрабатывает за один такт.

Данные по шине данных могут передаваться как от процессора к какому-либо устройству, так и в обратную сторону, т. е. шина данных является двунаправленной. К основным режимам работы процессора с использованием шины передачи данных можно отнести следующие: запись/чтение данных из оперативной памяти и из внешних запоминающих устройств, чтение данных с устройств ввода, пересылка данных на устройства вывода.

Выбор абонента по обмену данными производит процессор, который формирует код адреса данного устройства, а для ОЗУ - код адреса ячейки памяти. Код адреса передается по адресной шине, причем сигналы передаются в одном направлении, от процессора к устройствам, т. е. эта шина является однонаправленной.

По шине управления передаются сигналы, определяющие характер обмена информацией, и сигналы, синхронизирующие взаимодействие устройств, участвующих в обмене информацией.

|

|

|

|

|

Дата добавления: 2014-01-13; Просмотров: 495; Нарушение авторских прав?; Мы поможем в написании вашей работы!