КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Триггеры

|

|

|

|

В импульсной и цифровой технике широко используются функциональные узлы, способные сохранять двоичную информацию (состояния «0», «1») после окончания действия входных импульсов. Такие функциональные узлы называют триггерами. В интегральной схемотехнике триггеры выполняют либо на основе логических элементов, либо как завершенный функциональный элемент в виде микросхемы. Интегральные триггеры характеризуются большим разнообразием. Их отличают функциональный признак, определяющий поведение триггера при воздействии сигнала управления, а также используемый способ управления.

По функциональному признаку различают триггеры типов RS, D, T, JK и др. По способу управления триггеры подразделяют на асинхронные и тактируемые (синхронные). В асинхронных триггерах переключение из одного состояния в другое осуществляется непосредственно с поступлением сигнала на информационный вход. В тактируемых триггерах помимо информационных входов имеется вход тактовых импульсов. Их переключение производится только при наличии разрешающего, тактирующего импульса.

2.3.1.1 RS-триггеры

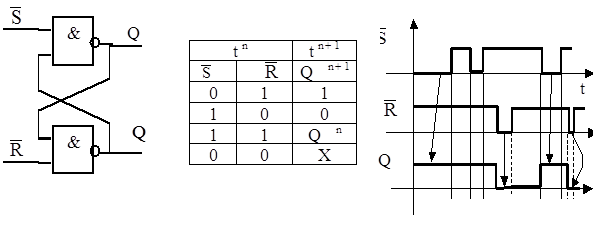

Асинхронные триггеры требуют для своего построения два двухвходовых логических элемента типа И-НЕ или ИЛИ-НЕ. На рисунке 2.10 приведена структурная схема асинхронного триггера на логических элементах 2И-НЕ.

Рисунок 2.10 – Асинхронный RS-триггер на логических элементах 2И-НЕ

Состоянию логической «1» соответствует Q = 1,  = 0. Состоянию логического «0» соответствует Q = 0,

= 0. Состоянию логического «0» соответствует Q = 0,  = 1. По управляющему входу

= 1. По управляющему входу  производится установка триггера в состояние логической «1», а по управляющему входу

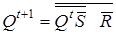

производится установка триггера в состояние логической «1», а по управляющему входу  – установка (перевод) триггера в исходное состояние логического «0». Структурные уравнения триггера имеют вид:

– установка (перевод) триггера в исходное состояние логического «0». Структурные уравнения триггера имеют вид:

;

;  . (2.4, 2.5)

. (2.4, 2.5)

Принцип действия триггера определяется поведением в нем элементов И-НЕ. Он иллюстрируется таблицей переходов триггера, где указаны значения входных сигналов в некоторый момент времени tn и состояние триггера (по значению его прямого выхода) в следующий момент времени tn+1 после прихода очередных импульсов. Рассмотренной схеме триггера соответствуют временные диаграммы, приведенные на рисунке 2.10. Они построены с учетом таблицы переходов.

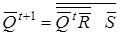

На рисунке 2.11 приведена структурная схема тактируемого RS-триггера на элементах 2И-НЕ.

Переключения в тактируемом триггере возможны лишь при наличии тактирующего импульса, подаваемого на вход Т. Эта особенность схемы связана с применением на входах двух управляющих элементов 2И-НЕ.

Рисунок 2.11 – Тактируемый RS-триггер

2.3.1.2 D-триггеры

D-триггеры имеют один информационный вход. Состоянию логической «1» на прямом выходе соответствует единица на информационном входе триггера, а состоянию логического «0» – нулевой уровень входного сигнала. Характеристические уравнения D-триггера имеют вид:

. (2.6)

. (2.6)

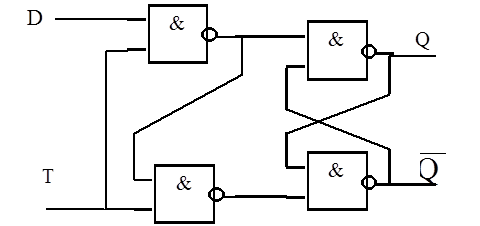

На практике наибольшее применение получили тактируемые (однотактные и двухтактные) D-триггеры. Их обозначение обусловлено свойством сохранять состояние на выходе после снятия сигнала с информационного входа до прихода очередного тактового импульса (dе1ау – задержка). D-триггеры широко используют при построения регистров. На рисунке 2.12 приведена схема однотактного D-триггера, выполненная на основе асинхронного RS-триггера.

Рисунок 2.12 – Однотактный тактируемый D-триггер

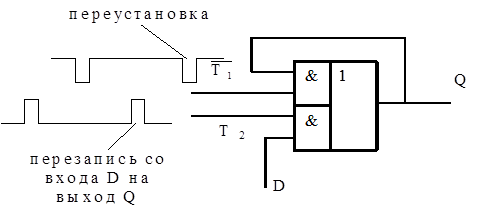

Принцип действия двухтактных D-триггеров подобен однотактным. Отличие заключается в том, что запись информации в них производится с участием одной последовательности тактовых импульсов, а обнуление (переустановка) с участием другой последовательности тактовых импульсов. Вторая последовательность тактовых импульсов имеет фазовый сдвиг в 180° и инверсна первой (пример на рисунке 2.13). На рисунке 2.13 приведена схема однофазного (имеющего один выход) двухтактного D-триггера на элементе 2И-ИЛИ.

Рисунок 2.13 – Однофазный двухтактный D-триггер

2.3.1.3 Т-триггер

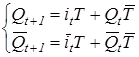

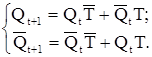

Характерным свойством Т-триггера является его переключение в противоположное состояние с приходом каждого очередного входного импульса. Ввиду широкого применения в счетчиках импульсов его часто называют триггером со счетным запуском. Триггеры Т-типа выполняются на базе двух асинхронных RS-триггеров (Мaster-Slave-схема), один из которых называют основным, а другой – вспомогательным (ведущий-ведомый) – триггеры левый и правый на рисунке 2.14. Состояния его выходов описываются системой уравнений:

(2.7)

(2.7)

По M/S-схеме реализуются несколько вариантов Т-триггера. Особенностью рассматриваемой структурной схемы является наличие в ней дополнительного инвертора (элемент D3), управляющего вспомогательным триггером. В связи с этим ее называют часто схемой с инвертором.

Рисунок 2.14 – Т-триггер

Последовательность переключения асинхронных RS-триггеров, входящих в Т-триггер, такая. На этапе фронта входного импульса переключается основной триггер, а по окончании длительности tИ входного импульса (на этапе среза) – вспомогательный триггер. Указанная особенность отражается в другом названии схемы – триггер с внутренней задержкой (Тt).

Режим счетного запуска Т-триггера определяет указанные ниже особенности, учитываемые при его построении. В схеме должны быть созданы условия для сохранения нового состояния после переключения триггера входным импульсом. При этом должна обеспечиваться необходимая направленность переключения: если триггер находится в состоянии «1», то входной импульс переводит его в состояние «0», и наоборот.

Избирательность переключения Т-триггера достигается наличием связей элементов D8, D9 с выходами вспомогательного триггера. Если до прихода очередного входного импульса Т в триггере записана «1», то по цепям обратных связей на входе элемента D9, будет логическая «1», а на выходе элемента D8 – логический «0». При поступлении входного импульса Т элемент D9 переходит в состояние «0», вызывая переключение в нулевое состояние основного триггера, а после окончания входного импульса в состояние «0» переключается и вспомогательный триггер.

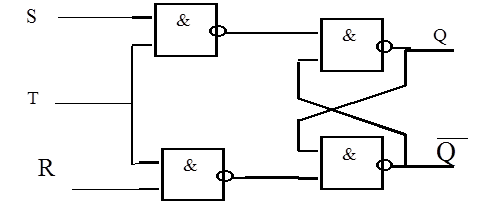

2.3.1.4 JK-триггер

JK-триггер получают на основе Т-триггера путем использования в его входных цепях трехвходовых элементов И-НЕ, позволяющих иметь два дополнительных входа J и К (рисунок 2.14). Наличие двух дополнительных входов расширяет функциональные возможности триггера, в связи с чем JK-триггер называют универсальным. При соответствующем подключении входов JК-триггер, в частности, может выполнять функции RS, D и T-триггеров (рисунок 2.15).

Рисунок 2.15 – Схемы триггеров на основе JK-триггера

JК-триггер, так же как и все типы триггеров, получаемые на его основе, является триггером с внутренней задержкой: в момент действия импульса Т информация записывается в основной триггер, а после его окончания состояние основного триггера передается во вспомогательный. Наличие в работе схемы внутренней временной задержки, определяемой длительностью тактовых импульсов, часто отражается символом «t» в обозначении JK-триггера и триггеров, выполненных на его основе: JKt, RSt, Dt, Тt.

RSt, и Dt-триггеры являются тактируемыми (рисунок 2.16): RSt-триггер получают подачей на вход J сигнала S, а на вход К – сигнала R. Dt-триггер создается введением инвертора в цепь входа К. Триггер со счетным запуском (Тt-триггер) реализуется подключением входов J и К к входу Т.

|

|

|

|

Дата добавления: 2014-01-13; Просмотров: 1587; Нарушение авторских прав?; Мы поможем в написании вашей работы!