КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Мультиплексоры и селекторы

|

|

|

|

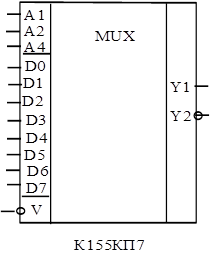

Мультиплексоры. Это функциональный узел ЭВМ, осуществляющий микрооперацию передачи сигнала с одного из своих входов на один выход. На рисунке 2.25 показаны схема и функциональное обозначение стробируемого мультиплексора К155КП7.

Рисунок 2.25 – Мультиплексор К155КП7

Структура этого узла описывается следующими уравнениями:

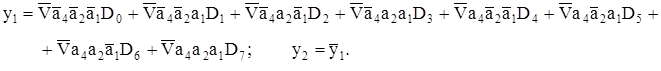

Вход V используется для стробирования и наращивания числа входов мультиплексора. Входы a4, a2 и а1 – адресные. Двоичный код на этих входах определяет, какой сигнал Di, будет передан на выход. Например, при a4 = 1, a2 = 0, а1 = 1, V = 0 сигнал D5 передается на выход, так как все остальные члены в формуле при этом наборе будут равны нулю, т. е. y1 =D5, a y2 =  . Способ наращивания мультиплексоров (до 16 входов) показан на рисунке 2.26.

. Способ наращивания мультиплексоров (до 16 входов) показан на рисунке 2.26.

Рисунок 2.26 – Наращивание мультиплексоров

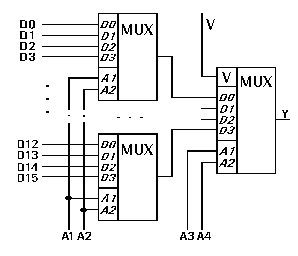

Селекторы. Селектор (демультиплексор) – функциональный узел, осуществляющий операцию передачи сигнала с одного входа на один из нескольких выходов. Селекторы в виде самостоятельных узлов изготовляются редко, так как их функции может выполнять дешифратор. Очевидно, что входной сигнал активизирует тот выход дешифратора, который соответствует конкретному набору переменных, являющихся в данном случае адресом селектора. Использование дешифратора для мультиплексирования показано на рисунке 2.27.

Рисунок 2.27 – Селектор-мультиплексор 564КП2

Широкие возможности предоставляет мультиплексор-селектор, выполненный на КМДП-структурах. На рисунке 2.27 показаны схема и функциональное обозначение микросхемы 564КП2. Один из восьми выходов дешифратора, задаваемый адресом а4а2а1 при V = 0, открывает соответствующий двунаправленный ключ Кл, обеспечивая связь цепей у и Di. При V = 1 все ключи закрыты. Данная схема может использоваться в качестве дешифратора с активным уровнем выходов «1» или «0» и мультиплексора. При использовании схемы в качестве дешифратора с уровнем выходов «1» необходимо присоединить цепь у к источнику питания, а цепи Di через резисторы не менее 20 кОм – к земле.

|

|

|

При использовании схемы в качестве дешифратора с активным уровнем выходов «0» необходимо присоединить цепь у к земле, а цепи Di через резисторы не менее 20 кОм – к источнику питания. Входами дешифратора будут входы а4, а2, а1, а выходами – Di. При использовании схемы в качестве мультиплексора адресными входами являются входы а4, а2, а1; информационными входами – Di, а выходом – у.

При использовании схемы в качестве селектора адресными входами являются входы а4, а2, а1, информационным входом – у, а выходами Di. Из приведенных примеров следует, что мультиплексоры и селекторы являются многофункциональными узлами.

2.7 Счётчики импульсов

Подсчет числа импульсов является наиболее распространенной операцией в устройствах цифровой обработки информации. В устройствах цифровой обработки информации измеряемый параметр (угол поворота, перемещение, скорость, частота, время, температура и т. д.) преобразуется в импульсы напряжения, число которых в соответствующем масштабе характеризует значение данного параметра. Эти импульсы подсчитываются счетчиками импульсов и выражаются в виде цифр.

По целевому назначению счетчики подразделяют на простые и реверсивные. Простые счетчики, в свою очередь, подразделяют на суммирующие и вычитающие. Суммирующий счетчик предназначен для выполнения счета в прямом направлении, т. е. для сложения. С приходом очередного счетного импульса на вход счетчика его показание увеличивается на единицу. Вычитающий счетчик служит для осуществления счета в обратном направлении, т. е. для вычитания. Каждый счетный импульс, поступающий на вход вычитающего счетчика, уменьшает его показание на единицу.

|

|

|

Реверсивные счетчики предназначены для выполнения операции счета как в прямом, так и в обратном направлении, т. е. они могут работать в режиме сложения и вычитания. Ос новными параметрами счетчиков являются модуль счета (коэффициент счета К) и быстродействие. Коэффициент счета определяет число импульсов, которое может быть сосчитано счетчиком.

Быстродействие счетчика характеризуется максимальной частотой fсч следования счетных импульсов и связанным с ней временем tуст установки счетчика. Величина tуст определяет максимальное время протекания переходных процессов во всех разрядах счетчика с поступлением на вход очередного счетного импульса. Счетчики импульсов выполняются на основе триггеров. Счет числа поступающих импульсов производится с использованием двоичной системы счисления.

Двоичные суммирующие счетчики с непосредственной связью: они производят счет поступающих импульсов в двоичной системе счисления. Основным узлом двоичного счетчика (служащим также его разрядом) является триггер со счетным запуском, осуществляющий подсчет импульсов по модулю 2.

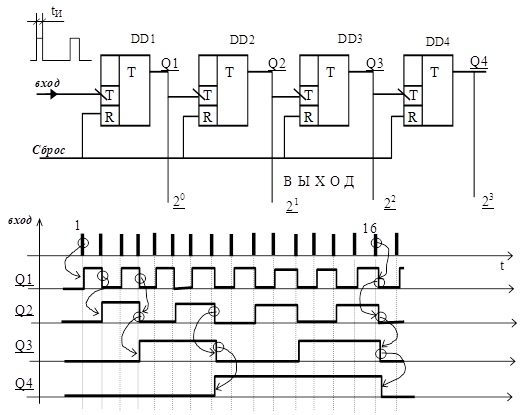

Многоразрядные двоичные суммирующие счетчики с непосредственной связью выполняются путем последовательного соединения счетных триггеров. Принцип действия двоичного счетчика с непосредственной связью рассмотрим на примере четырехразрядного счетчика, показанного на рисунке 2.28. Схема выполнена на счетных Тt-триггерах с внутренней задержкой. Работу схемы иллюстрируют временные диаграммы, приведенные на рисунке 2.28, и таблица 2.4.

Рисунок 2.28 – Двоичный четырёхразрядный счётчик

По окончании 15-го импульса все разряды счетчика устанавливаются в состояние «1», а 16-й импульс переключает первый разряд счетчика в «0». В соответствии с рисунком 2.28 и таблицей 2.4, установка в исходное состояние «0» двух последовательно включенных триггеров (DD1 и DD2) осуществляется четвертым счетным импульсом, трех триггеров (DD1-DD3) – восьмым и четырех триггеров – 16-м счетным импульсом. Из этого следует, что модуль счета двухразрядного, трехразрядного и четырехразрядного двоичных счетчиков равен соответственно 4, 8 и 16. Модуль счета двоичного счетчика находят из соотношения Ксч = 2N, где N – число разрядов счетчика.

|

|

|

В процессе работы двоичного счетчика частота следования импульсов на выходе каждого последующего триггера уменьшается вдвое по сравнению с частотой его входных импульсов. Это свойство схемы используют для построения делителей частоты. При использовании схемы в качестве делителя частоты входной сигнал подают на счетный вход первого триггера, а выходной снимают с последнего триггера.

Выходная и входная частоты связаны соотношением fвых = fвх/Ксч. Максимальное время установки tуст max в двоичных счетчиках с непосредственной связью характеризуется суммарной задержкой в последовательной передаче информации от младшего к старшему разряду счетчика. Другими словами, параметр определяется временем перехода счетчика из кода 2N – 1 в код 00...0. Его находят из соотношения tуст max = Ntзт, где tзт – задержка переключения Тt -триггера после окончания счетного импульса.

Таблица 2.4 – Состояние триггеров счётчика

| Число импульсов | Триггер 1 | Триггер 2 | Триггер 3 | Триггер 4 |

| 0 | 0 | 0 | 0 | |

| 0 | 0 | 0 | 1 | |

| 0 | 0 | 1 | 0 | |

| 0 | 0 | 1 | 1 | |

| 0 | 1 | 0 | 0 | |

| 0 | 1 | 0 | 1 | |

| 0 | 1 | 1 | 0 | |

| 0 | 1 | 1 | 1 | |

| 1 | 0 | 0 | 0 | |

| 1 | 0 | 0 | 1 | |

| 1 | 0 | 1 | 0 | |

| 1 | 0 | 1 | 1 | |

| 1 | 1 | 0 | 0 | |

| 1 | 1 | 0 | 1 | |

| 1 | 1 | 1 | 0 | |

| 1 | 1 | 1 | 1 | |

| 0 | 0 | 0 | 0 |

Время установки возрастает с увеличением числа разрядов, что сказывается на быстродействии счетчика. Максимальная частота следования счетных импульсов ограничивается величиной:

fвх max = 1/(tи + tуст max). (2.13)

При работе счетчика в режиме деления частоты его предельная частота определяется предельной частотой переключения триггера первого разряда:

fвх max = 1/(tи + tзт). (2.14)

Счетчики с коэффициентом счета Ксч ¹ 2N.

На практике часто возникает необходимость в счетчиках, коэффициент счета которых не соответствует указанному значению 2N. Такие счетчики выполняются на основе двоичных счетчиков. Общий принцип их построения основывается на исключении у счетчика с Ксч = 2N соответствующего числа « избыточных» состояний. Число избыточных состояний s определяется разностью: s = 2N – Ксч, где 2N – количество состояний двоичного счетчика; Ксч – требуемый коэффициент счета. Число триггеров счётчика выбирают по минимуму величины s. Например, при построении счетчика с Ксч = 3на двух триггерах и счетчика с Ксч = 10 на четырех триггерах следует исключить соответственно 1 и 6 состояний.

|

|

|

Способы построения счетчиков с коэффициентом счета Ксч ¹ 2N достаточно разнообразны. Наибольшее распространение получили способ принудительной установки в состояние «0» всех разрядов двоичного счетчика и способ принудительного насчета. По первому способу реализуются счетчики с естественным порядком счета, по второму – счетчики с принудительным счетом.

В счетчиках с естественным порядком счета порядок счета такой же, как в двоичных счетчиках. Отличие заключается в том, что путем введения дополнительных связей счет заканчивается раньше значения 2N. У счетчика с Ксч = 10 переход разрядов в состояние «0» будет происходить с приходом не 16-го, а 10-го счетного импульса («Система 16 – 6»).

В счетчиках с принудительным насчетом исключение избыточных состояний двоичного счетчика достигается путем принудительной установки отдельных его разрядов в состояние «1» в процессе счета. Принудительный насчет осуществляется введением обратных связей со старших разрядов двоичного счетчика в младшие, благодаря чему соответствующие младшие разряды вне очереди переключаются в состояние «1».

Вследствие принудительного насчета показания рассматриваемых счетчиков не соответствуют двоичной системе счисления. По этой причине их относят к классу счетчиков с «произвольным» порядком счета. Способ реализации счетчиков с принудительным насчетом показан на примере функциональной схемы счетчика с Ксч = 10 (рисунок 2.29).

Рисунок 2.29 – Функциональная схема декадного счетчика

с принудительным насчетом

До записи «1» в четвертый разряд, т. е. до прихода восьмого счетного импульса, счетчик работает как двоичный (таблица 2.5). С приходом восьмого счетного импульса «1» записывается в триггер Т4 с осуществлением обратной связи на запись «1» во вторую и третью ячейки.

Таблица 2.5 – Состояние триггеров счётчика с принудительным счётом

| Число входных импульсов | Т4 | Т3 | Т2 | Т1 |

| 8*®14 | ||||

Таким образом, после восьмого счетного импульса вследствие принудительного насчета в счетчик записывается число 8 + 6 = 14. Девятый счетный импульс устанавливает «1» в триггере Т1, а десятый счетный импульс возвращает счетчик в исходное нулевое состояние.

Счетчики с Ксч = 10 называют десятичными, или декадными. Они нашли широкое применение для регистрации числа импульсов с последующим визуальным отображением результата.

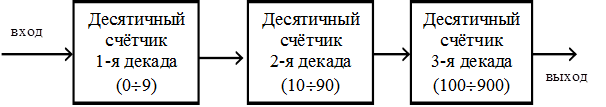

Десятичные счетчики часто включают последовательно (рисунок 2.30).

Рисунок 2.30 – Последовательное соединение декадных счётчиков

Если в пределах всех декад счет ведется в двоичной системе счисления, то, например, числу 978 будет отвечать код 1001 0111 1000, характеризующий двоично-десятичную систему счисления.

Электронная промышленность выпускает широкую номенклатуру интегральных схем счётчиков. Типичным представителем является счётчик 531ИЕ16 – синхронный, реверсивный, декадный, двоично-десятичный счётчик. Эта ИС позволяет строить счётчики с предустановкой, строить комбинированные схемы счётчиков, управлять их коэффициентом счёта и управлять направлением счёта.

Современными счётчиками КМОП ИС являются микросхемы КР1554 ИЕ6, ИЕ7, ИЕ10, ИЕ18 и ИЕ23, имеющие примерное время задержки распространения в диапазоне 9-22 нс. Развитие этой технологии – серии 5514 и 5554. Кроме счётчиков в сериях общего назначения имеются счётчики и в сериях сверхбыстродействующих ИС. Микросхемы серии 6500 (буферизированная полевая логика, материал GaAs) работают на максимальной частоте не менее 1000 МГц и имеют время задержки распространения 1-2 нс. Так, 6500ИЕ4 – 4-разрядный двоичный счётчик с предустановкой. Напряжения питания ИС этой серии – 4 В и минус 2,5 В. Выход – с открытым истоком, сопротивление внешней нагрузки – 50 Ом.

Особо стоит сверхбыстродействующая серия 193, используемая с закрытым входом (с разделительным конденсатором) и имеющая высокую чувствительность, но работающая от конечного значения нижней входной частоты. Так, счётчик К193ИЕ9 с коэффициентом счёта 4 работает на нижней частоте 150 МГц при напряжении 0,6 В и на верхней 1,3 ГГц, а при нескольких милливольтах на частоте 1150 МГц. Счётчик Н193ПЦ5 работает в диапазоне частот 1500-3000 МГц. В этой серии имеются микросхемы для построения сверхвысокочастотных делителей частоты с управляемым коэффициентом деления. У этих ИС есть управляющий вход, изменяющий коэффициент счёта дискретно: так, счётчик 193ИЕ8 имеет управляемый коэффициент счёта 20/22, а микросхема ИЕ2 – коэффициент 10/11.

|

|

|

|

Дата добавления: 2014-01-13; Просмотров: 4215; Нарушение авторских прав?; Мы поможем в написании вашей работы!