КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Организация микросхем памяти

|

|

|

|

Статическая и динамическая ОП /оперативная память

Организация микросхем памяти

Лекция № 12 /2 Память - 2

Некоторые операции над массивами.

Вывод элементов одномерного массива на экран

Ввод элементов одномерного массива

– с помощью оператора присваивания:

1) Непосредственное присваивание конкретного значения элементу массива в программе:

a[1]:= 8;

a[2]:= 15;

a[10]:= 71;

2) Присваивание значения элементу массива в соответствии с некоторой формулой:

for i:=1 to 8 do

a[i]:=(2*i+3/i)/10;

3) Присваивание случайного значения элементу массива с использованием функции random:

Функция random выдает числа, равномерно распределенные в промежутке от 0 до1.

y[i]:=random;

В качестве аргумента для функции random можно использовать положительное целое число: random(N). В этом случае функция будет выдавать случайные целые числа в промежутке от 0 до N.

for i:=1 to 5 do

X[i]:=random(10);

– с помощью операторов ввода read или readln:

for i:=1 to 10

begin

writeln(‘Введите’,i,’-й элемент: ’);

read(a[i]);

end;

Вывод производится с помощью операторов write и writeln.

for i:=1 to 5 do

writeln(a[i]:4);

for i:=1 to 10 do

write(x[i]:7:2);

Копирование.

Чтобы записать один массив в другой необходимо воспользоваться оператором присваивания для каждого элемента.

for i:= 1 to 10 do

B[i]:= A[i];

Если массив объявлен, как идентичный, то можно использовать оператор присваивания целиком для массива:

B:= A;

Аналогично можно проверять равенства и неравенства массивов:

if a=b...

if a<>b...

Содержание

- конвейерный;

- • регистровый;

- • страничный;

- • пакетный;

- • удвоенной скорости.

2. Оперативные запоминающие устройства………….8

Статические ОЗУ…………………………………………………………9

динамические ОЗУ ……………………………………..10

3.Обнаружение и исправление ошибок …………………………16

Литература Глава 5. Памятьстр.207-220

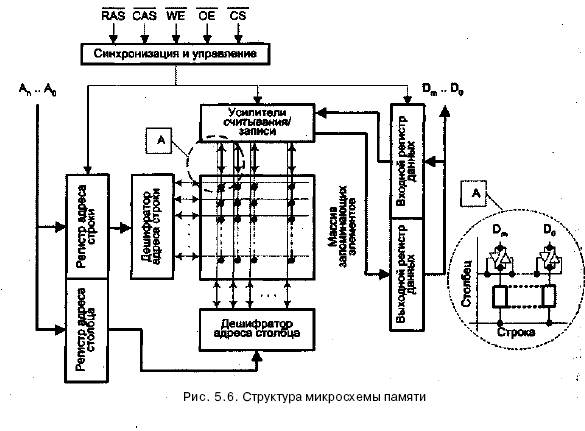

Интегральные микросхемы (ИМС) памяти организованы в виде матрицы ячеек,

каждая из которых, в зависимости от разрядности ИМС, состоит из одного или

более запоминающих элементов (ЗЭ) и имеет свой адрес. Каждый ЗЭ способен

хранить один бит информации. Для ЗЭ любой полупроводниковой памяти харак-

терны следующие свойства:

• два стабильных состояния, представляющие двоичные 0 и 1;

• в ЗЭ (хотя бы однажды) может быть произведена запись информации, посред-

ством перевода его в одно из двух возможных состояний;

• для определения текущего состояния ЗЭ его содержимое может быть считано.

При матричной организации ИМС памяти (рис. 5.6) реализуется координат-

ный принцип адресации ячеек. Адрес ячейки, поступающий по шине адреса ВМ,

пропускается через логику выбора, где он разделяется на две составляющие: адрес

строки и адрес столбца. Адреса строки и столбца запоминаются соответственно

в регистре адреса строки и регистре адреса столбца микросхемы. Регистры соеди-

нены каждый со своим дешифратором. Выходы дешифраторов образуют систему

горизонтальных и вертикальных линий, к которым подсоединены запоминающие

элементы матрицы, при этом каждый ЗЭ расположен на пересечении одной гори-

зонтальной и одной вертикальной линии.ЗЭ, объединенные общим ≪горизонтальным≫ проводом,

принято называть стро-кой (row). Запоминающие элементы, подключенные к общему ≪вертикальному≫

проводу, называют столбцом (column). Фактически ≪вертикальных≫ проводов

в микросхеме должно быть, по крайней мере, вдвое больше, чем это требуется для

адресации, поскольку к каждому ЗЭ необходимо подключить линию, по которой

будет передаваться считанная и записываемая информация.

Совокупность запоминающих элементов и логических схем, связанных с выбо-

ром строк и столбцов, называют ядром микросхемы памяти. Помимо ядра в ИМС

имеется еще интерфейсная логика, обеспечивающая взаимодействие ядра с внеш-

ним миром. В ее задачи, в частности, входят коммутация нужного столбца на вы-

ход при считывании и на вход — при записи.

На физическую организацию ядра, как матрицы однобитовых ЗЭ, накладывает-

ся логическая организация памяти, под которой понимается разрядность микросхе-

мы, то есть количество линий ввода/вывода. Разрядность микросхемы определяет

количество ЗЭ, имеющих один и тот же адрес (такая совокупность запоминающих

элементов называется ячейкой), то есть каждый столбец содержит столько разря-

дов, сколько есть линий ввода/вывода данных.

Для уменьшения числа контактов ИМС адреса строки и столбца в большин-

стве микросхем подаются в микросхему через одни и те же контакты последова-

тельно во времени (мультиплексируются) и запоминаются соответственно в реги-

стре адреса строки и регистре адреса столбца микросхемы. Мультиплексирование

обычно реализуется внешней по отношению к ИМС схемой

Для синхронизации процессов фиксации и обработки адресной информации

внутри ИМС адрес строки (RA) сопровождается сигналом RAS (Row Address

Strobe — строб строки), а адрес столбца (СА) — сигналом СAS (Column Address

Strobe — строб столбца). Вторую букву в аббревиатурах RAS и CAS иногда рас-

шифровывают как Access — ≪доступ≫, то есть имеется строб доступа к строке и строб

доступа к столбцу. Чтобы стробирование было надежным, эти сигналы подаются

с задержкой, достаточной для завершения переходных процессов на шине адреса

и в адресных цепях микросхемы.

Сигнал выбора микросхемы CS (Crystal Select) разрешает работу ИМС и ис-

пользуется для выбора определенной микросхемы в системах, состоящих из не-

скольких ИМС. Вход WE (Write Enable — разрешение записи) определяет вид

выполняемой операции (считывание или запись).

Записываемая информация, поступающая по шине данных, первоначально за-

носится во входной регистр данных, а затем — в выбранную ячейку. При выполне-

нии операции чтения информация из ячейки до ее выдачи на шину данных буфе-

ризируется в выходном регистре данных. Обычно роль входного и выходного

выполняет один и тот же регистр. Усилители считывания/записи (УСЗ) служат

для электрического согласования сигналов на линиях данных и внутренних сиг-

налов ИМС. Обычно число УСЗ равно числу запоминающих элементов в строке

матрицы, и все они при обращении к памяти подключаются к выбранной горизон-

тальной линии. Каждая группа УСЗ, образующая ячейку, подключена к одному из

столбцов матрицы, то есть выбор нужной ячейки в строке обеспечивается активи-

зацией одной из вертикальных линий. На все время пока ИМС памяти не исполь-

зует шину данных, информационные выходы микросхемы переводятся в третье

(высокоимпедансное) состояние. Управление переключением в третье состояние

обеспечивается сигналом ОЕ (Output Enable — разрешение выдачи выходных сиг-

налов). Этот сигнал активизируется при выполнении операции чтения.

Для большинства перечисленных выше управляющих сигналов активным обыч-

но считается их низкий уровень, что и показано на рис. 5.6.

Управление операциями с основной памятью осуществляется контроллером

памяти. Обычно этот контроллер входит в состав центрального процессора либо

реализуется в виде внешнего по отношению к памяти устройства. В последних

типах ИМС памяти часть функций контроллера возлагается на микросхему памяти.

Хотя работа ИМС памяти может быть организована как по синхронной, так и по

асинхронной схеме, контроллер памяти — устройство синхронное, то есть сраба-

тывающее исключительно по тактовым импульсам. По этой причине операции с

памятью принято описывать с привязкой к тактам. В общем случае на каждую та-

кую операцию требуется как минимум пять тактов, которые используются следу-

ющим образом:

1. Указание типа операции (чтение или запись) и установка адреса строки.

2. Формирование сигнала RAS.

3. Установка адреса столбца.

4. Формирование сигнала CAS.

5. Возврат сигналов RAS и CAS в неактивное состояние.

Типовую процедуру доступа к памяти рассмотрим на примере чтения из ИМС с мультиплексированием адресов строк и столбцов. Сначала на входе WE уста-навливается уровень, соответствующий операции чтения, а на адресные контакты ИМС подается адрес строки, сопровождаемый сигналом RAS. По заднему фронту этого сигнала адрес запоминается в регистре адреса строки микросхемы, после чего дешифрируется. После стабилизации процессов, вызванных сигналом RAS, вы-бранная строка подключается к УСЗ. Далее на вход ИМС подается адрес столбца, который по заднему фронту сигнала СAS заносится в регистр адреса столбца. Од-новременно подготавливается выходной регистр данных, куда после стабилиза-ции сигнала CAS загружается информация с выбранных УСЗ.

Разработчики микросхем памяти тратят значительные усилия на повышение быстродействия ИМС, которое принято характеризовать четырьмя параметрами (численные значения приводятся для типовой микросхемы динамической памяти емкостью 4 Мбит):

• t^s — минимальное время от перепада сигнала RAS с высокого уровня к низко-му до момента появления и стабилизации считанных данных на выходе ИМС.Среди приводившихся в начале главы характеристик быстродействия это со-ответствует времени доступа Гд (t^ = 60 нс);

• tKC — минимальное время от начала доступа к одной строке микросхемы памя-ти до Начала доступа к следующей строке. Этот параметр также упоминался в начале главы как длительность цикла памяти Гц (tRC = 110 нс при t^s = 60 нс);

• tCAS — минимальное время от перепада сигнала CAS с высокого уровня к низко-му до момента появления и стабилизации считанных данных на выходе ИМС (tCAS = 15 не при ^RAS= 60 нс);

• ТРС — минимальное время от начала доступа к одному столбцу микросхемы па-мяти до начала доступа к следующему столбцу (£РС = 35 нс при t^s = 60 нс).

Возможности ≪ускорения ядра≫ микросхемы ЗУ весьма ограничены и связаны в основном с миниатюризацией запоминающих элементов. Наибольшие успехи достигнуты в интерфейсной части ИМС, касаются они, главным образом, операции чтения, то есть способов доставки содержимого ячейки на шину данных. Наибольшее распространение получили следующие шесть фундаментальных подходов:

• последовательный;

• конвейерный;

• регистровый;

• страничный;

• пакетный;

• удвоенной скорости.

|

|

|

|

|

Дата добавления: 2014-01-14; Просмотров: 400; Нарушение авторских прав?; Мы поможем в написании вашей работы!