КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Федеральный закон

|

|

|

|

Система команд 8-разрядного микропроцессора.......................................

Регистры микропроцессора...............................................................

Формат команд...................................................................................

Архитектура 8-разрядного процессора.......................................................

Устройство ячеек памяти. Статическая, динамическая память........

Типы памяти. ПЗУ, ОЗУ.....................................................................

Память микропроцессорных систем.............................................................

Тристабильные схемы........................................................................

Триггеры, регистры............................................................................

Логические элементы..........................................................................

Схемотехника ЭВМ.......................................................................................

Типы систем счисления.......................................................................

История развития ЭВМ. Системы счисления.............................................

Exercise 7. Number this jumbled conversation in the correct order.

-I'll sign them this afternoon and send them back to you.

- Hello. My name's Beata Szlachetka. I'd like to speak to Kate Chapman please.

-Good morning. IKI Industries. How may I help you?

-Hold the line, please. I'll see if she's in.

-Great. Thanks a lot.

-(pause) Hello. Kate Chapman speaking.

-Beata Szlachetka and I'd like to speak to Kate Chapman.

-Hello, this is Beata.

-Sorry. I didn't quite catch that.

-Hi, Beata. How are you doing?

-OK. Busy as usual.

-Fine, thanks. And you?

-Yeah, they came this morning but I haven't signed them yet.

-I'm just ringing to find out if you've received the copies of the contract.

-OK, there's no rush.

Exercise 8. Complete this UNIT about a telephonist's job with the correct form of nouns and verbs

I work on the a …. so I answer all the calls that come in.

When the phone b …. I answer it and I say "Hello, Worldwide Limited. Can I help you?". The person on the other end c …. somebody in the company and I try to d…. them. The company closes at about six in the evening, but we leave the e …. on all night and at weekends. I listen to the f …. when I arrive in the morning.

Exercise 9. Write what a secretary says:

a) if the caller wants to leave a message.

b) if the boss is out at the moment.

c) if the caller is to wait.

d) if the caller wants someone to call him back.

РЕКОМЕНДУЕМАЯ ЛИТЕРАТУРА

Основная литература:

Дополнительная литература:

1.2. Арифметические операции в двоичной системе счисления..............

1.3. Представление отрицательных чисел в двоичной системе счисления

1.4. Кодирование информации …………………………………………….

3.3. Модули памяти …………………………………………………………..

3.4. Карта памяти ……………………………………………………………..

4.3. Дешифратор команд, устройство управления …………………………

4.4. Арифметико-логическое устройство, регистр признаков……………..

4.5. Временные диаграммы работы микропроцессора …………………….

4.6. Работа микропроцессорной системы……………………………………

5.1. Типы команд…………………………………………………………….

5.2. Команды пересылок ……………………………………………………

5.3. Арифметические команды …………………………………………….

5.4. Логические команды ………………………………………………….

5.5. Команды условных и безусловного перехода

Литература........................................................................................................

Введение

Современные ЭВМ используют различные микропроцессорные наборы, которые имеют общие принципы устройства и временные диаграммы работы.

В настоящее время вычислительные мощности процессоров значительно превосходят 8-разрядные процессоры, которые, тем не менее, применяются для реализации микропроцессорных приборов, регуляторов и простых и дешевых контроллеров для управления несложными объектами управления, не требующими высокого быстродействия и имеющими небольшое количество входных и выходных переменных.

В то же время рассмотрение 8-разрядных процессоров позволяет в наглядной и доступной форме рассмотреть и изучить устройство микропроцессора, проследить технологию обработки данных в микропроцессоре.

В учебном пособии основное внимание уделяется вопросам, связанным с устройством и работой микропроцессоров и микроконтроллеров, их программным обеспечением, разработкой программ на языке Ассемблер.

Данное пособие отражает содержание первого модуля дисциплины "Микропроцессорная техника":

· Модуль 1 – Устройство и работа микропроцессора

· Модуль 2 - Устройство и работа микроконтроллера

· Модуль 3 – Программирование микроконтроллеров

· Модуль 4 – Архитектура ЭВМ

· Модуль 5 - Интерфейсы ЭВМ

· Модуль 6 – Курсовая работа

Цель практических занятий – закрепление теоретических знаний и приобретение практических навыков по разработке микропроцессорных систем и их программного обеспечения для решения задач локальной автоматизации.

1. История развития ЭВМ. Системы счисления.

1.1. История развития ЭВМ.

Первые механические вычислительные устройства, счеты, появились еще в античном мире. За 1000 лет до нашей эры появились счеты в Китае и Японии, счеты имели форму бус, укрепленных на специальной раме. Бусы назывались калькулями [1].

Следующим этапом развития вычислительных устройств является создание Б.Паскалем в 1647 г. арифметической машины, которая использовала принцип колес от 0 до 9. В 1966 г. С.Морланд создал суммирующее и вычитающее устройство, а в 1673 г. был изготовлен калькулятор Морланда с умножением чисел.

Лейбниц реализовал вычислительное устройство для умножения и деления чисел.

Отцом вычислительной техники считается Ч.Бэббедж. Он в 1821 г. создал специализированные машины для вычисления разностей между числами, а в начале 30-х годов 19-го века приступил к созданию универсальной вычислительной машины, так как понимал ограниченность разностных машин.

Он первым пришел к заключению, что компьютер должен иметь 5 основных блоков:

- устройство ввода числовой информации (ими были вначале перфокарты Жакара для ткацких станков);

- память для хранения чисел и программ (перфокарта);

- арифметическое устройство;

- устройство управления для контроля над ходом выполнения программы;

- устройство вывода результатов.

В 1890 г. американский ученый Г.Холерит изобрел устройство для анализа результатов переписи населения США, которое было основано на использовании перфокарт с отверстиями, через которые замыкался контакт. На основе реализации данного изобретения в дальнейшем образовалась известная фирма IBM (International Business Machines).

К началу 40-х годов прошлого века стало возможным использовать в качестве элементов схем цифровых машин электролампы и дальнейшее развитие вычислительной техники пошло в направлении использования усилительных элементов, работающих в ключевом режиме с двумя состояниями "да" и "нет".

Развитие средств вычислительной техники развивалось одновременно в нескольких странах. В США, Великобритании, Германии.

В Германии в 1935 г. К.Цузе создает ЭВМ Z1 и патентует ее. В 1941 г. он создает ЭВМ Z3 – двоичный программируемый компьютер, в 1945 г. – первый язык программирования высокого уровня. В дальнейшем его компания влилась в компанию Сименс.

В США в 1943 г. в Гарварде была создана ЭВМ MARK-1, в Великобритании – Colossus-1 – для расшифровки сообщений немецких передатчиков.

Разработка вычислительной техники была стимулирована поставленными задачами науки и техники, которые начали требовать значительного объема расчетных операций, причем их необходимо было выполнять быстро.

Эти задачи были связаны с решением задач управления, а именно управления огнем зенитной артиллерии, расшифровкой радиограмм. В это же время начала зарождаться наука об управлении живыми и неживыми объектами – кибернетика.

Отцом кибернетики считается американский ученый Норберт Винер. Он вместе с мексиканским профессором медицины проанализировал патологии поведения человека при различным заболеваниях нервной системы и сформулировал понятие обратной связи, которое является основополагающим в теории управления.

В 1946 г. Дж.Макли и Дж.Эккерт (Пенсильванский университет) создали ЭВМ ENIAC (Electronic Numerical Integrator and Calculator) – для быстрого вычисления баллистических таблиц для орудий и ракет. Она состояла из 18000 ламп, объем памяти – 20 десятиразрядных чисел, потребление энергии – 150 кВт.

В 1945 г. Дж.фон Нейман приступил к проектированию машины EDVAC (Electronic Discrete Variable Automatic Computer). В проекте этой ЭВМ была реализована концепция управляющей программы, хранимой в памяти машин, а также идея, что с командами можно обращаться так же, как и с информацией, то в этом случае программа может модифицироваться сама в ходе ее исполнения.

В 1947 г. в Кембридже была создана ЭВМ EDSAC (Electronic Delay Storage Automatic Computer). Для нее была создана операционная система.

В 1958 г. появились промышленные образцы транзисторов, которые заменили лампы, что позволило значительно уменьшить габариты вычислительных машин, сократить энергопотребление, повысить их быстродействие. Это привело к созданию машин второго поколения.

В 1965 г. были выпущены интегральные схемы, которые заменили отдельные компоненты ЭВМ, что привело к дальнейшему сокращению габаритов и энергопотребления. Повысилась надежность работы машин, которые были уже машинами третьего поколения. Эти ЭВМ стали применяться для решения задач управления технологическими процессами.

В 1959 г. разработчики фирмы Datapoint (США) разработали первый микропроцессор и предложили фирме Intel реализовать его. Но характеристики этого процессора по быстродействию оказались хуже, чем ожидалось, и фирма Datapoint отказалась от продолжения дальнейших исследований. Фирма Intel тем не менее продолжила исследования, так как уже понесла затраты на разработку, и добилась необходимых результатов. Появился первый микропроцессор Intel 8008 на мировом рынке.

В СССР первые отечественные ЭВМ были созданы под руководством академиков С.А.Лебедева, Ю.А.Базилевского и И.С.Брука. Это малые машины "Наири", "Мир" а также уникальная по быстродействию машина – БЭСМ-6.

1.2.Системы счисления

Развитие вычислительной техники привело к расширению использования различных систем счисления. Обычно используется десятичная система счисления. Однако ее применение для реализации вычислительных процессов с помощью электронных устройств сопряжено с трудностью распознавания десяти различных уровней сигналов, которые бы соответствовали бы различных цифрам. Поэтому в вычислительной технике для реализации вычислений и представления чисел и кодов команд используют двоичную систему счисления, которая имеет две цифры 0 и 1 и для реализации которых в технических устройствах необходимо два уровня сигналов: высоки и низкий, есть сигнал или нет сигнала.

Система счисления определяет правило представления числа из комбинации цифр данной системы счисления. В десятичной системе счисления, которой мы пользуемся повседневно, имеется десять цифр, комбинация которых определяет число. При представлении числа из цифр имеет значение, на каком месте стоит цифра. Место определяет вес данной цифры. Одна и та же цифра может определять количество единиц, десятков, сотен и т.д., все зависит от ее месторасположения в числе.

Такие системы счисления называются позиционными системами счисления по основанию [2]. В этих системах используется конечный набор символов, каждый символ называется цифрой и обозначает некоторое количество. Число различных цифр в наборе называется основанием системы счисления. Чтобы получить какое-либо число, необходимо цифры записать рядом. Относительной позиции цифры в числе ставится в соответствие весовой множитель (коэффициент).

В десятичной системе счисления 10 цифр: 0, 1, … 9. Представление числа в десятичной системе счисления можно представить следующим образом в виде полинома. Например, число 678 будет иметь вид:

Здесь цифра 6 входит с весом 100, цифра 7 – с весом 10, цифра 8 – с весом 1.

В общем виде данное выражение можно представить следующим образом:

, (1.1)

, (1.1)

где  - цифры числа;

- цифры числа;

- весовые коэффициенты.

- весовые коэффициенты.

В таблице 1.1 приведены наиболее употребительные системы счисления и их характеристики.

Таблица 1.1, Системы счисления

| Основание | Система счисления | Обозна-чение | Цифровые символы |

| Двоичная | b | 0,1 | |

| Троичная | 0,1,2 | ||

| Четверичная | 0,1,2,3 | ||

| Пятеричная | 0,1,2,3,4 | ||

| Восьмеричная | o | 0,1,2,3,4,5,6,7 | |

| Десятичная | d | 0,1,2,3,4,5,6,7,8,9 | |

| Двенадцатеричная | 0,1,2,3,4,5,6,7,8,9,A,B | ||

| Шестнадцатеричная | h | 0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F |

Наибольшее применение в вычислительной технике, наряду с десятичной системой счисления, получили двоичная, восьмеричная и шестнадцатеричная системы счисления. Для различия систем счисления применяют следующие обозначения:

100(10), 100(d) – число представлено в десятичной системе счисления;

100(2), 100(b) - число представлено в двоичной системе счисления;

100(8), 100(o) - число представлено в восьмеричной системе счисления;

100(16), 100(h) - число представлено в шестнадцатеричной системе счисления.

1.3.Двоичная система счисления

Двоичная система счисления использует только две цифры 0 и 1, что позволяет использовать эту систему счисления техническими устройствами для выполнения арифметических операций [3]. Данные технические устройства имеют два устойчивых состояния: включено-выключено, низкий-высокий уровень.

В двоичной системе счисления каждой позиции соответствует определенный вес, который определяется как степень числа 2, так как основание двоичной системы счисления равно 2. Из-за того, что данная система счисления имеет две цифры, разрядность двоичных чисел значительно больше разрядности десятичных чисел.

Представление двоичных чисел и их перевод в десятичное число осуществляется по выражению (1.1)

1011012 = 1*25 + 0*24 + 1*23 + 1*22 + 0*21 + 1*20 =

= 1*32 + 0*16 + 1*8 + 1*4 + 0*2 +1*1 = 4510

При записи двоичного числа каждая позиция занята двоичной цифрой, которая называется битом. Слово бит искусственное, оно произошло как сокращение от двух слов: binary digit (двоичная единица) - bit.

При рассмотрении двоичных чисел пользуются понятиями наименьший значащий бит (самый младший двоичный разряд) и наибольший значащий бит (самый старший двоичный разряд). Обычно двоичное число записывается так, что наибольший значащий бит является крайним слева.

Перевод из десятичной системы в двоичную систему счисления осуществляется следующим образом. Преобразование осуществляется многократным делением десятичного числа на 2. Например, перевод десятичного числа 35 в двоичное число

35:2=17 остаток 1 = a0

17:2=8 остаток 1 = a1

8:2 =4 остаток 0 = a2

4:2 =2 остаток 0 = a3

2:2 =1 остаток 0 = a4

2:2 =1 остаток 0 = a4

1 = a5

Таким образом, двоичное число будет иметь вид a5a4a3a2a1a0

1000112 = 1*25 + 0*24 + 0*23 + 0*22 + 1*21 + 1*20 =

1*32 + 0*16 + 0*8 + 0*4 + 1*2 +1*1 = 3510

1.4.Шестнадцатеричная система счисления

В шестнадцатеричной системе счисления используются 16 цифр: 0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F. Шестнадцатеричная система счисления используется как средство сокращенной записи 4-х разрядного двоичного числа. В таблице 1.2 приведены шестнадцатеричные числа и их двоичные и десятичные эквиваленты.

Таблица 1.2

| Шестнадца- теричное число | Двоичное число | Десятичное число | Шестнадца- теричное число | Двоичное число | Десятичное число |

| A | 1A | ||||

| B | 1B | ||||

| C | 1C | ||||

| D | 1D | ||||

| E | 1E | ||||

| F | 1F |

Преобразование двоичного числа в шестнадцатеричное число заключается в том, что биты, начиная с младшего значащего бита, объединяются в группы по четыре. Каждой группе подбирается соответствующий шестнадцатеричный символ. Например, чтобы представить двоичное число 1010101111111012 в виде шестнадцатеричного числа необходимо слева добавить два незначащих нуля с целью формирования битов в группы по четыре: 0010 1010 1111 1101. Заменив каждую группу битов соответствующим шестнадцатеричным символом, получим число 2AFD16.

Данная форма записи намного проще и воспринимается легче, чем двоичная.

Нужно помнить, что шестнадцатеричные числа – это способ представления двоичных чисел, которыми оперирует микропроцессор.

Представление шестнадцатеричного числа в виде двоичного также осуществляется по выражению (1.1).

2AFD16 = 2*163 + A*162 + F*161 + D*160 =

2*4096 + 10*256 + 15*16 + 13*1 =

8192 + 2560 + 240 + 13 = 1100510

101010111111012 = 1*213 + 0*212 + 1*211 +0*210 + 1*29 +0*28 +

+ 1*27 + 1*26 + 1*25 + 1*24 + 1*23 + 1*22 +0*21 +1*20 =

= 8192 + 0 + 2048 + 0 + 512 + 0 + 128 + 64 + 32 + 16 +

+ 8 + 4 + 0 + 1 = 1100510

1.5. Двоичная арифметика

Четыре основные арифметические операции, а именно сложение, вычитание, умножение, деление можно выполнять в позиционной системе счисления с любым основанием.

Сложение двух двоичных чисел

| a | b | a+b |

| 1+1+1 |

Правила сложения двоичных и десятичных чисел аналогичны, но в результате более быстрого заполнения разрядов в двоичной системе счисления быстрее происходит и перенос в старший разряд при сложении двоичных чисел.

Прибавление единицы к старшему разряду в результате переполнения соседнего, младшего разряда называют переносом.

Сложение двоичных чисел выполняется по тем же правилам, что и сложение десятичных чисел. Например, сложение двоичных чисел 1101010 и 1101100 происходит следующим образом. В первом младшем разряде слагаемыми являются 0 и 0, результат получается 0. Во втором разряде к 1 прибавляется 0, результат получается 1. В третьем разряде к 0 прибавляется 1, результат получается 1. В четвертом разряде результатом сложения 1 с 1 является 10. Единицу переноса записываем над пятым разрядом, в котором суммирование 1,0 и 0 дает в результате 1. В шестом разряде снова суммируются 1 и 1, результат получается 10. Аналогичным образом единицу переноса записываем над седьмым разрядом, в котором теперь необходимо сложить три единицы. Результат есть 11. Единицу переноса располагаем над восьмым разрядом, который пуст для обоих слагаемых, поэтому в результате сложения в восьмом разряде появится 1. Порядок сложения приведен на рис.1.1.

| Разряд | ||||||||

| ЧислоА | ||||||||

| Число В | ||||||||

| Сумма |

| Разряд | ||||||||

| Перенос |  1 1

| |||||||

| ЧислоА | ||||||||

| Число В | ||||||||

| Сумма | (1)0 |

| Разряд | ||||||||

| Перенос |  1 1

|  1 1

| ||||||

| ЧислоА | ||||||||

| Число В | ||||||||

| Сумма | (1)1 | (1)0 |

Рис.1.1. Схема сложения двух чисел.

Вычитание двоичных чисел

Вычитание десятичных чисел является более привычным и на их примере можно понять механизм вычитания двоичных чисел. Например, вычтем 17283 (вычитаемое) из числа 909009 (уменьшаемого). Вычитание начинают с самого правого разряда. Вычитая 3 из 9, получаем 6.

| Разряд | ||||||

| Число А | ||||||

| Число В | ||||||

| Разность |

| Разряд | ||||||

| Число А |  (10) (10)

| |||||

| Число В | ||||||

| Разность |

| Разряд | ||||||

| Число А | (10) | |||||

| Число В |

| |||||

| Разность |

Рис.1.2. Схема вычитания двух десятичных чисел

В следующем разряде необходимо вычесть 8 из 0, что непосредственно сделать невозможно, так как 8 > 0. Чтобы осуществить дальнейшие вычисления необходимо обратиться к разрядам, расположенным слева, для нахождения числа, не равного 0. В данном случае таким числом будет 9. Занимаем 1 из 9, в результате чего в четвертом разряде вместо 9 появляется 8, в третьем разряде вместо 0 появляется 9, во втором разряде – 10.

Теперь во втором разряде из 10 можно отнять 8, получив 2. В третьем разряде нужно вычесть 2 из 9, получим 7. В четвертом разряде вычитаем 7 из 8, получаем 1. В пятом разряде нужно вычесть 1 из 0. Для этого необходимо опять занять 1, двигаясь влево до тех пор, пока не дойдем до первого ненулевого разряда. В нем 9 заменяем на 8, а вместо 0 в пятом разряде получаем 10. Теперь вычисления можно продолжить.

Для двоичных чисел процесс вычисления приведен на рис.1.3.

| Разряд | ||||||||

| ЧислоА |  1 1

| |||||||

| Число В | ||||||||

| Разность |

| Разряд | ||||||||

| ЧислоА | (10) | |||||||

| Число В | ||||||||

| Разность |

| Разряд | ||||||||

| ЧислоА |  (10) (10)

| |||||||

| Число В | ||||||||

| Разность |

Результат вычисления в правом разряде 1-1 = 0. Во втором разряде вычесть 1 из 0 просто так не удастся, и поэтому просматриваем разряды справа налево до тех пор, пока не найдем 1. Добавляем 1 к 0 во втором разряде, что дает 10 (один, нуль). Числу 102 соответствует десятичное число 2. Нули, которые стоят между двумя разрядами, обращаются в единицы. Во втором разряде вычитаем из 102 – 12 и получаем 12. В третьем и четвертом разрядах результат вычитания будет равен 0.В пятом разряде опять из 0 нужно вычесть 1, для чего опять производится заем, как и в случае, описанном выше.

Если уменьшаемое больше вычитаемого, то разность получается положительной, если наоборот, то результат будет отрицательным.

Дополнительный код двоичного числа

Так как вычислительная машина оперирует с цифрами 0 и 1, то знаки + и -, предназначенные для обозначения положительных и отрицательных чисел, отсутствуют. Для представления положительных и отрицательных чисел в двоичной системе счисления и вычислительной технике используют старший значащий разряд двоичного числа. Если он равен 1, то число будет отрицательным, если он равен 0, то число будет положительное.

Такая форма представления чисел получается, если двоичное число представить следующим образом:

Такое представление называют дополнительным кодом двоичного числа. В этом случае старший значащий разряд имеет вес не  , а

, а  . Если в этом разряде стоит 1, то он будет представлять десятичное число -128 и число в целом окажется отрицательным, так как наибольшее число, содержащееся в разрядах

. Если в этом разряде стоит 1, то он будет представлять десятичное число -128 и число в целом окажется отрицательным, так как наибольшее число, содержащееся в разрядах  , не может превысить десятичное значение 127.

, не может превысить десятичное значение 127.

Таким образом, двоичное число 10110001 можно представить как

1*(-128)+0*64+1*32+1*16+0*8+0*4+0*2+1*1=-79

Если в старшем значащем разряде стоит 0, подобная запись представляет собой положительное число, так как у всех остальных разрядов  веса положительны. Например,

веса положительны. Например,

01001000=0*(-128)+1*64+0*32+0*16+1*8+0*4+0*2+0*1=72

Для того чтобы представить отрицательное десятичное число в двоичной форме, необходимо это число записать как положительное в двоичном виде. После этого записать обратный код двоичного числа, а затем добавить к обратному коду двоичного числа единицу, в результате чего получим дополнительный код двоичного числа, который будет равен отрицательному десятичному числу. Рассмотрим следующий пример. Представить в двоичном виде отрицательное число – 77. Для этого получим двоичное число положительного числа 77.

77 = 01001101

Обратный код этого числа получим заменой 0 на 1, и 1 на 0.

Для получения дополнительного кода прибавим к обратному коду 1.

10110010 – обратный код

+ 1

10110011 – дополнительный код числа 77

Проверим, чему равно двоичное число 10110011

1*(-128)+0*64+1*32+1*16+0*8+0*4+1*2+1*1= -77

Таким способом можно представить числа в диапазоне от 10000000=-128 до 01111111=+127. Если этот диапазон недостаточен, то необходимо использовать шестнадцатиразрядные числа, которые образуются путем объединения двух 8-разрядных слов.

Использование дополнительных кодов двоичных чисел значительно упрощают операции двоичного вычитания, так как вычитание можно сложением положительного и отрицательного чисел. Например,

17-22= 17+(-22)

В двоичном виде это значит, что нужно сложить 00010001 = 17 и дополнительный код числа 00010110 = 22. Дополнительный код числа 00010110 получим, преобразовав его в обратный код 11101001 и прибавив к обратному коду 1.

00010110 – двоичный код числа 22

11101001 – обратный код

+ 1

11101010 – дополнительный код

После этого складываем

00010001 17

+

11101010 -22

=

11111011

Представим 11111011 в десятичном виде

1*(-128)+1*64+1*32+1*16+1*8+0*4+1*2+1*1= -5

Умножение двоичных чисел

Правила двоичного умножения

0*0=0

0*1=0

1*0=0

1*1=1

Умножение двух двоичных чисел осуществляется так же, как и умножение десятичных чисел. Возьмем два числа 9*3=27, в двоичном виде запишем их так

1001

* 11

=

1001

+ 1001

= 11011

11011= 1*16+1*8+0*4+1*2+1*1= 27

Двоично-десятичный код BCD (Binary Coded Decimal)

Двоично-десятичный код позволяет представлять в вычислительной машине десятичные цифры 0,…,9 с помощью символов двоичного алфавита.

При двоично-десятичном кодировании каждая десятичная цифра заменяется соответствующим 4-разрядным двоичным числом. Например, число 12 представляется следующим образом. Находим двоичное число для цифры 1 – 0001, находим двоичное число для цифры 2 – 0010, тогда двоично-десятичный код числа 12 будет иметь вид 0001 0010.

Системы кодирования

Для того чтобы иметь возможность оперировать не только с числами, но и символами, чтобы можно было представлять в ЭВМ текстовую информацию, используют системы кодирования, в которых каждому символу ставят в соответствие определенную комбинацию нулей и единиц.

В микроЭВМ наиболее часто используют два кода: американский стандартный код для обмена информацией ASCII (American Standard Code for Information Interchange) и расширенный двоично-кодированный EBCDIC (Extended Binary Coded Decimal Interchange).

Кроме этих кодов используются коды КОИ-7, КОИ-8 и др.

2. Схемотехника ЭВМ

2.1. Логические элементы

ЭВМ состоит не только из центрального процессора (микропроцессора). Он является главной, но лишь одной из многих интегральных микросхем, входящих в состав ЭВМ.

К наиболее распространенным интегральным микросхемам относятся логические элементы, реализующие логические функции И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ, инверторы, исключающее ИЛИ, триггеры, регистры, счетчики.

Данные интегральные микросхемы являются цифровыми. На их входах могут появляться лишь два характерных уровня напряжения: низкое (около 0 В) и высокое (например, 5 В), причем низкий и высокий уровни напряжения представляют собой двоичные значения 0 и 1 соответственно.

Логический элемент И.

Условное графическое изображение логического элемента И представлено на рис.2.1.

Рис.2.1. Графическое изображение логического элемента И.

Так как это цифровая микросхема, то на входы  и

и  подаются входные напряжения, которые могут принимать только фиксированные значения, принятые для данного типа микросхемы, которые определяются разработчиком микросхемы. Для микросхем типа ТТЛ это напряжения 0 В или 5 В. На выходе микросхемы

подаются входные напряжения, которые могут принимать только фиксированные значения, принятые для данного типа микросхемы, которые определяются разработчиком микросхемы. Для микросхем типа ТТЛ это напряжения 0 В или 5 В. На выходе микросхемы  также будут появляться данные напряжения, а какое конкретно – определяется таблицей истинности логического элемента. Для логического элемента И с двумя входами комбинации сигналов на входах элементов и таблица истинности представлены в таблицах 2.1 и 2.2.

также будут появляться данные напряжения, а какое конкретно – определяется таблицей истинности логического элемента. Для логического элемента И с двумя входами комбинации сигналов на входах элементов и таблица истинности представлены в таблицах 2.1 и 2.2.

Таблица 2.1 Комбинация сигналов на входах логического элемента И

,В ,В

|  ,В ,В

|  ,В ,В

|

Таблица 2.2 Таблица истинности логического элемента И

|

|

|

Таким образом, работа логического элемента И описывается следующим правилом: выходной сигнал равен 1 только тогда, когда все входные сигналы равны 1, т.е.  только тогда, когда все

только тогда, когда все  ,

, . Если на одном их входов появляется 0, то и на выходе появляется 0. Это правило аналитически записывается в виде

. Если на одном их входов появляется 0, то и на выходе появляется 0. Это правило аналитически записывается в виде

(2.2)

(2.2)

то есть операция И записывается точкой.

Данная запись заимствована из алгебры Буля, которую можно рассматривать как арифметику систем, построенных на логических элементах.

В ЭВМ арифметико-логическое устройство содержит восемь двухвходовых логических элементов И, что позволяет микро-ЭВМ выполнять операцию над двумя словами А и В, каждое длиной 8 бит.

Логический элемент ИЛИ.

Условное графическое изображение логического элемента ИЛИ представлено на рис.2.2.

Рис.2.2. Графическое изображение логического элемента ИЛИ.

Выходной сигнал логического элемента ИЛИ равен 1, если хотя бы один из входных сигналов равен 1. Аналитически это записывается следующим образом:

(2.2)

(2.2)

Символ + обозначает выполнение операции ИЛИ. Таблица истинности логического элемента ИЛИ приведена в таблице 2.3.

Таблица 2.3 Таблица истинности логического элемента ИЛИ

|

|

|

Инвертор или логический элемент НЕ

Выходной сигнал инвертора противоположен по значению входному сигналу или, другими словами, сигналы на входе и на выходе инвертора всегда не совпадают: если на входе 0, то на выходе 1; если на входе 1, то на выходе 0.

На рис.2.3 дано условное графическое изображение инвертора. Кружок на выходе инвертора означает выполнение операции НЕ.

Рис.2.3. Графическое изображение логического элемента НЕ.

Операция отрицания аналитически записывается в виде

(2.3)

(2.3)

Горизонтальная черта над переменной  читается как "не", т.е.

читается как "не", т.е.  читается как "

читается как " равно не

равно не  ".

".

Логический элемент И-НЕ

Логический элемент И-НЕ отличается от логического элемента И дополнительной операцией отрицания. Условное графическое изображение элемента такое же, как и у элемента И, с добавлением кружка на выходе (рис.2.4.)

Рис.2.4. Графическое изображение логического элемента И-НЕ.

В соответствии с алгеброй Буля операция И-НЕ аналитически записывается следующим образом:

(2.4)

(2.4)

Над переменными  и

и  сначала совершается операция И, результат которой инвертируется.

сначала совершается операция И, результат которой инвертируется.

Правило работы логического элемента И-НЕ заключается в следующем: выходной сигнал равен 0, если все входные сигналы равны 1.

Логические элементы И-НЕ используются достаточно часто, так как любая логическая схема может быть построена исключительно на элементах И-НЕ, то есть можно обойтись элементом одного единственного типа.

Таблица истинности приведена в таблице 2.4.

Таблица 2.4 Таблица истинности логического элемента И-НЕ

|

|

|

Логический элемент ИЛИ-НЕ

Условное графическое изображение приведено на рис.2.5.

Рис.2.5. Графическое изображение логического элемента ИЛИ-НЕ

Таблица истинности приведена в таблице 2.5

Таблица 2.5 Таблица истинности логического элемента ИЛИ-НЕ

|

|

|

В логическом элементе ИЛИ-НЕ совмещено выполнение двух операций: ИЛИ и НЕ, при этом сначала выполняется операция ИЛИ, а затем производится инвертирование.

В логическом элементе ИЛИ-НЕ выходной сигнал равен 1, если все входные сигналы равны 0. Аналитически операция ИЛИ-НЕ записывается следующим образом:

(2.5)

(2.5)

Логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ

В логическом элементе ИСКЛЮЧАЮЩЕЕ ИЛИ выходной сигнал равен 1 только тогда, когда один из входных сигналов равен 1 (табл.2.6).

Таблица 2.6 Таблица истинности логического элемента

ИСКЛЮЧАЮЩЕЕ ИЛИ

|

|

|

Условное графическое изображение приведено на рис.2.6.

Рис.2.6. Графическое изображение логического элемента

ИСКЛЮЧАЮЩЕЕ ИЛИ

2.2.Триггеры

Триггер представляет собой логическую схему с двумя выходами, значения сигналов на которых противоположны друг другу: если на одном из выходов 1, то на другом выходе 0 и наоборот. Выходы триггера обозначают  и

и  ;

;  по значению противоположно

по значению противоположно  (

( читается как "не

читается как "не  ").

").

Триггер имеет также дополнительные входы (не менее двух): установки, обозначаемый как  (set – установка), и сброса, обозначаемый R (reset – сброс). Появление импульса на входе

(set – установка), и сброса, обозначаемый R (reset – сброс). Появление импульса на входе  переводит триггер в состояние

переводит триггер в состояние  . Такой процесс называют установкой триггера в 1, а вход – входом установки триггера в 1. В зависимости от схемных особенностей триггера установка в 1 будет происходить при подаче на этот вход либо сигнала 1, либо сигнала 0. Вход

. Такой процесс называют установкой триггера в 1, а вход – входом установки триггера в 1. В зависимости от схемных особенностей триггера установка в 1 будет происходить при подаче на этот вход либо сигнала 1, либо сигнала 0. Вход  используют для перевода триггера в состояние

используют для перевода триггера в состояние  . Этот процесс называется установкой триггера в 0, или сбросом. Соответствующий вход называют входом установки триггера в 0, или входом сброса. Такой триггер называется

. Этот процесс называется установкой триггера в 0, или сбросом. Соответствующий вход называют входом установки триггера в 0, или входом сброса. Такой триггер называется  -триггером.

-триггером.

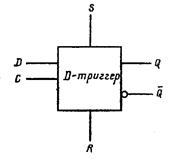

Условное графическое изображение  -триггера приведено на рис.2.7.

-триггера приведено на рис.2.7.

Рис.2.7.Условное графическое обозначение  -триггера.

-триггера.

Важнейшим из всех возможных применений триггера является использование его в качестве запоминающего устройства, называемого защелкой. Например, ячейки статической полупроводниковой памяти строятся на триггерах, причем для запоминания в ячейке памяти слова длиной 8 бит требуется 8 триггеров.

Другим примером использования триггера является его применение в качестве делителя на два частоты входных сигналов.

Кроме  -триггеров в микро-ЭВМ также используются

-триггеров в микро-ЭВМ также используются  -триггеры и двухтактные

-триггеры и двухтактные  -триггеры.

-триггеры.  -триггер используется как запоминающий элемент, двухтактный

-триггер используется как запоминающий элемент, двухтактный  -триггер используется как запоминающий элемент, так и для деления частоты на два.

-триггер используется как запоминающий элемент, так и для деления частоты на два.

Оба триггеры имеют вход синхронизации, сигналы на который подаются от генератора тактовых сигналов. Момент времени передачи информации со входа на выход триггера определяется его типом:  -триггер реагирует на появление фронта сигнала,

-триггер реагирует на появление фронта сигнала,  -триггер – на появление среза синхросигнала.

-триггер – на появление среза синхросигнала.

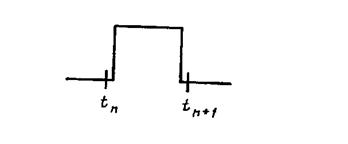

Фронт и срез сигнала показаны на рис.2.8.

Рис.2.8. Положение фронта и среза сигнала.

-триггер

-триггер

Условное графическое изображение  -триггера представлено на рис.2.9.

-триггера представлено на рис.2.9.

Рис.2.9. Условное графическое изображение  -триггера.

-триггера.

Для  -триггера обязательно наличие двух входов:

-триггера обязательно наличие двух входов:  (синхронизация) и

(синхронизация) и  (delay – задержка). Кроме этого, обычно имеются входы установки

(delay – задержка). Кроме этого, обычно имеются входы установки  и сброса

и сброса  .

.

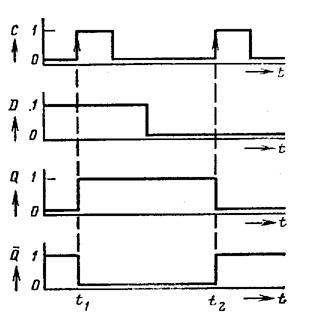

На рис.2.10 представлена временная диаграмма работы  -триггера.

-триггера.

Рис.2.10. Временные диаграммы работы  -триггера.

-триггера.

Сигнал, появляющийся на входе  , передается на выход

, передается на выход  при переключении сигнала синхронизации из нуля в единицу. Значение сигнала на выходе

при переключении сигнала синхронизации из нуля в единицу. Значение сигнала на выходе  сохраняется даже при последующих изменениях сигнала на входе

сохраняется даже при последующих изменениях сигнала на входе  , что и позволяет использовать триггер для запоминания информации. В момент времени

, что и позволяет использовать триггер для запоминания информации. В момент времени  , когда сигнал синхронизации снова становится равным единице, новое значение сигнала со входа

, когда сигнал синхронизации снова становится равным единице, новое значение сигнала со входа  передается на выход

передается на выход  и запоминается.

и запоминается.

Двухтактный  -триггер

-триггер

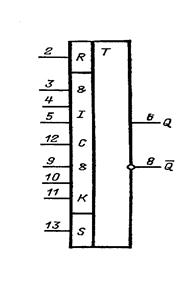

Условное графическое изображение двухтактного  -триггера приведено на рис.2.11.

-триггера приведено на рис.2.11.

Рис.2.11. Условное графическое изображение  -триггера

-триггера

Триггер имеет три входа J и три входа K, хотя в общем случае их может быть и другое число. Входы J и K предназначены для подачи на них управляющих сигналов, входы S и R используются для установки и сброса. Триггер считается готовым к работе, если S=1 и R=1 (в этом случае входы S и R не оказывают влияния на его функционирование).

Входы J и K заводятся на имеющиеся в триггере логические элементы И. В триггере выполняются операции

Момент времени, непосредственно предшествующий переключению сигнала синхронизации из нуля в единицу, обозначен  , а момент времени, непосредственно следующий за обратным переключением сигнала синхронизации, обозначен

, а момент времени, непосредственно следующий за обратным переключением сигнала синхронизации, обозначен  (рис.2.12)

(рис.2.12)

Рис.2.12. Схема моментов времени сигнала синхронизации.

В таблице 2.7 приведены сведения о работе JK-триггера, эта таблица является таблицей переходов JK-триггера.

Таблица 2.7 Таблица переходов JK-триггера

| Состояния входов и выходов | ||||

В момент

| В момент

| |||

|

|

|

| |

|

| |||

|

| |||

Если J=0 и K=0, то состояния выходов в моменты времени  и

и  одинаковы (первая строка таблицы).

одинаковы (первая строка таблицы).

Если J=0, то сигнал K=1 передается по срезу синхросигнала на выходы и переводит их в состояния  ,

,  (вторая строка).

(вторая строка).

Если J=1, то сигнал K=0 передается по срезу синхросигнала на выходы и переводит их в состояния

,

,  (третья строка).

(третья строка).

Триггер во втором и третьем случаях работает как запоминающий элемент.

Если J=1 и K=1, то состояния выходов изменяются на противоположные после окончания действия синхросигнала, то есть  ; другими словами, состояние выхода

; другими словами, состояние выхода  в момент времени

в момент времени  и

и  противоположны – выход

противоположны – выход  переключается. В этом режиме триггер работает как схема деления частоты входного синхросигнала на два, если на входах J и K присутствуют единичные сигналы.

переключается. В этом режиме триггер работает как схема деления частоты входного синхросигнала на два, если на входах J и K присутствуют единичные сигналы.

Регистры.

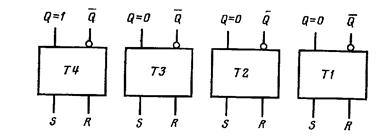

Регистры предназначены для запоминания двоичных чисел. Регистры представляют собой совокупность триггеров, предназначенную для хранения двоичного числа определенной длины. Так как триггер может находиться в двух состояниях, он способен хранить двоичные значения 0 и 1. Если же требуется запомнить двоичное число, составленное из некоторого набора нулей и единиц, то потребуется и соответствующее число триггеров. Для запоминания 8-разрядного числа нужно восемь триггеров: по одному триггеру на каждый бит. На рис.2.13 представлен регистр, способный хранить 4-битные слова, причем триггер Т4 используется для запоминания разряда с наибольшим весом. Так как данные регистр может хранить слова с длиной не более 4 бит. В нем могут быть записаны десятичные числа от 0 до 15, двоичное представление которых требует как раз не более четырех разрядов.

Рис.2.13. Четырехразрядный параллельный регистр.

Установку триггеров регистра в состояния 0 или 1 в соответствии со значениями разрядов входного слова называют приемом информации в регистр. Прием слова в регистр можно выполнить, подавая соответствующие сигналы на входы установки и сброса триггеров.

Микропроцессор в основном состоит из таких регистров, которые обрабатывают слова длиной 8 бит.

Сдвигающие регистры

По степени значимости для ЭВМ сдвигающие регистры уступают только счетчикам. Сдвигающий регистр – это регистр, в котором можно производить сдвиг слова на требуемое число разрядов.

В сдвигающем регистре информация, хранящаяся в триггерах, сдвигается вправо или влево при появлении сигнала синхронизации. Кроме этого, сдвигающие регистры используются для выполнения операций умножения и деления.

В зависимости от способа приема информации сдвигающие регистры можно подразделить на регистры с последовательным

|

|

|

|

|

Дата добавления: 2014-10-22; Просмотров: 474; Нарушение авторских прав?; Мы поможем в написании вашей работы!