КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Регистры

|

|

|

|

Регистр — это узел, предназначенный для приема, временного хранения и выдачи n-разрядного слова, а также выполнения над словами некоторых логических преобразований, например, сдвиг кода числа на определенное число разрядов влево или вправо; преобразования последовательного кода в параллельный и наоборот.

Регистр представляет собой упорядоченную совокупность триггеров со схемой управления входными и выходными сигналами. Разрядность регистров соответствует количеству используемых в нем триггеров.

По способу приема и передачи информации различают параллельные, последовательные и последовательно-параллельные регистры.

Параллельные регистры или регистры памяти применяются для ввода, хранения и вывода двоичной информации в параллельном коде.

В качестве разрядов регистра памяти используются синхронные D-триггеры, если информация поступает в виде однофазных сигналов. Если информация поступает в виде парафазных сигналов, то используется RS-триггер.

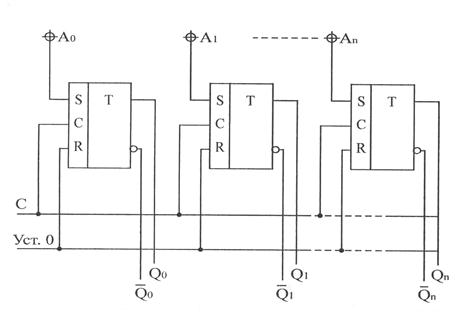

Функциональная схема регистра с параллельным приемом и выдачей информации

Предварительно перед установкой кода на все разряды регистра подается сигнал сброса (уст. 0).

Записанный в регистр код двоичного слова может храниться до тех пор, пока регистр не будет установлен в нулевое состояние сигналом «установка 0».

Ввод новой информации на входы А происходит при поступлении синхросигналов на вход С.

Последовательные или сдвиговые регистры — это регистры, выполняющие сдвиг двоичной информации вправо или влево в зависимости от управляющих сигналов.

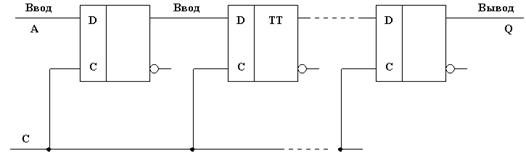

Функциональная схема регистра сдвига на D-триггерах

В регистре с последовательным приемом и выдачей информации первый разряд вводимого числа А0 подается на вход одного, крайнего слева, разряда регистра и вводится в него при поступлении первого синхроимпульса.

При поступлении следующего синхроимпульса значении А0 вводится в следующий разряд.

Таким образом производится последовательный сдвиг поступающей на вход информации на один разряд вправо в каждом такте синхросигналов. После поступления n синхросигналов весь регистр оказывается заполненным разрядами числа А и первый разряд числа А0 появляется на выходе Q0 регистра.

Сдвиговые регистры могут быть реверсивными, то есть выполнять сдвиг в любом направлении.

Сдвиг числа влево на один разряд соответствует его умножению на 2. Сдвиг числа вправо на один разряд соответствует его делению на 2, поэтому регистры сдвига используются для построения умножителей и делителей.

Сдвигающие регистры с цепями приема двоичной информации в последовательном коде и выдачи — в параллельном коде называются последовательно-параллельными регистрами, а также преобразователями последовательного двоичного кода в параллельный двоичный код.

Сдвигающие регистры с цепями приема двоичной информации в параллельном коде и выдачи — в последовательном коде называются параллельно-последовательными регистрами или преобразователями параллельного двоичного кода в последовательный двоичный код.

5.3.3 Счётчики

Счётчик представляет собой устройство, предназначенное для подсчёта числа сигналов, поступающих на его вход и фиксации этого числа в виде двоичного кода, хранящегося на выходах триггеров.

Счётчики различаются назначением, типом, количеством используемых триггеров, режимами работы, организацией связей между триггерами счётчика и другими особенностями его структуры.

Основными параметрами счётчика являются:

максимальное быстродействие, т.е. величина, равная числу сигналов фиксируемых счетчиком в единицу времени;

модуль счета — Кс — максимальное число импульсов, которое может быть сосчитано счетчиком. (После поступления Кс импульсов, счетчик возвращается в исходное состояние).

Счетчики могут быть синхронными и асинхронными.

Счетчики могут быть суммирующими и вычитающими, а также реверсивными (то есть и суммирующими и вычитающими).

По способу организации цепей переноса счетчики бывают с последовательным переносом и параллельным переносом сигнала.

Счетчики с последовательным переносом сигнала

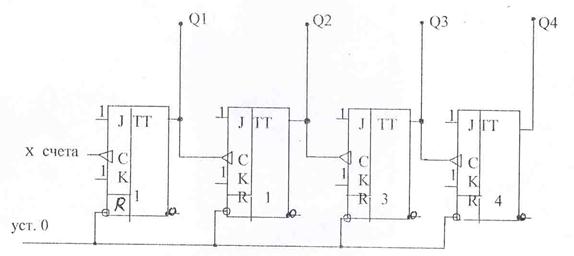

Схема синхронного двоичного четырехразрядного суммирующего счётчика на JK-триггерах с последовательным переносом сигнала

В этих счётчиках каждый последующий триггер запускается от информационного выхода Qi предыдущего триггера, а счётный сигнал поступает на вход триггера первого разряда.

| Xсч. | Q4 | Q3 | Q2 | Q1 |

Рассмотрим работу счётчика, полагая, что в исходном состоянии в нем записан код 0000.

В счётчике выход каждого предыдущего триггера соединен с входом синхронизации (Ci) последующего триггера. На входы J и K подаются сигнал 1.

Первый входной сигнал Xсч. установит триггер Т1 счётчика в состояние 1, все остальные триггеры останутся в состоянии 0.

Второй входной сигнал установит триггер Т1 в состояние 0; третий — опять в 1 и т.д.

Входными сигналами триггера Т2 будут уже сигналы, снимаемые с прямого выхода триггера Т1.

Таким образом, первый раз в состояние 1 триггер Т2 установится только после того, как на выходе триггера Т1 пройдет первый сигнал, а в состояние 0 — после того, как пройдет второй сигнал и так далее.

Входными сигналами триггера Т3 будут уже сигналы, снимаемые с прямого выхода триггера Т2 и так далее.

После того, как на вход счетчика будет подана серия сигналов, например, пройдет пять входных импульсов, на выходе триггеров счетчика установится двоичный код 0101, что и будет соответствовать цифре 510.

Так подсчитывается количество импульсов поданных на вход счетчика. Счетчик имеет цепь установки в состояние 0.

Недостаток счетчика с последовательным переносом сигнала — с ростом разрядности счетчика возрастает задержка поступления сигнала на вход С следующего разряда.

Таким образом, быстродействие его не велико, но аппаратно он прост в исполнении.

Счётчик с параллельным переносом сигнала

Счётчик с параллельным переносом сигнала характеризуется одновременным формированием импульсов переноса, поступающих на все разряды счётчика, начиная со второго.

Такие счётчики относятся к разряду быстродействующих, отличительной особенностью схемы является то, что сигналы с выходов i-х разрядов поступают на информационные входы J и K триггеров (i+1)-х разрядов.

Формирование сигналов в цепи параллельного переноса происходит одновременно во всех триггерах счетчика и заканчивается к приходу следующего очередного счетного сигнала, то есть все триггеры такого счетчика переключаются одновременно.

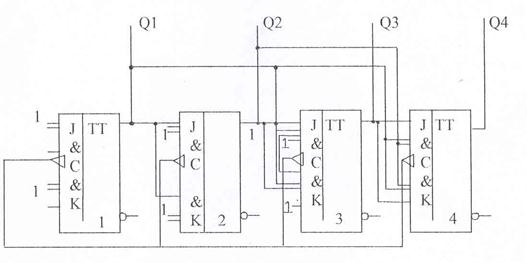

Схема четырехразрядного счетчика на JK-триггерах с параллельным переносом

Из схемы видно, что с возрастанием порядкового номера триггера увеличивается число входов в элементах И JK-триггеров.

Так как количество входов J и K и нагрузочная способность триггеров ограничены, то и разрядность счетчика с параллельным переносом невелика и равна обычно четырем.

Количество просчитанных импульсов можно определить по двоичному коду, записанному в триггеры счетчика.

Недостаток — сложная структурная (аппаратная) организация такого счетчика.

При числе разрядов счетчика большем максимального числа входов J и K, счетчики разбиваются на группы и внутри каждой группы строятся цепи параллельного переноса.

Глава 6 Память ЭВМ

|

|

|

|

|

Дата добавления: 2014-11-09; Просмотров: 1151; Нарушение авторских прав?; Мы поможем в написании вашей работы!