КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Обобщенная структура процессора

|

|

|

|

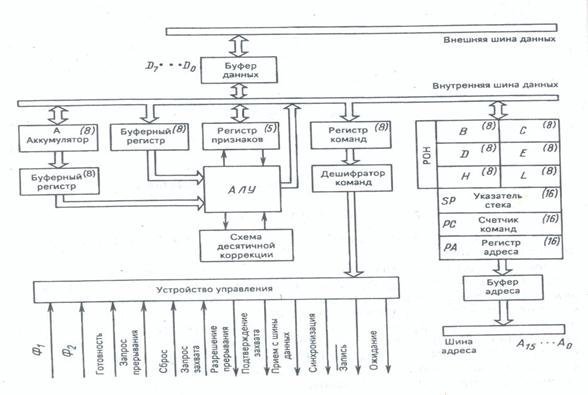

Обобщенную структуру процессора рассмотрим на примере типового 8-разрядного процессора, схема которого приведена на рисунке. МП серии КР580 один из простейших процессоров. Он является аналогом МП фирмы Intel 8080.

Он представляет собой 8-разрядный МП с тактовой частотой 2,5 МГц, выполненный по Моп-технологии. Потребляемая мощность 1,5 Вт, диапазон рабочих температур –100/+700С. микросхема имеет 40 выводов. Быстродействие 625000 операций в секунду.

Регистры данных. Для хранения операндов предусмотрено семь 8-разрядных регистров. Регистр A (аккумулятор) предназначен для обмена информацией с внешними устройствами (т.е. содержимое этого регистра может быть выдано либо на вход МП, либо со входа МП в него может быть принято от внешнего устройства число), при выполнении арифметических, логических операций и операций сдвига он служит источником операнда, в него помещается результат выполненной операции.

Шесть других регистров, обозначенных B, C, D, E, H, L образуют блок регистров общего назначения (РОН). В них могут храниться и данные и адреса. Эти регистры могут использоваться как одиночные 8-разрядные регистры. Если необходимо хранить 16-разрядные двоичные числа, регистры объединяются в пары BC, DE, HL.

Рис.2.1.1. Структура процессора 8080

Указатели стека. Регистр SP (16-разрядный) служит для адресации стека. Он содержит адрес входа в стек. Стек использует ячейки со старшими адресами (в то время как в ОЗУ команды размещаются в ячейках с младшими, последовательно нарастающими адресами). В стеке по мере заполнения занимаются ячейки с последовательно убывающими адресами.

При чтении из стека производится выборка содержимого ячейки по адресу, хранящемуся в SP, при записи в стек вводимое число помещается в ячейку с адресом, на единицу меньше содержимого SP, одновременно с записью и чтением изменяется содержимое SP: при записи уменьшается, а при чтении увеличивается на 1.

Счетчик команд. Регистр РС (16-разрядный) предназначен для хранения адреса команды; после выборки из оперативной памяти текущей команды содержимое счетчика увеличивается на 1, и таким образом формируется адрес очередной команды (при отсутствии переходов).

Регистр адреса. Регистр РА (16-разрядный). При выдаче адресов содержимое регистров РОН передается в РА, из которого через буферы адреса адрес поступает на 16-разрядную шину адреса, с которой он может быть принят в оперативную память. Число кодовых комбинаций 16-разрядного адреса равно 216, каждая из этих кодовых комбинаций может определить адрес (номер) одной из ячеек оперативной памяти. Таким образом, обеспечивается возможность обращения к памяти, содержащей до 216=26*26=64 Кбайт.

Арифметико-логическое устройство (АЛУ). В 8-разрядном АЛУ предусмотрена возможность выполнения четырех арифметических операций: сложение с передачей переноса в младший разряд и без учета этого переноса вычитание с передачей заема в младший разряд и без него; четырех видов логических операций (И, ИЛИ, неравнозначности сравнения), а также четырех видов циклического сдвига.

При реализации арифметических и логических операций одним из операндов служит содержимое аккумулятора, результат операции помещается в аккумулятор. Циклический сдвиг выполняется только над содержимым аккумулятора.

Предусмотрена возможность выполнения арифметических операций над десятичными числами, представленными в коде 8421. При хранении десятичного числа разряды регистра делятся на две группы, по четыре разряда, и в каждой группе разрядов хранится одна десятичная цифра, представленная в коде 8421 (название кода составлено из новых коэффициентов разрядов двоичного числа). Таким образом, в регистре можно хранить 2-разрядное десятичное число. Кроме того, в АЛУ имеется схема десятичной коррекции (СДК)

Регистр признаков (РП). Этот 5-разрядный регистр предназначен для хранения определенных признаков, выявляемых в числе, которое представляет результат выполнения некоторых операций. Пять триггеров этого регистра имеют следующее назначение:

- триггер переноса Тс при выполнении арифметических операций устанавливается в состояние, соответствующее переносу из старшего разряда числа, при выполнении операции сдвига – в состояние, соответствующее содержимому выдвигаемого из аккумулятора разряда;

- триггер нуля Тz устанавливается в состояние 1, если результат операции равен 0;

- триггер знака Тs устанавливается в состояние, соответствующее значению старшего разряда результата операции АЛУ;

- триггер четности Тр устанавливается в состояние 1, если число единиц в разрядах результата четное;

- триггер дополнительного переноса Тv хранит возникающий при операции перенос из 4-го разряда.

Блок управления состоит из регистра команд, куда принимается первый байт команды, и устройства управления, формирующего управляющие сигналы, под действием которых выполняются микрооперации в отдельных узлах. УУ содержит управляющую память, в которой хранятся микропрограммы отдельных операций.

Регистр команд – однобайтовый регистр, в котором хранится код выполняемой команды. Этот регистр непосредственно пользователю недоступен. Это означает, что не существует команды, которая явным образом могла бы изменить его содержимое. После выполнения очередной команды в регистр команд автоматически записывается код следующей команды из ячейки памяти, адрес которой содержится в счетчике команд.

Задача УУ - формировать управляющие сигналы, под действием которых в АЛУ будут производиться микрооперации.

В данном процессоре реализован принцип микропрограммного управления. Это означает, что каждая команда реализуется как некоторая последовательность микрокоманд, которые хранятся в управляющей памяти, выполненной на программируемой логической матрице. Считываемая из основной памяти команда (ее код операции) поступает в регистр команд, где хранится в течение времени выполнения команды. По результатам дешифрования кода команды происходит формирование в управляющей памяти последовательности микрокоманд, т.е. микропрограммы. Путем последовательного считывания микропрограммы в АЛУ реализуется требуемая операция.

Буферы обеспечивают связь МП с внешними шинами данных и адреса.

|

|

|

|

|

Дата добавления: 2014-12-16; Просмотров: 3503; Нарушение авторских прав?; Мы поможем в написании вашей работы!