КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Функциональные свойства и реализация триггеров

|

|

|

|

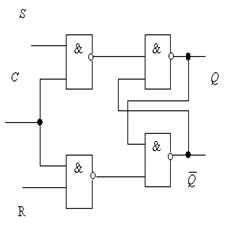

· RS-триггеры.

RS-триггер получил свое название от английских обозначений своих информационных входов. Один вход называется входом установки S (set), а другой входом сброса R (reset). При подаче сигнала на вход установки S триггер переходит в состояние «1» (выход  ). При наличии сигнала на входе сброса R, триггер устанавливается в состояние «0».При отсутствии сигналов на информационных входах триггер сохраняет свое предыдущее состояние.

). При наличии сигнала на входе сброса R, триггер устанавливается в состояние «0».При отсутствии сигналов на информационных входах триггер сохраняет свое предыдущее состояние.

Простейший RS-триггер может быть построен на логических элементах, за счет введения обратных связей. Именно введение обратных связей, позволяет «удерживать» сигнал на выходе устройства после окончания воздействия входного сигнала, т.е. придает устройству способность запоминать. Реализация нетактируемого RS-триггера на элементах И - НЕ и временная диаграмма его работы показаны на рис. 6.

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Рисунок 6

Ниже представлена реализация нетактируемого RS-триггера на элементах

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Рисунок 7

ИЛИ-НЕ, временная диаграмма его работы и условное обозначение приведены на рис. 7.

Каждая реализация представляют собой два элемента соответствующего типа замкнутые в кольцо. Если отсутствуют внешние воздействия, та на выходе одного элемента устанавливается логический уровень «1», а на выходе второго – уровень «0». Опрокидывание триггера на элементах И-НЕ производится уровнем «0», поступающем на какой либо вход, Триггер на элементах ИЛИ-НЕ опрокидывается при воздействии уровня «1». Таблица истинности для триггера на элементах И-НЕ следующая.

| R | S |

|

|

| ? | ? | ||

|

|

В таблице исходное (предыдущее) состояние триггера обозначено как  , а новое как

, а новое как  , символ «?» указывает на то, что состояние триггера не может быть определено. Временная диаграмма работы этого триггера приведена на рис. 3. Отметим, что данный триггер изменяет свое состояние при логическом «0» на одном из своих входах. Для того чтобы подчеркнуть этот факт, входы такого триггера называют инверсными. В дальнейшем будем рассматривать триггеры, построенные на элементах

, символ «?» указывает на то, что состояние триггера не может быть определено. Временная диаграмма работы этого триггера приведена на рис. 3. Отметим, что данный триггер изменяет свое состояние при логическом «0» на одном из своих входах. Для того чтобы подчеркнуть этот факт, входы такого триггера называют инверсными. В дальнейшем будем рассматривать триггеры, построенные на элементах

И-НЕ.

Тактируемый RS-триггер, получается из нетактируемого введением дополнительных элементов, которые разрешают прохождение тактового входного импульсного сигнала C (clock), на тот или иной вход исходного нетактируемого триггера. Схема такого триггера и его временная диаграмма и условное обозначение показаны на рис. 8.

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Рисунок 8

Таблица истинности следующая.

| R | S | C |

|

|

|

| |||

|

| |||

|

| |||

|

| |||

|

| |||

| ? | ? |

На тактовый вход C постоянно подается уровень «0», поэтому на выходах двух входных ключей И-НЕ присутствуют уровни «1», поступающие на входы элементарного триггера. Таким образом, независимо от сигналов на входах S и R триггер находится в режиме хранения информации. Если на вход C кратковременно подать уровень «1», то элементарный триггер установится в состояние, зависящее от сигналов на входах S и R. Состояние триггера при наличии на обоих входах S и R логической «1» единицы не определено. Это ограничение логично, т.к. бессмысленно требовать от триггера одновременного сброса и установки. Рассмотренный триггер тактируется уровнем, т.е. он изменяет состояние и переходит в режим хранения в зависимости уровня тактового сигнала. Отметим, что данный триггер изменяет свое состояние при наличии логической «1» на каком либо информационном входе. Поэтому информационные входы такого триггера называют прямыми.

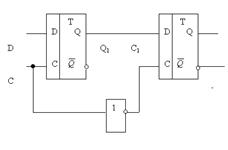

· D-триггеры.

D-триггер или триггер задержки (delay) устанавливается в состояние, соответствующее логическому уровню на информационном входе D, если есть разрешающий сигнал на тактовом входе C. Таким образом, все D-триггеры являются тактируемыми. D-триггер описывается следующим соотношением между входом и выходом  . Индексы

. Индексы  и

и  подчеркивают, что выходной сигнал

подчеркивают, что выходной сигнал  изменяется не сразу после изменения входного сигнала

изменяется не сразу после изменения входного сигнала  , а только с приходом тактового сигнала.

, а только с приходом тактового сигнала.

Тактируемый уровнем D-триггер, временная диаграмма его работы и обозначение показаны на рис. 9. Он построен на базе тактируемого уровнем RS-триггера. При этом вход D подключается напрямую к входу S, а на вход R он же подается через дополнительный инвертор. Вход C исходного триггера остается тактовым входом реализуемого D-триггера. При таком включении сигналы на входах S и R базового триггера оказываются взаимно инвертированными и, следовательно, исключается возможность

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Рисунок 9

возникновения запрещенного состояния, а вместо двух информационных входов S и R образуется один – D, уровень которого и определяет следующее состояние триггера.

Тактируемый фронтом D-триггер строится по двухступенчатой схеме. Построение тактируемого импульсом триггера по такой схеме, а не при помощи введения обратных связей, обусловлено тем, что сигнал обратной связи может измениться до окончания тактирующего импульса. Поэтому может произойти дополнительное, незапланированное переключение триггера. Двухступенчатая схема называется master-slave (хозяин – раб), подчеркивая тем самым то, что триггер состоит из двух частей. Одна часть ведущая (master), как бы заставляет другую ведомую (slave) повторять свои действия.

Схема тактируемого фронтом D-триггера приведена на рис. 10. Она состоит из двух тактируемых потенциалом D-триггеров. Вход D второго (slave) триггера подключен к выходу Q первого (master) триггера. Тактовый вход схемы подключается прямо к тактовому входу первого триггера

| |||

| |||

Рисунок 10

и инверсно к тактовому входу второго.

Исходно на тактовом входе ведущего триггера присутствует уровень логического «0», а на тактовом входе ведомого – уровень логической «1». При этом ведущий триггер находится в режиме хранения предыдущего состояния, а ведомый в режиме записи приложенного к его входу D сигнала с выхода ведущего, т.е. он также находится в предыдущем состоянии. При приходе тактового импульса - на входе C ведущего оказывается уро-

|

Рисунок 11

вень «1», а на входе C ведомого – уровень «0». Тогда ведомый переходит в

режим хранения и его состояние не изменяется, а ведущий опрокидывается в состояние, соответствующее уровню на своем входе D. Когда тактовый импульс заканчивается и становится логическим нулем, ведущий опять переходит в режим хранения уже измененного состояния, а ведущий в режим его записи. В этом состоянии триггер находится до прихода следующего тактового импульса. Таким образом, можно считать, что изменение состояния всего двухступенчатого триггера происходит по заднему фронту тактового импульса. Временная диаграмма работы тактируемого задним фронтом D-триггера показана на рис. 11.

Отметим, что аналогичным образом можно сконструировать и RS- триггер, тактируемый фронтом. Только в качестве ведущего и ведомого элементов используются тактируемые уровнем RS-триггеры. Схема триггера показана на рис. 12.

| |||

| |||

Рисунок 12

· T-триггеры.

Т-триггер или счетный триггер характеризуется отсутствием информационных входов и наличием только тактового входа. По каждому тактовому импульсу он устанавливается в состояние противоположное тому, в котором находился до его прихода. T-триггер описывается следующим выражением, связывающим его текущее и предыдущее состояния  .

.

В схеме на рис. 13, инверсный выход  тактируемого фронтом D-триггера соединен с его же информационным входом

тактируемого фронтом D-триггера соединен с его же информационным входом  . Поэтому после первого тактового импульса триггер переходит из состояния

. Поэтому после первого тактового импульса триггер переходит из состояния  в состояние

в состояние  . После второго импульс триггер возвращается в исходное состояние. Этот процесс происходит и дальше при поступлении следующих тактовых импульсов.

. После второго импульс триггер возвращается в исходное состояние. Этот процесс происходит и дальше при поступлении следующих тактовых импульсов.

| |||

|

Рисунок 13

Иными словами в ответ на два импульса на входе появляется один импульс на выходе (рис. 13). Если тактовые импульсы являются периодическими с частотой повторения  , то на выходе также имеем периодические импульсы, но с частотой повторения

, то на выходе также имеем периодические импульсы, но с частотой повторения  . Поэтому счетный триггер можно рассматривать как делитель частоты с коэффициентом деления 2. Такой режим работы триггера, как и образовавшийся при этом вход называют счетным. Счетный триггер можно получить, используя и другие триггеры.

. Поэтому счетный триггер можно рассматривать как делитель частоты с коэффициентом деления 2. Такой режим работы триггера, как и образовавшийся при этом вход называют счетным. Счетный триггер можно получить, используя и другие триггеры.

|

Рисунок 14

На рис. 14 показан счетный триггер на базе тактируемого фронтом RS-триггера. В нем выход  соединен с входом S, а выход

соединен с входом S, а выход  - с входом R.

- с входом R.

Вход С, при этом, становится счетным.

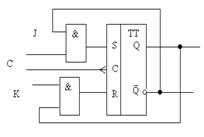

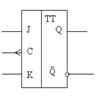

· JK-триггеры.

JK-триггер это наиболее универсальный триггер, из всех рассмотренных выше. Он имеет, как счетный вход, так и информационные входы, управляющие счетным. Аббревиатура JK, используемая для обозначения информационных входов происходит от английских слов Jump – прыжок и Keep – держать.

Структура JK-триггера (рис. 15) напоминает счетный триггер на базе тактируемого фронтом RS-триггера. Однако обратные связи заводятся на входы S и R через дополнительные двухвходовые схемы И. На другие входы этих схем И подаются информационные сигналы J и K.

| |||

| |||

Рисунок 15

Если J=1 и K=1, то триггер полностью эквивалентен схеме на рис. 15 и работает как счетный. В противном случае он работает как тактируемый фронтом триггер с установочными входами. Таблица истинности JK-триггера приведена ниже.

| J | K |

|

| ||

|

Глава 3. Основные компоненты компьютера

|

|

|

|

|

Дата добавления: 2014-11-29; Просмотров: 1459; Нарушение авторских прав?; Мы поможем в написании вашей работы!