КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Лекция 9. Основные элементы цифровой техники

|

|

|

|

Цель лекции: изучить основные схемы цифровой техники

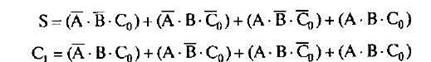

9.1 Сумматор

Одной из первых функций, реализованных в ИС помимо обычных логических функций, было сложение. В таблице истинности, показанной на рисунке 9.1, приведены значения бита суммы S и флага переноса Q, образующихся при сложении двух битов А и В и бита переноса из предыдущего разряда Со. Например, из 6-й строки таблицы следует, что при сложении двух единиц и 0-го переноса сумма будет равна 0, а перенос равен 1 (1+1+0=10). Для реализации этой строки таблицы нам нужно распознать комбинацию битов 110, описываемую выражением А*В*Со. Эту операцию выполняет 6-й элемент схемы. Таким образом, для сумматора мы просто объединяем по ИЛИ все возможные комбинации входных переменных:

Применяя такую схему для каждого разряда и подключая при этом выход переноса разряда с номером К - 1 к входу переноса разряда с номером К, мы сможем выполнять сложение любых N-битных чисел.

Рисунок 9.1 – Сложение чисел

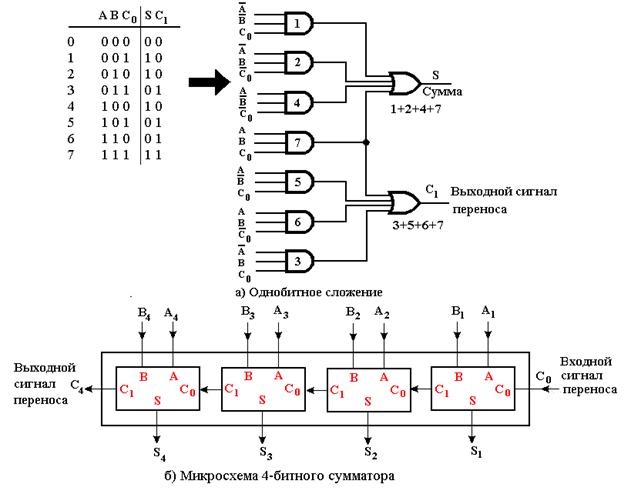

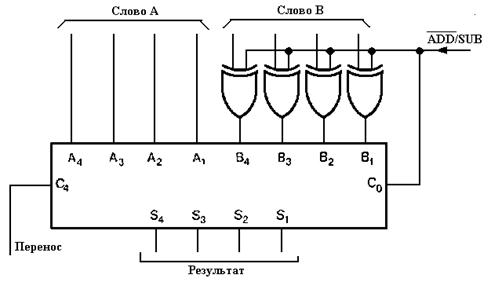

Разумеется, сумматоры можно использовать и для вычитания, если перевести операнды в дополнительный код.

Рисунок 9.2 - Программируемый сумматор/вычитатель

Схему сумматора/вычитателя можно реализовать при помощи набора логических элементов Исключающее-ИЛИ, выступающих в роли программируемых инверторов. Вход выбора режима ADD/SUB, управляющий этими инверторами на рисунке, 9.2, подключен также к входу переноса, что вызывает добавление единицы в режиме вычитания.

9.2 Арифметико-логическое устройство

Расширяя набор аргументов, мы придем к арифметико-логическому устройству (АЛУ). АЛУ представляет собой схему, выполняющую определенный набор арифметических и логических операций над входными данными в соответствии со значением на входах выбора режима.

Таблица 9.1 - АЛУ

| S2 S1 S0 | Операция |

| 0 0 0 | Сброс (F=0000) |

| 0 0 1 | Вычитание В-А |

| 0 1 0 | Вычитание А-В |

| 0 1 1 | Сложение А+В |

| 1 0 0 | Искл. ИЛИ АÅВ |

| 1 0 1 | ИЛИ А+В |

| 1 1 0 | И А*В |

| 1 0 1 | Установка (F=1111) |

Микросхема, таблица истинности которой приведена в таблице 9.1, выполняет 8 операций над двумя 4-битными числами. Выполняемая операция задается тремя битами выбора режима S0S1S2. Кроме сложения и вычитания, это АЛУ выполняет также операции OR, AND и XOR. Микросхема формирует также признак переполнения дополнительного кода.

9.3 Бистабильные схемы

Все рассмотренные ранее схемы, относятся к классу комбинационных схем. Значение их выходов зависит только от состояния входов в данный момент времени и не зависит от предыдущих событий. Такие же логические схемы, как защелки, счетчики, регистры и оперативная память (допускающая как чтение, так и запись), относятся к классу последовательных схем. Состояние выходов таких схем зависит не только от текущего состояния входов, но и от предыстории сигналов на входах.

Возьмем обыкновенную кнопку, она не обладает памятью. Рассмотрим выключатель. Вы нажимаете на выключатель, и свет загорается. Чтобы выключить свет, вы должны перевести выключатель в выключенное состояние. Ключи такого типа называются бистабильными Каждый такой ключ ведет себя как 1-битная ячейка памяти.

В микросхемах оперативной памяти каждая бистабильная ячейка формируется с помощью двух перекрестно включенных транзисторов. Рассмотрим два логических элемента ИЛИ-НЕ, объединенных перекрестными обратными связями (рисунок 9.3). Вспомним, что при появлении логической 1 на каком-либо входе элемента ИЛИ-НЕ на его выходе появляется логический нуль. Вооружившись этим знанием, проанализируем схему:

- если на вход S подать 1, то выход Q переключится в 0. На обоих входах верхнего элемента появится 0, что приведет к появлению 1 на выходе Q. Если, теперь на входе S снова появится 0, то нижний элемент останется в 0 (поскольку на входе обратной связи с вывода Q присутствует 1) и состояние выхода верхнего элемента также не изменится. Таким образом, триггер устанавливается при подаче положительного импульса на вход S.

- если на вход R подать 1, то выход Q переключится в 0. На обоих входах нижнего элемента появится 0, что приведет к появлению 1 на выходе Q. Если теперь на входе R снова появится 0, то верхний элемент останется в 0 (поскольку на входе обратной связи с вывода Q присутствует 1) и состояние выхода нижнего элемента также не изменится. Таким образом, триггер сбрасывается при подаче положительного импульса на вход R.

При нормальном функционировании (предполагается, что оба входа не могут быть активными в один и тот же момент времени) оба выхода дополняют друг друга, что отражено на условном графическом изображении триггера (рисунок 9.3).

9.4 Триггеры и регистры

Существует много различных реализаций бистабильных ячеек. Например, замена элементов ИЛИ-НЕ на элементы И-НЕ приведет к образованию RS-триггера, в котором активным входным сигналом является логический 0. Дальнейшим развитием RS-триггера является D-защелка. В этом элементе выходной сигнал (Q) повторяет входной (D),если на входе управления С присутствует активный уровень (в данном случае — высокий), и сохраняет предыдущее значение при неактивном уровне на входе управления. Таким образом, D-защелку можно рассматривать как 1-битную ячейку памяти, запоминающую значение, которое присутствует на ее входе на момент завершения импульса управления.

Рисунок 9.3 - RS триггер

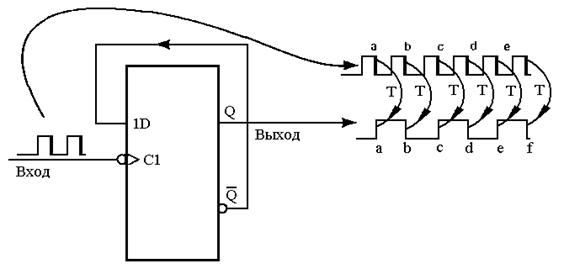

На рисунке 9.4 взаимное влияние входов D и С обозначается символами «C1» и «1D». Префикс «1» у D указывает на то, что этот вход зависит от любого сигнала в обозначении которого имеется суффикс «1», в данном случае от входа С то есть фиксация значения 1D происходит по сигналу С1.

D-триггер тоже представляет собой 1-битную ячейку памяти. Однако в нем данные передаются на выход только по активному фронту сигнала на управляющем (тактовом) входе. Наборы D-триггеров обычно называются регистрами, т.е. устройствами памяти, хранящими одно слово данных.

Рассмотрим D-триггер, тактируемый по спадающему фронту (рисунок 9.4), инверсный выход Q которого подключен к входу 1D. По каждому спадающему фронту на входе С1 данные с входа 1D будут защелкиваться и появляться на выходе Q. Поскольку инверсный сигнал этого выхода подастся обратно на вход, то в следующий раз триггер переключится в противоположное состояние. Это периодическое переключение между двумя состояниями помечено на временной диаграмме символом «Т». В результате при подаче на вход триггера сигнала некоторой частоты на его выходе будет сформирована последовательность импульсов, частота которых в 2 раза ниже. Такой Т-триггер называют триггером счетного типа или делителем на два.

Рисунок 9.4 - Т-триггер

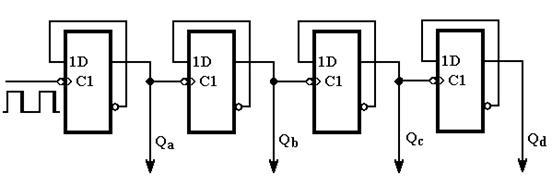

Разумеется, Т-триггеры тоже можно каскадировать, как показано на рисунке 9.5. В данном случае 4 триггера с запуском по спадающему фронту соединены таким образом, чтобы выход N-го разряда управлял тактовым входом разряда N + 1. Соответственно, если частота сигнала на входе С равна 8 МГц, то на выходе Qa будет прямоугольный сигнал частотой 4 МГц, на выходе Qb — 2 MГц, на Qc — 1 MГц и на Qd — 0,5 МГц.

Рисунок 9.5 – Каскадирование Т-триггеров

|

|

|

|

|

Дата добавления: 2014-12-07; Просмотров: 840; Нарушение авторских прав?; Мы поможем в написании вашей работы!