КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Аналого-цифровые преобразователи

|

|

|

|

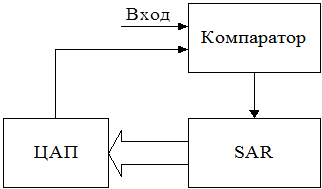

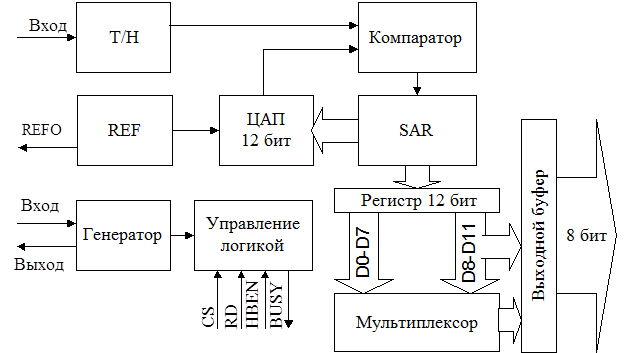

Самыми распространенными аналого-цифровыми преобразователями являются АЦП, работающие по принципу поразрядного уравновешивания. Структура преобразования представлена на рис. 7.16. Входной сигнал поступает на один из входов компаратора (сравнивающего устройства), а выходное напряжение внутреннего ЦАП – на второй. Разрядность ЦАП соответствует разряд- Рис. 7.16

Самыми распространенными аналого-цифровыми преобразователями являются АЦП, работающие по принципу поразрядного уравновешивания. Структура преобразования представлена на рис. 7.16. Входной сигнал поступает на один из входов компаратора (сравнивающего устройства), а выходное напряжение внутреннего ЦАП – на второй. Разрядность ЦАП соответствует разряд- Рис. 7.16

ности реализуемого АЦП. Если опорное напряжение ЦАП принять за U ref, то в начале преобразования специальный регистр управления (SAR –Successive Approximation Register) включает старший бит ЦАП, формируя напряжение U ref/2. Компаратор сравнивает это напряжение с входным. Если входное напряжение больше, бит остается включенным, а если нет – выключается. Далее включается следующий бит, добавляющий к выходному напряжению сигнал U ref/4, и реализуется алгоритм, аналогичный предыдущему. Таким образом, через число тактов, равное разрядности АЦП, в регистре управления будет сформирован код, пропорциональный входному напряжению и U ref.

|

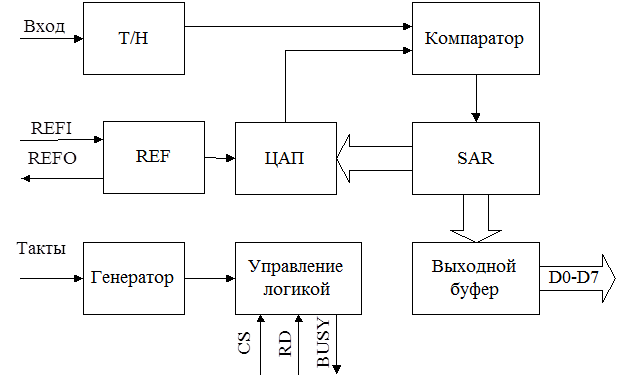

Рассмотрим микросхему 8-разрядного АЦП, имеющего параллельный интерфейс, внутренний источник опорного напряжения (REF) и тактовый генератор. Структура АЦП приведена на рис. 7.17.

Рис. 7.17

Аналоговый сигнал с входа поступает на специальное устройство выборки/хранения (T/H). Это устройство предназначено для запоминания уровня аналогового сигнала, соответствующего началу преобразования, на все время поразрядного уравновешивания. Этим исключается динамическая ошибка преобразования, связанная с изменениями входного сигнала. Запоминание обычно осуществляется на конденсаторе. До начала преобразования напряжение на конденсаторе отслеживает изменения входного сигнала. В начале преобразования конденсатор отключается от входа, запоминая последний уровень входного сигнала. Изменения сигнала на входе компаратора во время преобразования исключены.

Сигналы CS и RD управляют началом преобразования и выдачей данных из управляющего регистра на внешнюю магистраль. Во время преобразования вырабатывается специальный сигнал неготовности данных BUSY.

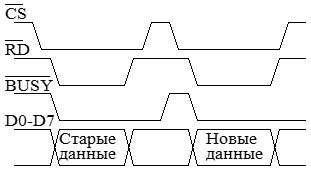

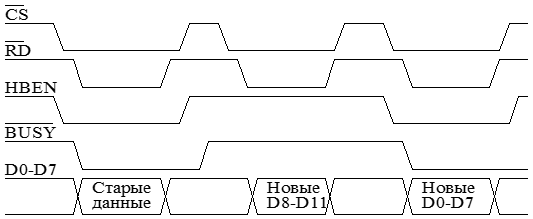

Преобразование начинается с появлением 0 на входах выборки микросхемы CS и чтения RD (рис. 7.18). АЦП выдает сигнал BUSY = 0 на все время преобразования. Поскольку сигналы CS = 0 и RD = 0, выходной буфер переходит из высокоимпедансного состояния в режим передачи данных, но выдаются данные предыдущего преобразования. Если дож- Рис. 7.18

Преобразование начинается с появлением 0 на входах выборки микросхемы CS и чтения RD (рис. 7.18). АЦП выдает сигнал BUSY = 0 на все время преобразования. Поскольку сигналы CS = 0 и RD = 0, выходной буфер переходит из высокоимпедансного состояния в режим передачи данных, но выдаются данные предыдущего преобразования. Если дож- Рис. 7.18

даться окончания преобразования, удерживая сигнал 0 на входах CS и RD, то одновременно с изменением BUSY из 0 в 1 произойдет изменение данных преобразования на новые.

|

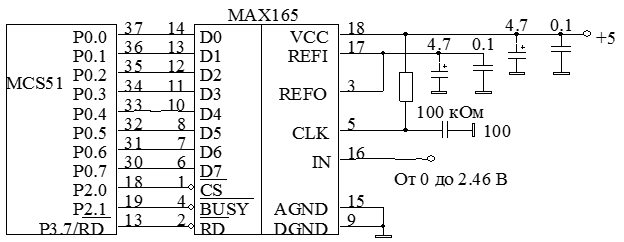

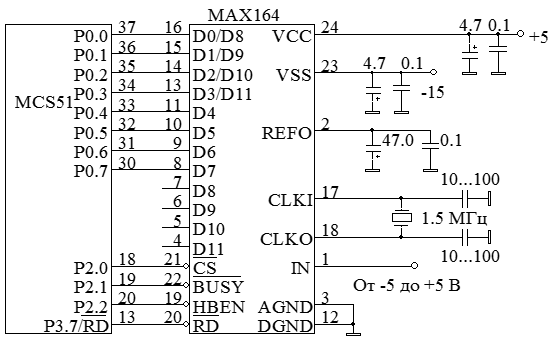

Рекомендуемая схема подключения АЦП к микроконтроллеру приведена на рис. 7.19. Используется внутренний тактовый генератор с внешней

Рис. 7.19

RC- цепочкой (вход CLK). Время преобразования нестабильно и для указанных на схеме номиналов элементов составляет от 5 до 15 мкс. При подключении к входу CLK внешнего генератора с частотой 4 МГц получим время преобразования 5 мкс.

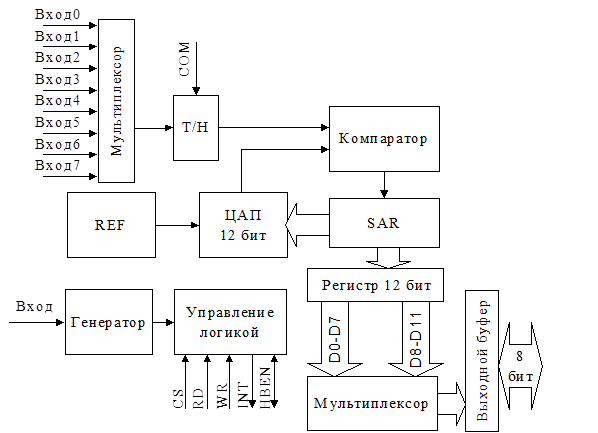

Структура 12-разрядного АЦП приведена на рис. 7.20. Микросхема МАХ164 содержит встроенный генератор, внутренний источник опорного

Структура 12-разрядного АЦП приведена на рис. 7.20. Микросхема МАХ164 содержит встроенный генератор, внутренний источник опорного

Рис. 7.20

|

напряжения и мультиплексированную шину данных. Реализована возможность подключения к 8-разрядным ОЭВМ (рис. 7.21). Мультиплексор, управ-

Рис. 7.21

ляемый сигналом HBEN, подключает к выходу 8 младших разрядов данных или 4 старших разряда в младшей тетраде (рис. 7.22).

Для питания АЦП используются напряжения +5 и –15 В, что позволяет преобразовывать двухполярные сигналы. Для смещения входного сигнала можно использовать выход источника опорного напряжения (REFO = –5 В). Синхронизацию работы узлов АЦП осуществляет внутренний генератор, выполненный на трех инверторах и ориентированный на использование внешнего кварцевого резонатора. Последний обеспечивает время преобразования порядка 8,33 мкс.

|

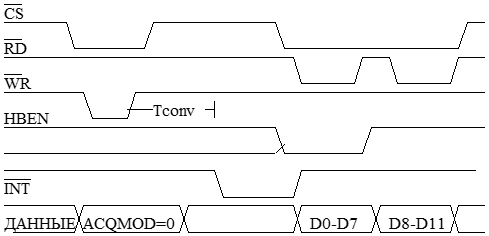

Временные диаграммы управления преобразованием представлены на рис. 7.22. По аналогии с 8-разрядным АЦП преобразование запускается при

Рис. 7.22

CS = 0 и RD = 0, обязательным условием является HBEN = 0. Только в этом случае начинает работу структура поразрядного уравновешивания и выдается сигнал BUSY = 0 на все время преобразования. Одновременно с запуском преобразования на выводы D0…D7 выдается младший байт данных от предыдущего цикла. После завершения преобразования (BUSY = 1) нужно установить HBEN = 1, при этом на выводах D0…D3 (в младшей тетраде) ОЭВМ получит данные D8…D11 нового цикла. При чтении старшего байта нового преобразования не происходит, так как HBEN = 1. После чтения старших бит нужно установить HBEN = 0. На выводах D0…D7 формируется младший байт нового цикла преобразования, одновременно производится запуск очередного цикла аналого-цифрового преобразования.

На выводах D0…D11 можно получить все разряды АЦП одновременно, удерживая нуль на входах CS, RD и HBEN до конца преобразования.

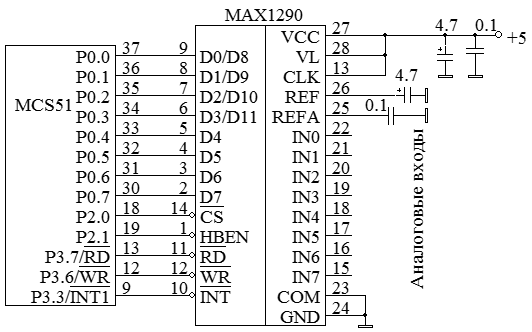

Фирма "MAXIM" разработала целую серию АЦП с параллельным и последовательным интерфейсами различной разрядности. Рассмотрим их работу на примере микросхемы MAX1290 (рис. 7.23). Двенадцатиразрядный

Рис. 7.23

АЦП снабжен 8-канальным входным аналоговым мультиплексором, внутренним генератором и источником опорного напряжения 2.5 В, имеет 8-разрядный мультиплексированный выход. Общее построение напоминает микросхему MAX164, однако имеются и отличия. Выходная шина – двунаправленная, с возможностью записи режима работы АЦП. Изменилось обозначение сигнала, формирующегося во время проведения преобразования. Теперь это сигнал прерывания микроконтроллера (INT).

АЦП может обрабатывать сигналы от 8 источников. Мультиплексор подключает к входу устройства выборки/хранения один или два аналоговых входа из восьми. В соответствии с режимом работы запоминающий конденсатор может сохранить уровень сигнала выбранного входа или разность сигналов на двух выбранных входах. Кроме того, запоминание сигнала происходит со смещением, определяемым входом COM.

Преобразователь может работать в режиме обработки двухполярного сигнала (± U ref /2), если COM = U ref /2.

|

Внутренний источник опорного напряжения +2.5 В может подстраиваться на ±100 мВ посредством вывода REFA. Кроме того, при работе с внутренним источником опорного напряжения можно использовать сигнал на выходе REF для получения необходимого смещения по входу COM. Если используется внешний источник U ref, он подключается к выводу REF, а вывод REFA должен быть подключен к источнику аналогового питания VСС. Схема подключения к ОЭВМ представлена на рис. 7.24.

Рис. 7.24

Преобразование начинается с записи в АЦП управляющего слова (табл. 7.11), содержащего режимы работы и номер подключенного входа. Внутренний генератор обеспечивает время преобразования 3.6 мкс, внешний может иметь частоту от 0.1 до 7.6 МГц. В "спящем" режиме все функции АЦП остановлены, ток потребления уменьшается до 2 мкА. Время выхода из

"спящего" режима составляет 500 мкс. Режим пониженного потребления увеличивает время преобразования. При установке 1 на входе ACQMOD сигналом WR = 0 производится запись режима работы АЦП без запуска преобразования. Установка ACQMOD в 0 приводит к запуску преобразования после записи выбранных режимов по сигналу WR (рис. 7.25).

Таблица 7.11

| Бит | Имя | Функция | ||

| D7,D6 | PD1,PD0 | спящий режим (I = 2 мкА) | ||

| режим пониженного потребления | ||||

| внутренний генератор | ||||

| внешний генератор | ||||

| D5 | ACQMOD | ACQMOD = 0; запись данных с запуском АЦП, ACQMOD = 1; запись данных без запуска АЦП | ||

| D4 | SGL/DIF | SGL/DIF = 0; псевдодифференциальные входы SGL/DIF = 1; обычные входы | ||

| D3 | UNI/BIP | UNI/BIP = 0; биполярный режим (от –REF/2 до +REF/2) UNI/BIP = 1; однополярный режим (от 0 до +REF) | ||

| D2 D1 D0 | A2,A1,A0 | SGL/DIF = 1; A2, A1, A0 задают номер канала, SGL/DIF = 0; A2, A1задают номер канала, A0 – полярность подключения дифференциальных входов: A0 = 0; четные каналы к "+", а нечетные к "–" A0 = 1; четные каналы к "–", а нечетные к "+" |

|

Бит SGL/DIF определяет режим работы входного мультиплексора. Бит UNI/BIP задает кодировку результата преобразования.

Рис. 7.25

При однополярном кодировании выходной код изменяется линейно от 0 (0 В на входе) до 4095 (U ref + COM на входе). В случае биполярного преобразования нулю кода соответствует напряжение смещения COM, изменение кодов от 0 до 2047 происходит при изменении входного сигнала от COM до COM + U ref /2, а коды от 4097 до 2048 соответствуют изменению входного сигнала от COM до COM – U ref /2.

Цикл преобразования начинается с записи управляющего слова (ACQMOD = 0, CS = 0 и WR = 0). Преобразование может быть остановлено записью нового управляющего слова. После окончания преобразования выдается сигнал INT для микроконтроллера, который удерживается до первого чтения из АЦП (рис. 7.25).

Для чтения данных необходимо подать на входы CS и RD сигнал нулевого уровня. Микросхема выведет на шину данных младший байт результата. Затем надо установить HBEN = 1. В младшей тетраде шины данных появятся 4 старших бита. В старшей тетраде шины данных при двухполярном режиме работы повторяется старший 12-й бит результата, в однополярном режиме – выводятся 4 нуля.

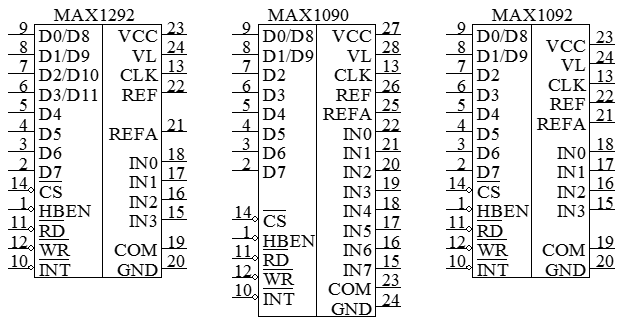

Аналогично с рассмотренной схемой работают АЦП, имеющие 4 входных канала и выполняющие 10-разрядное преобразование (рис. 7.26).

Аналогично с рассмотренной схемой работают АЦП, имеющие 4 входных канала и выполняющие 10-разрядное преобразование (рис. 7.26).

Рис. 7.26

Микросхемы АЦП, как и ЦАП, различаются по разрядности, типу интерфейса, напряжению питания, потребляемому току и времени преобразования (t пр). Кроме того, АЦП необходимо выбирать по уровню входных аналоговых сигналов и по количеству каналов. Основные характеристики микросхем АЦП представлены в табл. 7.12.

Таблица 7.12

| Название | Чи-сло ка-налов | U, В | I,мA | t пр, мкс | Источник U ref, B | Входной сигнал, B | Интер-фейс |

| 8-битовые | |||||||

| MAX165 | 5/±5 | Внутренний1.23 | ±2 U ref | P 8 | |||

| MAX166 | 5/±5 | Внутренний 1.23 | ±2 U ref | P 8 | |||

| MAX1106 | 2.7-5 | 0.25 | Внутренний 2.048 | ± U ref /2 | SPI | ||

| MAX1107 | 0.25 | Внутренний 4.096 | ± U ref /2 | SPI | |||

| MAX155 | 5/±5 | 3.6 | Внешний 2.5 | ± U ref | P 8 | ||

| MAX1113 | 0.25 | Внутренний 4.096 | ± U ref /2 | SPI | |||

| 10-битовые | |||||||

| MAX1084 | 2.5 | Внутренний 2.5 | ± U ref /2 | SPI | |||

| MAX1082 | 2.5 | Внутренний 2.5 | ± U ref /2 | SPI | |||

| MAX1092 | 2.5 | Внутренний 2.5 | ± U ref /2 | P 8 | |||

| MAX1080 | 2.5 | Внутренний 2.5 | ± U ref /2 | SPI | |||

| MAX1090 | 2.5 | Внутренний 2.5 | ± U ref /2 | P 8 | |||

| 12-битовые | |||||||

| MAX164 | 5/-12 | 8.3 | Внутренний 5 | ±5 | P 12/8 | ||

| MAX167 | 5/-12 | 8.3 | Внутренний 2.5 | ±2.5 | P 12/8 | ||

| MAX1284 | 2.5 | Внутренний 2.5 | + U ref | SPI | |||

| MAX1296 | 2.5 | Внутренний 2.5 | ± U ref /2 | P 12 | |||

| MAX1282 | 2.5 | Внутренний 2.5 | ± U ref /2 | SPI | |||

| MAX1292 | 2.5 | Внутренний 2.5 | ± U ref /2 | P 8 | |||

| MAX1298 | 2.5 | Внутренний 2.5 | ± U ref /2 | SPI | |||

| MAX1294 | 2.5 | Внутренний 2.5 | ± U ref /2 | P 12 | |||

| MAX1280 | 2.5 | Внутренний 2.5 | ± U ref /2 | SPI | |||

| MAX1290 | 2.5 | Внутренний 2.5 | ± U ref /2 | P 8 |

|

|

|

|

|

Дата добавления: 2014-12-27; Просмотров: 1589; Нарушение авторских прав?; Мы поможем в написании вашей работы!