КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Исследование логических схем

|

|

|

|

Отчет по учебной практике

по дисциплине

«микросхемотехника»

Выполнил

студент гр. 1084/1 К.А.Лобов

<подпись>

Руководитель

доцент В. В. Амосов

<подпись>

Санкт-Петербург

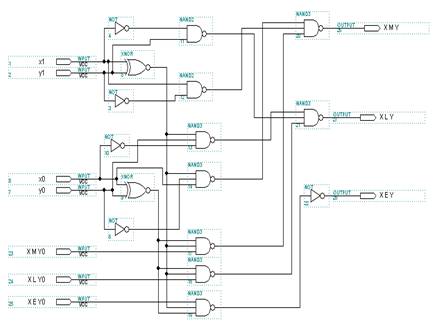

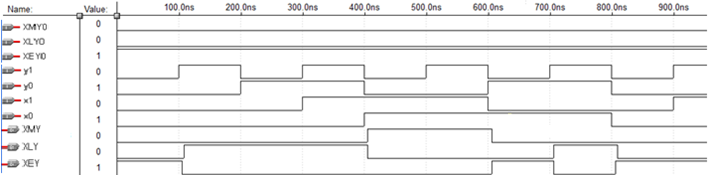

Лабораторная работа: Исследование функционирования логическоий схемы компаратора для сравнения двухбитных слов

Компаратор — это устроийство сравнения двух двоичных слов, определяющее в каком отношении находятся между собоий эти слова.

Здесь: “XMY” – “X>Y”; “XLY” – “X<Y”; “XEY” – “X=Y”.

1)Схема 2х разрядного компаратора

Временная диаграмма соответствует описанию.

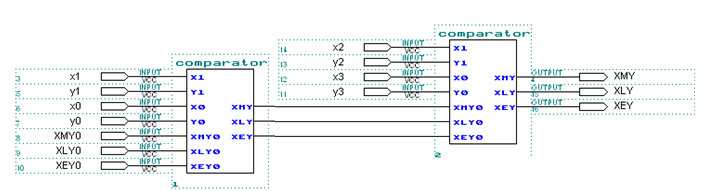

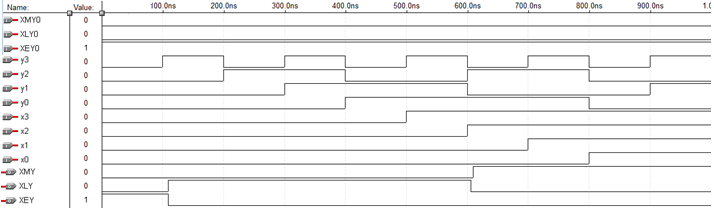

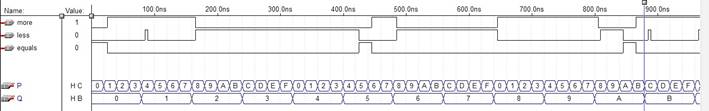

2) Схема 4-х разрядного компаратора

(“XMY” – “X>Y”; “XLY” – “X<Y”; “XEY” – “X=Y”.)

Временная диаграмма соответствует описанию.

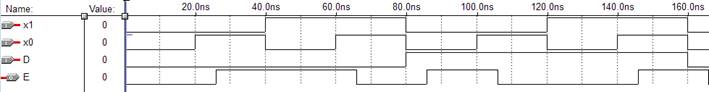

4) VHDL

Library IEEE;

use ieee.std_logic_1164.all;

use ieee.std_logic_signed.all;

entity comparator_vhd is

port (P,Q: in std_logic_vector(3 downto 0);

more,less,equals: out std_logic);

end comparator_vhd;

architecture behav of comparator_vhd is

signal tmpP,tmpQ: integer;

begin

process (p,q)

begin

tmpP <= conv_integer(P);

tmpQ <= conv_integer(Q);

more <= '0';

less <= '0';

equals <= '0';

if tmpP = tmpQ then

equals <= '1';

end if;

if tmpP < tmpQ then

less <= '1';

end if;

if tmpP > tmpQ then

more <= '1';

end if;

end process;

end behav;

Как видно из временной диаграммы, VHDL модель полностью удовлетворяет условию.

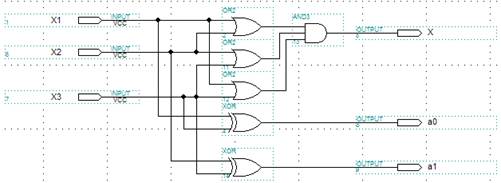

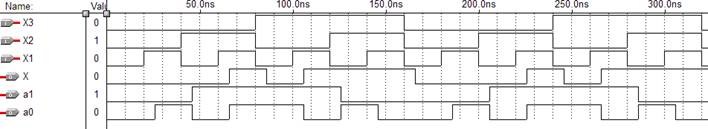

Лабораторная работа: Исследование функционирования схем контроля по модулю 2 и схемы мажоритарного элемента

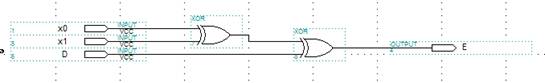

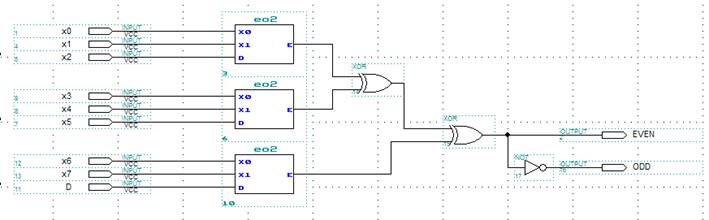

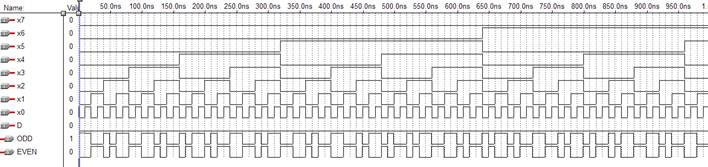

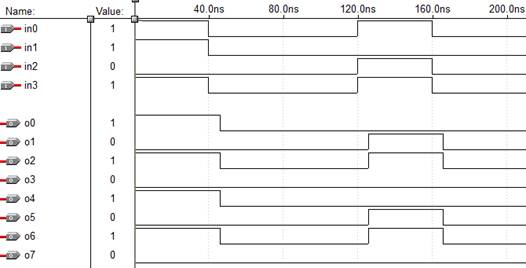

1) Схема контроля на четность/нечетность для двухразрядного слова с третьим контрольным входом, допускающую свертку по модулю

а) Графическая модель

Временная диаграмма соответствует описанию.

б) VHDL

Library IEEE;

use ieee.std_logic_1164.all;

use ieee.std_logic_signed.all;

entity odd4_vhd is

port (p: in std_logic_vector(3 downto 0);

odd,even: out std_logic);

end odd4_vhd;

architecture behav of odd4_vhd is

begin

process (p)

function OddEven(p: std_logic_vector(3 downto 0)) return bit is

variable tmp:bit:='0';

begin

if p(0)='1' then

if tmp='0' then

tmp:= '1';

else

tmp:= '0';

end if;

end if;

if p(1)='1' then

if tmp='0' then

tmp:= '1';

else

tmp:= '0';

end if;

end if;

if p(2)='1' then

if tmp='0' then

tmp:= '1';

else

tmp:= '0';

end if;

end if;

if p(3)='1' then

if tmp='0' then

tmp:= '1';

else

tmp:= '0';

end if;

end if;

return tmp;

end OddEven;

begin

even <= '0';

odd <= '0';

if OddEven(p)='1' then

odd <= '1';

else

even <= '1';

end if;

end process;

end behav;

Как видно из временной диаграммы, VHDL модель полностью удовлетворяет условию.

Как видно из временной диаграммы, VHDL модель полностью удовлетворяет условию.

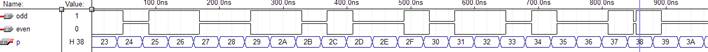

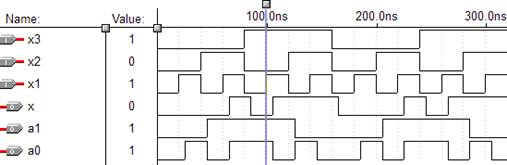

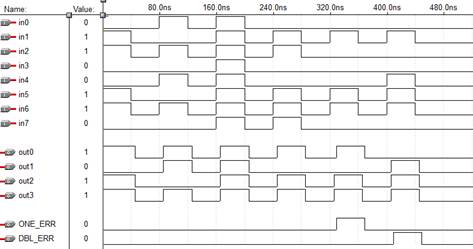

2) Схема контроля четности/нечетности восьмибитного слова

а) Графическая модель

Временная диаграмма соответствует описанию.

б) VHDL

Library IEEE;

use ieee.std_logic_1164.all;

use ieee.std_logic_signed.all;

entity odd8_vhd is

port (p: in std_logic_vector(7 downto 0);

odd,even: out std_logic);

end odd8_vhd;

architecture behav of odd8_vhd is

begin

process (p)

function OddEven(p: std_logic_vector(7 downto 0)) return bit is

variable tmp:bit:='0';

begin

if p(0)='1' then

if tmp='0' then

tmp:= '1';

else

tmp:= '0';

end if;

end if;

if p(1)='1' then

if tmp='0' then

tmp:= '1';

else

tmp:= '0';

end if;

end if;

if p(2)='1' then

if tmp='0' then

tmp:= '1';

else

tmp:= '0';

end if;

end if;

if p(3)='1' then

if tmp='0' then

tmp:= '1';

else

tmp:= '0';

end if;

end if;

if p(4)='1' then

if tmp='0' then

tmp:= '1';

else

tmp:= '0';

end if;

end if;

if p(5)='1' then

if tmp='0' then

tmp:= '1';

else

tmp:= '0';

end if;

end if;

if p(6)='1' then

if tmp='0' then

tmp:= '1';

else

tmp:= '0';

end if;

end if;

if p(7)='1' then

if tmp='0' then

tmp:= '1';

else

tmp:= '0';

end if;

end if;

return tmp;

end OddEven;

begin

even <= '0';

odd <= '0';

if OddEven(p)='1' then

odd <= '1';

else

even <= '1';

end if;

end process;

end behav;

Как видно из временной диаграммы, VHDL модель полностью удовлетворяет условию.

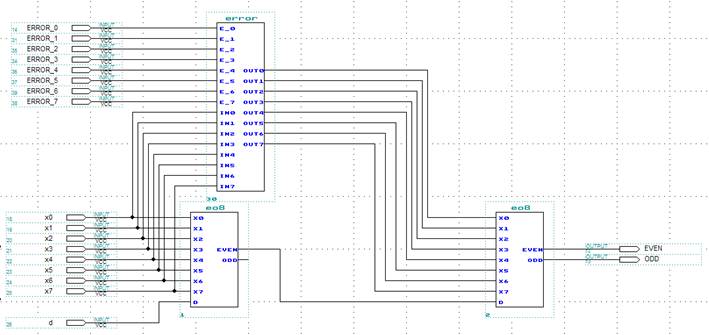

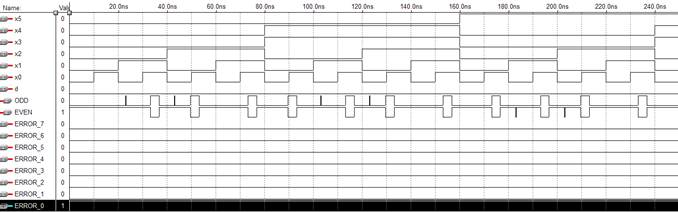

3) Применение элемента контроля четности/нечетности в схеме обнаружения ошибок при передаче данных.

Временная диаграмма соответствует описанию.

Мажоритарный элемент – логическая схема с чётным или нечётным числом входов и одним выходным сигналом, значение которого совпадает со значением, на большинстве входов.

4) Схема мажоритарного элемента

Временная диаграмма соответствует описанию.

5) VHDL мажоритарного элемента

Library IEEE;

use ieee.std_logic_1164.all;

entity major is

port (x1,x2,x3: in std_logic;

x,a0,a1: out std_logic);

end major;

architecture behav of major is

begin

process (x1,x2,x3)

begin

x <= (x1 and x2) or (x1 and x3) or (x2 and x3);

a0 <= x1 xor x3;

a1 <= x2 xor x3;

end process;

end behav;

Как видно из временной диаграммы, VHDL модель полностью удовлетворяет условию.

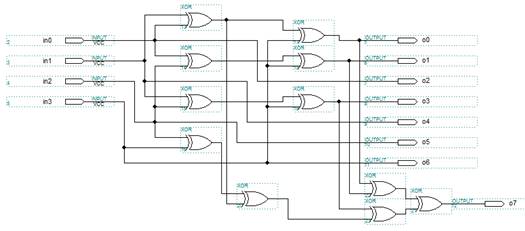

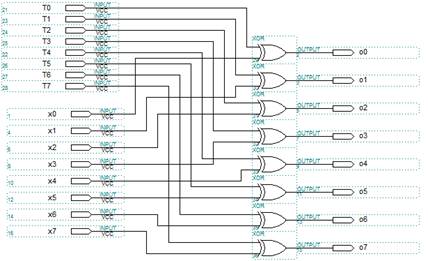

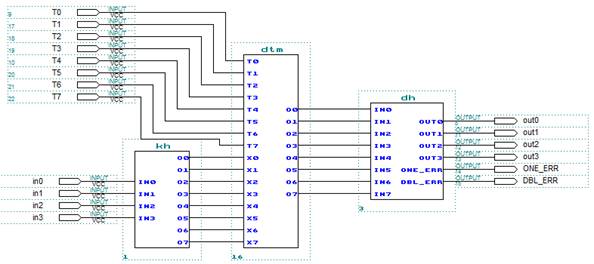

Лабораторная работа: Исследование функционирования логической схемы кодера и декодера Хемминга

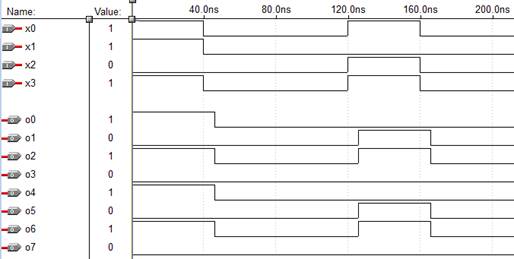

1. Схема кодера Хемминга.

На выходе данного кодера мы получаем модифицированный код Хемминга: K1,K2,D0,K3,D1,D2,D3; где D0,D1,D2,D3 – информационные разряды, а K1,K2,K3,K – контрольные разряды кода Хемминга.

Временная диаграмма соответствует описанию.

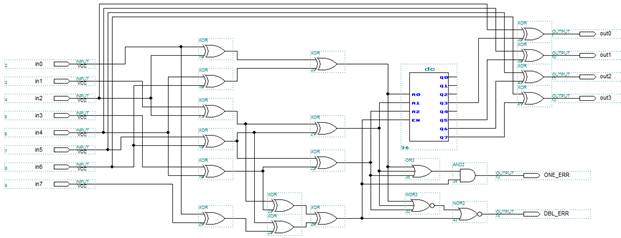

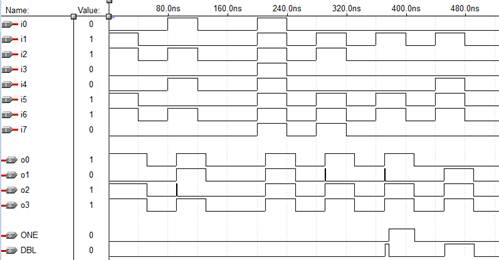

2. Схема декодера Хемминга.

При декодировании в данном декодере из модифицированного кода Хемминга определяется синдром ошибки или двоичное слово: KP,P3,P2,P1. Далее при наличии одиночной ошибки она исправляется в соответствии с синдромом ошибки.

Так же модуль имеет два выхода для обозначения ошибок:

- ONE_ERR – если на этом выходе «1», то была одиночная ошибка, и она исправлена;

- DBL_ERR – если на этом выходе «1», то была двойная ошибка, в результате имеем сбой в работе модуля.

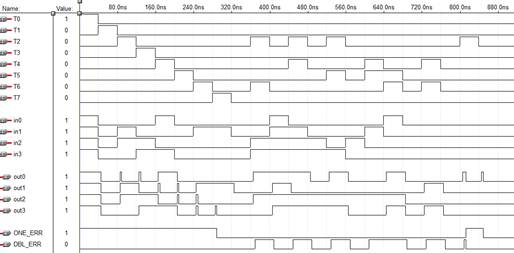

Временная диаграмма соответствует описанию.

3. Проект примера, реализующего функции кодирования и декодирования информации с использованием модифицированного кода Хемминга.

a) Разработаем специальный модуль для создания ошибок Data Transformer Module.

б) Схема примера исправления ошибок

4. Поведенческая модель кодера Хемминга на языке VHDL.

library IEEE;

use ieee.std_logic_1164.all;

entity kh2 is

port(x: in std_logic_vector (3 downto 0);

o: out std_logic_vector (7 downto 0));

end kh2;

architecture behavior of kh2 is

signal k1,k2,k3: std_logic;

begin

k1<= x(0) xor x(1) xor x(3);

k2<= x(0) xor x(2) xor x(3);

k3<= x(1) xor x(2) xor x(3);

o(0)<= k1;

o(1)<= k2;

o(2)<= x(0);

o(3)<= k3;

o(4)<= x(1);

o(5)<= x(2);

o(6)<= x(3);

o(7)<= k1 xor k2 xor x(0) xor k3 xor x(1) xor x(2) xor x(3);

end behavior;

5. Поведенческая модель декодера Хемминга VHDL.

library IEEE;

use ieee.std_logic_1164.all;

entity dh2 is

port(i: in std_logic_vector (7 downto 0);

o: out std_logic_vector (3 downto 0);

ONE: out std_logic;

DBL: out std_logic);

end dh2;

architecture behavior of dh2 is

signal p1,p2,p3,KP: std_logic;

begin

p1<= i(0) xor i(2) xor i(4) xor i(6);

p2<= i(1) xor i(2) xor i(5) xor i(6);

p3<= i(3) xor i(4) xor i(5) xor i(6);

KP<= i(0) xor i(1) xor i(2) xor i(3) xor i(4) xor i(5) xor i(6) xor i(7);

ONE<= KP and (p1 or p2 or p3);

DBL<= not(KP or not(p1 or p2 or p3));

o(0)<= i(2) xor (KP and (not p3 and p2 and p1));

o(1)<= i(4) xor (KP and (p3 and not p2 and p1));

o(2)<= i(5) xor (KP and (p3 and p2 and not p1));

o(3)<= i(6) xor (KP and (p3 and p2 and p1));

end behavior;

Как видно из временной диаграммы, VHDL модель полностью удовлетворяет условию.

|

|

|

|

Дата добавления: 2014-12-24; Просмотров: 3049; Нарушение авторских прав?; Мы поможем в написании вашей работы!