КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Раскройте скобки, употребляя глаголы в Present Continuous или в Present Simple. 2 страница

|

|

|

|

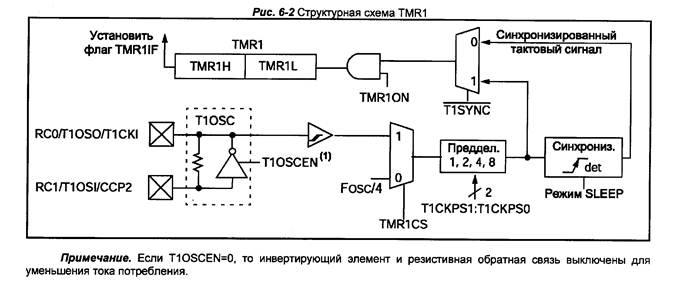

Работа TMR1 в режиме таймера.

Приращение таймера происходит от внутреннего сигнала Fosc/4,когда бит TMR1CS(T1CON<1>) сброшен в "0". В этом режиме бит синхронизации T1SYNC(T1CON<2>) игнорируется, потому что внутренний тактовый сигнал всегда синхронизирован.

Работа TMR1 в режиме счетчика.

TMR1 может работать в синхронном или асинхронном режимах в зависимости от состояния бита TMR1CS. Когда TMR1 использует внешний тактовый сигнал, приращение таймера происходит по переднему фронту. Включив TMR1 в режим внешнего тактового сигнала счет начнется только после появления заднего фронта.

Работа TMR1 в режиме синхронного счетчика

Работа TMR1 от внешнего источника тактового сигнала выбирается установкой бита TMR1CS в "1". В этом режиме приращение таймера происходит по каждому переднему фронту сигнала на выводе RC1/T1OS/CCP2 (если T1OSCEN=1) или RC0/T1OSO/T1CKI (если T1OSCEN=0).

Если –T1SYNC=0, то активный фронт внешнего тактового сигнала синхронизируется с внутренним тактовым сигналом на выходе асинхронного предделителя.

В SLEEP режиме микроконтроллера счетчик не будет инкрементироваться (при наличии тактового сигнала), т.к. синхронизатор выключен (предделитель продолжает счет от тактовых импульсов).

Работа TMR1 в режиме асинхронного счетчика

Если бит –T1SYNC (T1CON<2>) установлен в "1", внешний тактовый сигнал TMR1 не будет синхронизироваться с внутренним тактовым сигналом микроконтроллера, таймер продолжает работать в режиме SLEEP микроконтроллера. Переполнение таймера вызовет "пробуждение" микроконтроллера, если разрешено прерывание от TMR1. Однако требуется осторожность при записи/чтении TMR1.

В этом режиме TMR1 не может использоваться для захвата/сравнения данных модуля CCP.

Чтение/запись TMR1 в асинхронном режиме.

Чтение TMR1H или TMR1L во время счета в асинхронном режиме, гарантирует получение текущего значения счетчика (реализовано аппаратно). Однако пользователь должен иметь в виду, что чтение 16-разрядного значения выполняется по байтно. Это накладывает некоторые ограничения, так как таймер может переполниться между чтениями байт.

Запись в TMR1 рекомендуется выполнять после остановки таймера. Запись в регистры TMR1 во время приращения таймера может привести к непредсказуемому значению регистра.

Генератор TMR1

Резонатор подключается к выводам T1OSI (вход) и T1OSO (выход усилителя). Максимальная частота резонатора 200 КГц. Тактовый генератор TMR1 (идентичный LP генератору) в основном предназначен для кварцевого резонатора 32 КГц. Включение генератора производится установкой бита T1OSEN в регистре T1CON<3>, что позволяет работать TMR1 в SLEEP режиме микроконтроллера.

Пользователь должен обеспечить программную задержку, чтобы гарантировать надлежащий запуск генератора.

Сброс TMR1 триггером модуля CCP

Если модуль CCP1 или CCP2 работает в режиме сравнения с триггером специальных функций (CCP1M3:CCP1M0=1011), то сигнал триггера сбросит TMR1.

Сигнал с триггера специальных функций модуля CCP1 не будет устанавливать флаг TMRIF (PIR<0>) в "1".

TMR1 должен работать в режиме синхронизированного внешнего тактового сигнала или внутреннего тактового сигнала. В асинхронном режиме эта функция не работает.

Когда запись в TMR1 совпадает с сигналом сброса от триггера специальных событий, приоритет отдается записи в TMR1.

В этом режиме модуля CCP период сброса TMR1 сохраняется в регистрах CCPRxH:CCPRxL.

Сброс регистров TMR1 (TMR1H, TMR1L)

Регистры TMR1H, TMR1L не сбрасываются в 00h при сбросе по включению питания POR и других видах сброса, кроме сброса по сигналу триггера специальных событий модуля CCP1 или CCP2.

Регистр T1CON сбрасывается в 00h при сбросе POR и BOR (TMR1 выключается, коэффициент предделителя равен 1:1). При всех остальных видах сброса значение регистра T1CON не изменится.

Предделитель TMR1

Предделитель TMR1 очищается при записи в регистр TMR1H и TMR1L.

4.3. Модуль таймера TMR2

TMR2 – 8-разрядный таймер с программируемым предделителем и выходным делителем, 8-разярдным регистром периода PR2. TMR2 может быть опорным таймером для CCP модуля в ШИМ режиме. Регистры TMR2 доступны для записи/чтения и очищаются при любом виде сброса.

Входной тактовый сигнал (Fosc/4) поступает через предделитель с программируемым коэффициентом деления (1:1, 1:4 или 1:16), определяемый битами T2CKPS1:T2CKPS0 (T2CON<1:0>)/

TMR2 cчитает, инкрементируя от 00h до значения в регистре PR2, затем сбрасывается в 00h на следующем машинном цикле. Регистр PR2 доступен для записи и чтения. После сброса значение регистра PR2 равно FFh.

Сигнал переполнения TMR2 проходит через выходной 4-разядный делитель с программируемым коэффициентом деления (от 1:1 до 1:16 включительно) для установки флага TMR2IF в регистре PIR1<1>.

Для уменьшения энергопотребления таймер TMR2 может быть выключен сбросом бита TMR2ON (T2CON<2>) в "0".

Предделитель и выходной делитель TMR2

Счетчик предделителя и выходного делителя сбрасываются в случае:

- записи в регистр TMR2;

- записи в регистр T2CON;

- любого вида сброса микроконтроллера (POR, BOR, сброс WDT или активный сигнал –MCLR)

Регистр TMR2 не очищается при записи в T2CON.

Сигнал TMR2

Сигнал переполнения TMR2 (до выходного предделителя) поступает в модуль SSP для управления скоростью передачи данных.

5. Память ПИК-контроллеров

Особый интерес представляет организация памяти в микроконтроллерах. В микроконтроллерах три вида памяти: память программ, память данных и ЕЕPROM памяти данных. Память программ и память данных имеют раздельные шины данных и адреса, что позволяет выполнять параллельный доступ.

5.1.Организация памяти программ

Микроконтроллеры имеют 13-разрядный счетчик команд РС, способный адресовать 8К х 14 слов памяти программ. Физически реализовано FLASH памяти 8К х 14 для PIC16F877. Обращение к физически нереализованной памяти программ приведет к адресации реализованной памяти.

Адрес вектора сброса – 0000h. Адрес вектора прерываний – 0004h.

Память программ состоит из 4-х страниц: страница 0, страница 1, страница 2, страница 3.

Страница 0 имеет адреса: 0005h-07FFh.

4 0800h-0FFFh.

5 1000h-17FFh

6 1800h-1FFFh

5.2.Организация памяти данных

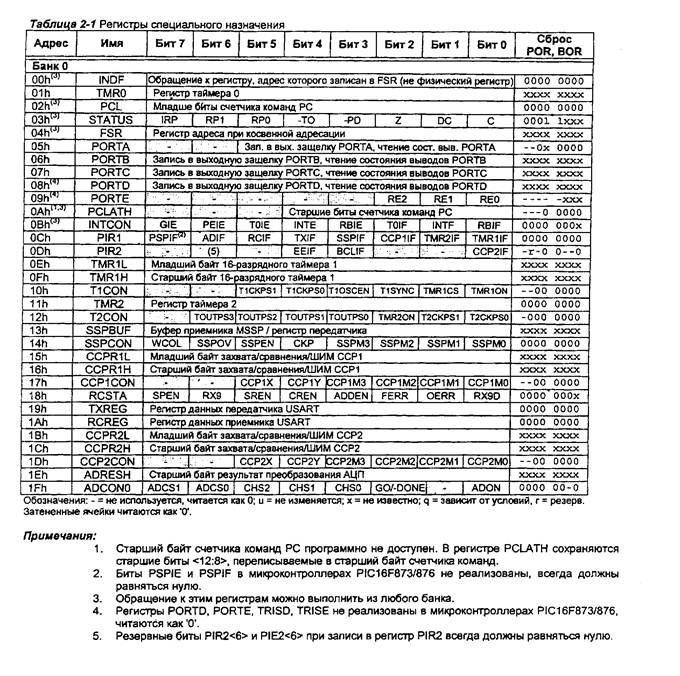

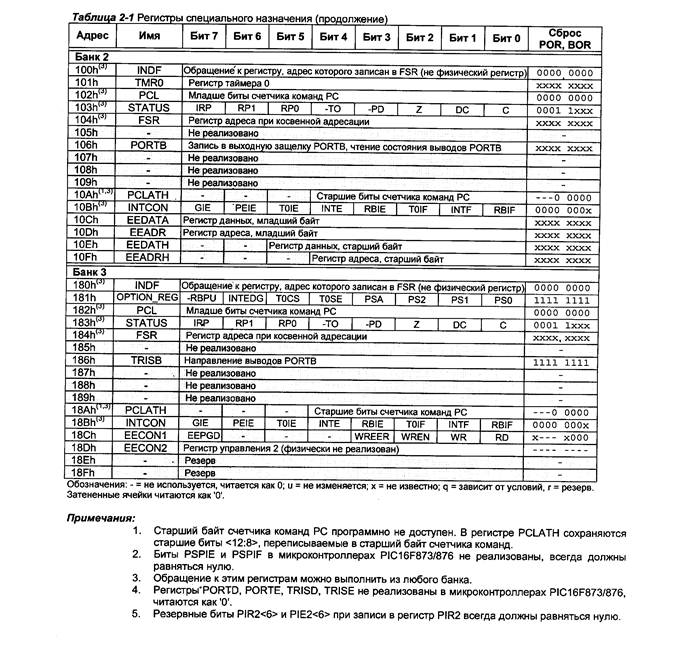

Память данных разделяется на 4 банка, которые содержат регистры общего и специального назначения (SFR). Биты RP1 (STATUS<6>) и RP0 (STATUS<5>) предназначены для управления банками. В Таблице приведено состояние управляющих битов при обращении к банкам памяти данных.

| RP1:RP0 | Банк |

Объем памяти банков данных до 128 байт (7Fh). В начале банка размещаются регистры специального назначения, затем регистры общего назначения, выполненные как статическое ОЗУ. Все реализованные банки содержат регистры специального назначения. Часто используемые регистры специального назначения могут отображаться и в других банках памяти.

Регистры общего назначения.

К регистрам общего назначения можно обращаться прямой или косвенной адресацией, через регистр FSR.

Регистры специального назначения

С помощью регистров специального назначения выполняется управления функциями ядра и периферийными модулями микроконтроллера. Регистры специального назначения реализованы как статическое ОЗУ. В этом разделе описаны регистры, управляющие функциями ядра микроконтроллера.

5.3.EEPROM память данных. FLASH память программ.

Данные из EEPROM памяти данных и FLASH памяти программ могут быть прочитаны /перезаписаны в нормальном режиме работы МК во всем диапазоне напряжения питания. Операции выполняются с одним байтом для EEPROM память данных и одним словом для FLASH память программ. Запись производится по принципу "стирание-запись" для каждого байта или слова. Сформированная кодом программы операция стирания не может быть выполнена при включенной защите записи.

Доступ к памяти программ позволяет выполнить вычисление контрольной суммы. Данные, записанные в памяти программ, могут быть использованы в виде: 14-разрядных чисел, калибровочной информации, серийных номеров, упакованных 7-разрядных символов ASCII и т.д. В случае обнаружения недействительной команды в памяти программ, выполняется пустой цикл NOP.

Число циклов стирания/записи определяется электрическими характеристиками этих устройств. Число циклов стирания/записи для FLASH памяти программ значительно ниже по сравнению с EEPROM памятью данных, поэтому EEPROM память данных должна использоваться для сохранения часто изменяемых данных. Время записи данных управляется внутренним таймером, оно зависит от напряжения питания, температуры и имеет небольшой технологический "разброс".

При записи байта или слова автоматически стирается соответствующая ячейка, а затем выполняется запись. Запись в EEPROM память данных не воздействует на выполнение программы, а при записи во FLASH память программ выполнение программы останавливается на время записи. Нельзя обратиться к памяти программ во время цикла записи. В течение операции записи тактовый генератор продолжает работать, периферийные модули включены и генерируют прерывания, которые "ставятся в очередь" до завершения цикла записи. После завершения записи выполняется загруженная команда (из-за конвейерной обработки) и происходит переход по вектору прерываний, если прерывание разрешено, и условие прерывания возникло во время записи.

Доступ к функциям записи/чтения EEPROM памяти данных и FLASH памяти программ выполняется через шесть регистров специального назначения:

EEDATA;

EEDATH;

EEADR;

EEADRH;

EECON1;

EECON2.

Операция чтения/записи EEPROM память данных не приостанавливают выполнение программы. В регистре EEADR сохраняется адрес ячейки EEPROM память данных. Данные сохраняются/читаются из регистра EEDATA. В микроконтроллерах 877 объем EEPROM память данных 256 байт.

Чтение FLASH памяти программ не влияет на выполнение программы, а во время операции записи выполнение программы приостановлено. В спаренных регистрах EEADRH:EEADR сохраняется 13-разрядный адрес ячейки памяти программ, к которой необходимо делать обращение. Спаренные регистры EEDATH:EEDATA содержат 14 разрядные данные для записи и отображают значение из памяти программ при чтении. В регистры EEADRH:EEADR должен быть загружен адрес физически реализованной памяти программ (от 0000h до 1FFFh), потому что циклическая адресация не поддерживается.

5.4. Регистры EECON1, EECON2

Регистр EECON1 содержит биты управления косвенной записи/чтения EEPROM память данных FLASH память программ. Регистр EECON2 физически не реализован, он используется только при операциях записи с целью предотвращения случайной записи.

Значение бита EEPGD в регистре EECON1 определяет тип памяти, к которой будет выполнено обращение. Если EEPGD = 0, то операции относятся к EEPROM память данных. Когда EEPGD=1, обращение происходит к FLASH память программ.

В операции чтения используется только один дополнительный бит RD, инициализирующий операцию чтения из указанной памяти. Установив бит RD в "1", значение ячейки памяти будет доступно в регистре данных. Бит RD не может быть сброшен программно в "0", он сбрасывается автоматически по окончании операции чтения. При чтении из EEPROM памяти данные будут доступны в регистре EEDATA в следующем машинном цикле, после установки бита RD. При чтении из FLASH память программ данные будут доступны в регистре EEDATA:EEDATH на втором машинном цикле, после установки бита RD.

В операции записи используется два служебных бита WR, WREN и два бита статуса WRERR, EEIF. Бит WREN применяется для разрешения/запрещения операции записи (WREN = 0 –операция записи запрещена). Перед выполнением записи бит WREN необходимо установить в "1". Бит WR предназначен для инициализации записи, он аппаратно сбрасывается в "0" по завершении операции записи. Флаг прерывания EEIF устанавливается в "1" по завершении записи. Этот флаг должен быть сброшен программно в "0" перед установкой бита WR.

Для EEPROM памяти данных:

После установки битов WREN, WR в "1" стирается, указанная в регистре EEADR, ячейка EEPROM памяти, а затем происходит запись данных из регистра EEDATA. Операция записи сопровождается выполнением кода программы. По завершении записи устанавливается флаг прерывания EEIF в "1".

Для FLASH памяти программ:

После установки битов WREN, WR в "1" микроконтроллер приостанавливает выполнение программы. Стирается ячейка памяти программ, указанная в регистре EEADRH:EEADR, затем происходит запись данных из регистра EEDATAH:EEDATA. По завершении записи устанавливается флаг прерывания EEIF в "1", а микроконтроллер продолжит выполнять код программы.

Бит WRERR указывает, что произошел сброс микроконтроллера во время выполнения операции записи. Бит WRERR устанавливается в "1", если во время выполнения записи данных произошел сброс данных по сигналу –MCLR или по переполнению сторожевого таймера WDT в нормальном режиме. Проверив состояние бита WRERR, пользователь может повторить запись (регистры EEDATA и EEADR не изменяют своего значения). Содержимое регистров данных, адреса и бит EEPGD не изменяется после сброса по сигналу –MCLR, по переполнению сторожевого таймера WDT в нормальном режиме.

5.5. EEPROM память данных..

Чтение из EEPROM памяти данных.

Последовательность действий при чтении из EEPROM память данных.

1.Записать адрес в регистр EEADR.

2.Сбросить в "0" бит EEPGD для обращения к EEPROM памяти данных.

3.Инициализировать операцию чтения установкой бита RD в "1".

4.Прочитать данные из регистра EEDATA.

После установки в "1" бита RD данные будут доступны в регистре EEDATA на следующем машинном цикле. Данные в регистре EEDATA сохраняются до выполнения следующей операции чтения или записи в EEDATA.

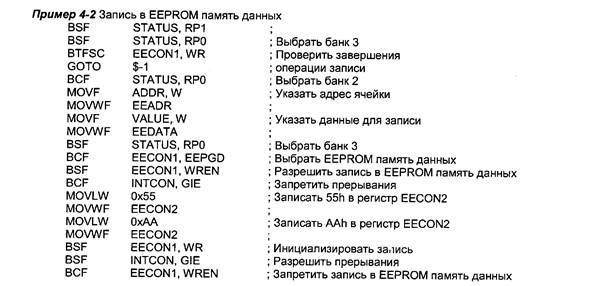

Запись в EEPROM память данных.

Запись данных в EEPROM память данных несколько сложнее чтения. Адрес ячейки памяти и записываемый данные должны быть помещены в соответствующие регистры специального назначения, бит EEPGD сбрасывается в "0". Бит WREN должен всегда равняться нулю, если не осуществляется непосредственная запись в память. Бит WR может быть установлен в "1" только, если бит WREN был установлен в предыдущих командах, т.е. биты WR, WREN не могут устанавливаться в "1" одной командой. Бит WREN должен быть сброшен в "0" после инициализации записи (на процесс записи он не влияет).

Перед записью в EEPROM память должна быть выполнена обязательная последовательность команд, предотвращающая случайную запись. Обязательная последовательность выполняется при выключенных прерываниях.

Последовательность действий при записи в память.

1. Если шаг 10 не был выполнен, то необходимо проверить, что не происходит запись (WR=0).

2. Записать адрес в регистр EEADR. Проверьте, что записанный адрес корректен для данного типа микроконтроллера.

3. Записать 8-разрядное значение в регистр EEDATA.

4. Сбросить в "0" бит EEPGD для обращения к EEPROM памяти данных.

5. Установить бит WREN в "1", разрешив запись в EEPROM память.

6. Запретить прерывания, если они разрешены.

7. Выполнить обязательную последовательность из пяти команд:

- запись значения 55h в регистр EECON2 (две команды, сначала в W затем в EECON2);

- запись значения AAh в регистр EECON2 (две команды, сначала в W затем в EECON2);

- установить бит WR в "1".

8. Разрешить прерывания (если необходимо).

9. Сбросить бит WREN в "0".

10. После завершения цикла записи сбрасывается в "0" бит WR, устанавливается в "1" флаг прерывания EEIF (сбрасывается программно), Если шаг 1 не выполняется, то необходимо проверить состояние битов EEIF, WR перед началом записи.

5.6. FLASH памяти программ

Чтение из FLASH памяти программ

Чтение из FLASH памяти программ очень похоже на процедуру чтения из EEPROM памяти данных, только необходимо выполнить две инструкции после установки бита RD в "1". Два пустых цикла NOP используются микроконтроллером для чтения данных из FLASH памяти программ и сохранения их в регистрах EEDATH:EEDATA. Данные в регистрах будут доступны после выполнения второй инструкции NOP. Данные в регистре EEDATH:EEDATA сохраняются до выполнения следующей операции чтения или записи в EEDATH:EEDATA.

Рекомендованная последовательность действий при чтении из FLASH памяти программ:

1. Записать адрес в регистры EEDATH:EEDATA. Проверьте, что записанный адрес корректен для данного типа микроконтроллера.

2. Установить в "1" бит EEPGD для обращения к FLASH памяти программ.

3. Инициализировать операцию чтения установкой бита RD в "1".

4. Выполнить две команды NOP, чтобы позволить микроконтроллеру произвести чтение из FLASH памяти программ.

5. Прочитать данные из регистров EEDATH:EEDATA.

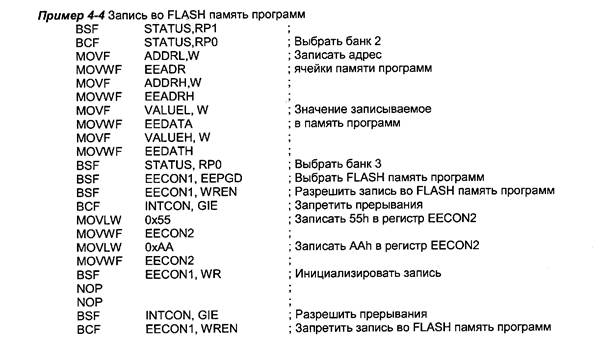

Запись во FLASH память программ.

В течение операции записи выполнение программы останавливается, тактовый генератор продолжает работать, периферийные модули включены и генерируют прерывания, которые "ставятся в очередь" до завершения цикла записи. После завершения записи микроконтроллер продолжает выполнять код программы с места остановки. Другим существенным отличием записи во FLASH память программ является наличие бита защиты WRTв слове конфигурации, предотвращающий любую запись в память программ.

Запись данных во FLASH память программ несколько сложнее чтения. Адрес ячейки памяти программ и записываемые данные должны быть помещены в соответствующие специального назначения, бит EEPG устанавливается в "1". Бит WREN должен всегда равняться нулю, кроме непосредственной записи во FLASH память программ. Бит WR может быть установлен в "1" только, если бит WREN был установлен в предыдущих командах, т.е. биты WR, WREN не могут устанавливаться в "1" одной командой. Бит WREN должен быть сброшен программно в "0" после инициализации записи (на процесс записи он не влияет).

Перед записью во FLASH память программ должна быть выполнена обязательная последовательность команд, предотвращающая случайную запись. Обязательная последовательность выполняется при выключенных прерываниях. После обязательной последовательности должны размещаться две инструкции NOP, позволяющие микроконтроллеру произвести запись. Выполнение программы после записи начинается с инструкции, расположенной после двух команд NOP.

Последовательность действий при записи во FLASH память программ.

1. Записать адрес в регистры EEDATH:EEDATA. Проверить, что записанный адрес корректен для данного типа микроконтроллера.

2. Записать 14-разрядное значение в регистры EEDATH:EEDATA.

3. Установить в "1" бит EEPGD для обращения к FLASH памяти программ.

4. Установить бит WREN в "1", разрешив запись во FLASH память программ.

5. Запретить прерывания, если они разрешены.

6. Выполнить обязательную последовательность из пяти команд:

- запись значения 55h в регистр EECON2 (две команды, сначала в W затем в EECON2);

- запись значения AAh в регистр EECON2 (две команды, сначала в W затем в EECON2);

- установить бит WR в "1".

7. Выполнить две команды NOP, чтобы позволить микроконтроллеру произвести запись во FLASH память программ.

8. Разрешить прерывания (если необходимо).

9. Сбросить бит WREN в "0".

По завершению операции записи аппаратно сбрасывается в "0" бит WR и устанавливается в "1" флаг прерывания EEIF (флаг EEIF сбрасывается в "0" программно). Для определения окончания операции записи проверять бит WR и EEIF не обязательно, т.к. микроконтроллер не выполняет программу во время записи во FLASH память программ.

6.Аналого-цифровой преобразователь

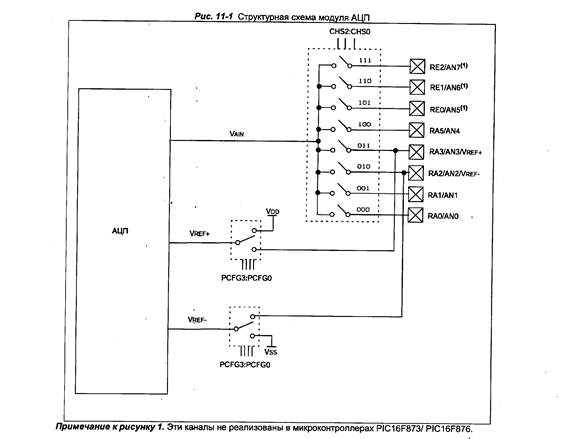

Модуль АЦП имеет 5 каналов у 28 выводных и 8 каналов у 40/44 выводных микросхем.

Входной аналоговый сигнал через коммутатор заряжает внутренний конденсатор АЦП СHOLD. Модуль АЦП преобразует напряжение, удерживаемое на конденсаторе в соответствующий 10-разрядный цифровой код методом последовательного приближения. Источник верхнего и нижнего опорного напряжения может быть программно выбран с выводов VDD, VSS, RA2 или RA3.

Допускается работа модуля АЦП в SLEEP режиме микроконтроллера, при этом в качестве источника тактовых импульсов для АЦП должен быть выбран RC генератор.

6.1. Регистры АЦП

Для управления АЦП в микроконтроллере используется 4 регистра:

- регистр результата ADRESH (старший байт);

- регистр результата ADRESL (младший байт);

- регистр управления ADCON0;

- регистр управления ADCON1/

Регистр ADCON0 используется для настройки работы модуля АЦП, а с помощью регистра ADCON1 устанавливается какие входы микроконтроллера будут использоваться модулем АЦП и в каком режиме (аналоговый или цифровой порт ввода/вывода).

В регистрах ADRESH:ADRESL сохраняется 10-разрядный результат АЦП преобразования. После завершения преобразования результат преобразования записывается в регистры ADRESH:ADRESL, сбрасывается флаг GO/-DONE (ADCON0<2>), устанавливается флаг прерывания ADIF. Структурная схема модуля АЦП показана на рис. 5.1

Рис.5.1. Структурная схема АЦП.

6.2.Порядок работы с АЦП

После включения и конфигурации АЦП выбирается рабочий аналоговый канал. Соответствующие биты TRIS аналоговых каналов должны настраивать порт ввода/вывода на вход. Перед началом преобразования необходимо выдержать временную паузу.

Рекомендованная последовательность действий для работы с АЦП:

- настроить модуль АЦП:

- настроить выводы как аналоговые входы, входы VREF или цифровые

каналы ввода/вывода (ADCON1);

- выбрать входной канал АЦП (ADCON0);

- выбрать источник тактовых импульсов для АЦП (ADCON0);

- включить модуль АЦП (ADCON0);

- настроить прерывание от модуля АЦП (если необходимо):

- сбросить бит ADIF в "0";

- установить бит ADIE в "1";

- установить бит PEIE в "1";

- установить бит GIE в "1".

- Выдержать паузу, необходимую для зарядки конденсатора CHOLD.

- начать аналого-цифровое преобразование

- установить бит GO/-DONE в "1" (ADCON0);

- ожидать окончания преобразования

- ожидать пока бит GO/-DONE не будет сброшен в "0"

ИЛИ

- ожидать прерывание по окончанию преобразования.

- считать результат преобразования из регистров ADRESH:ADRESL,

сбросить бит ADIF в "0", если это необходимо.

- для следующего преобразования необходимо выполнить шаги, начиная с пункта 1 или 2. Время преобразования одного бита определяется как время TAD. Минимальное время ожидания перед следующим преобразованием должно составлять не менее 2 TAD.

6.2.1..Выбор источника тактовых импульсов для АЦП

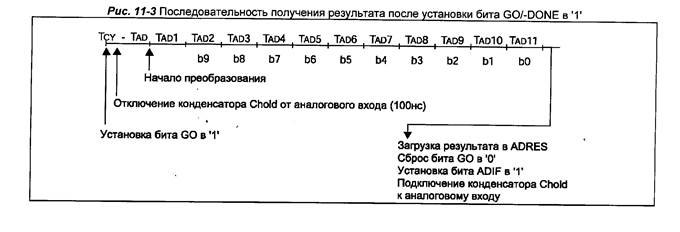

Время получения одного бита результата определяется параметром TAD. Для 10-разрядного результата требуется как минимум 12 TAD. Параметры тактового сигнала для АЦП определяются программно, TAD может принимать следующие значения:

- 2Tosc;

- 8Tosc;

- 32Tosc;

- внутренний RC генератор модуля АЦП (2-6мкс).

Для получения корректного результата преобразования необходимо выбрать источник тактового сигнала АЦП, обеспечивающий время TAD не менее 1,6 мкс.

6.2.2.Настройка аналоговых входов

Регистры ADCON1, TRISA и TRISE отвечают за настройку выводов АЦП. Если выводы микросхемы настраиваются как аналоговые входы, то при этом должны быть установлены соответствующие биты в регистре TRIS. Если соответствующий бит сброшен в "0", вывод микросхемы настроен как цифровой выход со значениями выходных напряжений VOH и VOL.

Модуль АЦП функционирует независимо от состояния битов CHS2:CHS0 и битов TRIS.

6.2.3.. Аналого-цифровое преобразование

Сброс бита GO/-DONE в "0" во время преобразования приведет к его прекращению. При этом регистры результата (ADRESH:ADRESL) не изменят своего содержимого. После досрочного завершения преобразования необходимо обеспечить временную задержку 2TAD. Выдержав требуемую паузу, можно начать новое преобразование установкой бита GO/-DONE в "1".

На рис. 5.2. Показана последовательность получения результата после установки бита GO/-DONE.

6.2.4. Выравнивание результата преобразования

10-разрядный результат преобразования сохраняется в спаренном 16-разрядном регистре ADRESH:ADRESL. Запись результата преобразования может выполняться с правым или левым выравниванием, в зависимости от значения бита ADFM. Не задействованные биты регистра ADRESH:ADRESL читаются как "0". Если модуль АЦП выключен, то 8-разрядные регистры ADRESH и ADRESL могут использоваться как регистры общего назначения.

7.Прерывания микроконтроллеров

PIC16F877 имеют 14 источников прерываний. Регистр INTCON содержит флаги отдельных прерываний, биты разрешения этих прерываний и бит глобального разрешения прерываний.

Если бит GIE (INTCON<7>) установлен в 1, разрешены все немаскируемые прерывания. Если GIE=0, то все прерывания запрещены. Каждое прерывание в отдельности может быть разрешено/запрещено установкой/сбросом соответствующего бита в регистрах INTCON, PIE1 и PIE2. При сбросе микроконтроллера бит GIE сбрасывается в 0.

|

|

|

|

|

Дата добавления: 2014-12-26; Просмотров: 598; Нарушение авторских прав?; Мы поможем в написании вашей работы!