КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Основы микропроцессорной техники 1 страница

|

|

|

|

ЦИФРОВЫЕ И МИКРОПРОЦЕССОРНЫЕ УСТРОЙСТВА

Основы микропроцессорной техники

ЦИФРОВЫЕ И МИКРОПРОЦЕССОРНЫЕ УСТРОЙСТВА

Минск

Основы микропроцессорной техники

ЦИФРОВЫЕ И МИКРОПРОЦЕССОРНЫЕ УСТРОЙСТВА

Володимир Миколайович

Адабашев

Бекір Велішайович

кандидат педагогічних наук

доцент РВНЗ «КІПУ»

зав. кафедрою «Професійної педагогіки та інженерної графіки»

РВНЗ «КІПУ»

Падєрін

інженер – конструктор

кандидат технічних наук

доцент РВНЗ «КІПУ»

Завдання з інженерної та комп’ютерної графіки. Частина 1.

(Основи нарисної геометрії). Навчальний посібник РВНЗ «Кримський інженерно–

-педагогічний університет». Сімферополь, ДІАЙПІ, 2012. - 175 с.: іл.

Коректор: Аширова Ф.М.

Комп'ютерна графіка: Зітляєєв Р.Е.

Комп'ютерний набір: Падєрін О.В.

Видавництво «ДІАЙПІ» 2012 г. Сімферополь.

Тираж 300 прим.

Конспект лекций

В 5 частях

Часть 4

МИНИСТЕРСТВО СВЯЗИ И ИНФОРМАТИЗАЦИИ

РЕСПУБЛИКИ БЕЛАРУСЬ

Учреждение образования

«ВЫСШИЙ ГОСУДАРСТВЕННЫЙ КОЛЛЕД СВЯЗИ»

Кафедра информатики и вычислительной техники

Конспект лекций

для студентов специальностей

2-45 01 03 – Сети телекоммуникаций

2-45 01 02 – Системы радиосвязи, радиовещания и телевидения

В 5 частях

Часть 4

Минск

УДК 81.332

ББК 32.97

Ц75

Рекомендовано к изданию

кафедрой информатики и вычислительной техники

15 января 2008 г., протокол № 4

Составитель

В. И. Богородов, преподаватель высшей категории

кафедры информатики и вычислительной техники

Рецензент

Е. В. Новиков, зав. кафедрой информатики и вычислительной техники,

канд. техн. наук, доцент

| Ц75 | Цифровыеи микропроцессорные устройства: конспект лекций для студентов специальностей 2-45 01 03 – Сети телекоммуникаций, 2-45 01 02 – Системы радиосвязи, радиовещания и телевидения. В 5 ч. Ч. 4: Основы микропроцессорной техники / сост. В. И. Богородов. – Минск: ВГКС, 2008. – 61 с. ISBN 978-985-6866-42-8. Рассматриваются общие принципы построения микропроцессоров и микропроцессорных систем, основные технические данные и структура однокристального микропроцессора К1821ВМ85А. Описываются система прерываний, последовательный ввод-вывод данных, система команд и программирование микропроцессора К1821ВМ85А. Приводятся назначение, схемотехническая реализация, принципы работы простых интерфейсных схем и их программирование, примеры современных интерфейсных микросхем отечественного производства схемотехники КМОП. Предназначено для студентов и преподавателей колледжа. УДК 81.332 ББК 32.97 |

ISBN 978-985-6866-42-8 (ч. 4)

978-985-6866-43-5 ©ВГКС, 2008

Учебное издание

Конспект лекций

для студентов специальностей

2-45 01 03 – Сети телекоммуникаций

2-45 01 02 – Системы радиосвязи, радиовещания и телевидения

В 5 частях

Часть 4

Составитель

Богородов Владимир Ильич

Редактор Е. Б. Левенкова

Компьютерная верстка И. А. Крутая

План 2007/2008 уч. г., поз. 23

Подписано в печать 01.09.2008. Формат 60*84/16.

Бумага офсетная. Гарнитура «Times».

Печать цифровая.

Усл. печ. л. 3,34. Уч.-изд. л. 2,85.

Тираж 95 экз. Заказ 91.

Издатель и полиграфическое исполнение

Учреждение образования

«Высший государственный колледж связи»

ЛИ № 02330/0131902 от 03.01.2007.

220114, Минск, Ф.Скорины, 8/2

ВВЕДЕНИЕ

В четвертой части конспекта лекций рассматриваются основные определения и классификация микропроцессоров, структурные схемы микропроцессоров с «жесткой» и программируемой логикой управления, типовая структурная схема микропроцессорной системы с мультиплексируемой шиной адресов и данных на основе микропроцессора К1821ВМ85А. Описываются структура микропроцессора К1821ВМ85А, назначение узлов и их взаимодействие в процессе считывания и исполнения команд, система прерываний, последовательный ввод-вывод данных, система команд и приемы программирования. Рассматриваются назначение, схемотехническая реализация, принципы работы простых интерфейсных схем и их программирование. Приводятся примеры современных интерфейсных микросхем отечественного производства схемотехники КМОП.

ОБЩИЕ СВЕДЕНИЯ О МИКРОПРОЦЕССОРАХ

Общие сведения о микропроцессорах, основные определения и классификация

Микропроцессором (МП) называют программно-управляемое устройство, осуществляющее процесс обработки цифровой информации и управления им, реализованное в виде одной или нескольких интегральных схем.

Микропроцессорная БИС – интегральная схема с большой степенью интеграции, выполняющая функцию микропроцессора или его части.

Микропроцессорный комплект (МПК) – совокупность микропроцессорных и других интегральных схем, совместимых по архитектуре, конструктивному исполнению и электрическим параметрам, обеспечивающих возможность их совместного применения в составе микропроцессорного вычислительного или управляющего устройства.

Кристалл БИС – часть полупроводниковой пластины, в объеме и на поверхности которой сформированы базовые элементы микропроцессора, межэлементные соединения и контактные площадки.

Аналоговая микросхема – микросхема, предназначенная для преобразования и обработки сигналов, изменяющихся по закону непрерывной функции.

Цифровая микросхема – микросхема, предназначенная для преобразования и обработки сигналов, изменяющихся по закону дискретной функции.

МП является центральным процессорным элементом микропроцессорных систем (МПС) или микроЭВМ.

МПС – совокупность БИС МПК, объединенных в единую структуру и имеющая совместную программу работы.

В МПС организуется процесс выполнения заданной программы, и самые разные задачи решаются путем выполнения команд, свойственных данному МП, т. е., входящих в его систему команд.

Система команд – полный набор всех команд, выполняемых МП.

Вычислительные, контрольно-измерительные и управляющие системы, обрабатывающим элементом которых служит МП, относятся к числу МПС.

Первый МП появился в 1971 году. Это 4-разрядный МП i4004, который стал применяться в микрокалькуляторах. В 1972 году появился 8-разрядный МП i8008, а в 1974 году его улучшенный аналог i8080. Он нашел применение в первых встроенных ЭВМ для управления производственными процессами.

Развитие МП шло по разным направлениям, важнейшее из которых - увеличение разрядности. В этой области в сжатые сроки были достигнуты существенные результаты. Так в 1980 году фирма Motorola выпустила 32-разрядный МП MC68000, а затем Intel и др. Первый 64-разрядный МП i80860 был создан фирмой Intel в 1989 году и т. д. Подавляющее большинство производимых МП являются однокристальными.

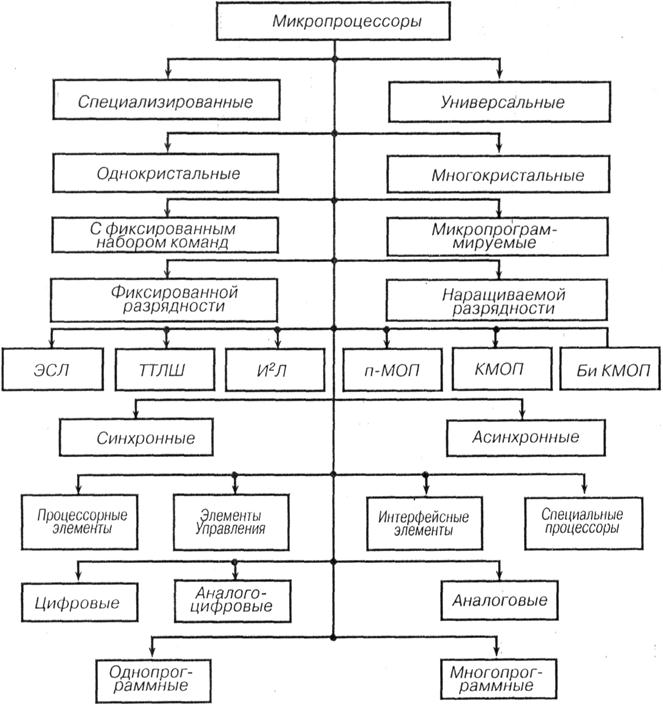

Все многообразие МП БИС можно классифицировать по следующим признакам (рисунок 1):

- по технологии изготовления и схемотехнической элементной базе;

- по разрядности обрабатываемых данных;

- по типу архитектуры;

- по виду временной организации работы БИС;

- по функциональному назначению;

- по виду обрабатываемой информации;

- по области применения;

- по числу одновременно выполняемых программ.

По технологии изготовления и связанной с ней схемотехнической элементной базе различают МП БИС на основе схемотехники типа МОП, биполярной и комбинированной биполярно-полевой (Би-КМОП). Первые поколения МП БИС были реализованы на основе p - (p -МОП) и n -канальных (n -МОП) транзисторов, современные поколения проектируются на основе усовершенствованной КМОП-схемотехники и технологии. Микропроцессорные БИС на основе комбинированной биполярно-полевой (Би-КМОП) технологии обладают наилучшим сочетанием характеристик, обеспечивая высокие быстродействие и нагрузочную способность при сравнительно небольшой, присущей КМОП БИС, мощности потребления. Наибольшее распространение получили МП БИС типа КМОП и Би-КМОП.

По разрядности обрабатываемых данных различают 2-, 4-, 8-, 16-, 32-, 64-разрядные МП БИС и более. При этом обычно имеется в виду максимальная разрядность обрабатываемого информационного слова (операнда), например, 16-разрядный МП может обрабатывать 8-разрядные слова.

По типу архитектуры различают расширяемые (или секционные) и нерасширяемые (или закрытые) микропроцессоры. Расширяемые позволяют увеличивать разрядность обрабатываемых данных (операндов) путем параллельного объединения необходимого числа МП БИС. Так, для обработки 32-разрядного слова можно использовать два 16-разрядных или четыре 8-разрядных секционных МП. Естественно, в структуру таких МП БИС вводятся специальные входы, определяющие позицию секционного МП в микропроцессорной системе – младшая, средняя или старшая. В понятие типа архитектуры также включается тип шинной организации: с раздельными, с совмещенными, с двунаправленными шинами.

Рисунок 1 – Классификация МП БИС

Кроме возможности расширения разрядности схемные решения МП БИС позволяют организовать конвейерные архитектуры, когда обработка потока информации выполняется параллельно.

В зависимости от используемой системы команд различают два типа архитектур: МП CISC -архитектуры (CISC-Complex Instruction Set Computer), выполняющие полный набор команд и МП с RISC -архитектурой (RISC-Reduced Instruction Set Computer), выполняющие не все стандартные, а только наиболее часто используемые в вычислительных и управляющих системах типы команд. Это позволяет существенно сократить аппаратурные затраты, необходимые для реализации таких БИС, а главное, увеличить производительность работы МП БИС.

По виду временной организации работы МП БИС и их комплекты подразделяются на синхронные и асинхронные. Если в синхронных МП БИС время выполнения команд (тактовая частота работы БИС) остается постоянным и независимым от типа команд и величин операндов, то в асинхронных МП БИС начало выполнения каждой следующей команды определяется по сигналу фактического окончания выполнения предыдущей. Синхронные МП БИС отличаются сравнительной простотой организации внутреннего управления, хотя и обеспечивают более низкую по сравнению с асинхронными БИС производительность.

По функциональному назначению различают следующие типы МП БИС: БИС процессорных элементов (ПЭ), БИС микропрограммного управления (МПУ), интерфейсные БИС. Процессорные элементы фактически представляют собой операционное устройство любой микропроцессорной системы, которое выполняет полный набор операций. БИС МПУ, входящие в состав большинства микропроцессорных комплектов, предназначены для формирования последовательности адресов внешней памяти команд (микрокоманд) на основании кодов обрабатываемых команд, значений вырабатываемых процессорным элементом сигналов, сигналов внешних устройств, запросов прерываний и т. д. Интерфейсные МП БИС предназначены для организации связи БИС ПЭ и МПУ с внешними устройствами и друг с другом в составе любой микропроцессорной системы. Здесь, в свою очередь, различают такие их типы, как магистральные приемопередатчики (МПП), магистральные коммутаторы (МК), программируемые системные контроллеры (ПСК), программируемые каналы ввода-вывода (ПКВВ), многоцелевые буферные регистры, контроллеры прямого доступа к памяти (КПДП) и др.

По виду обрабатываемой информации МП БИС могут быть разделены на цифровые, аналоговые и комбинированные (цифро-аналоговые и аналого-цифровые). В цифровых МП БИС прием, обработка и выдача результата осуществляется в цифровой форме. В аналоговых МП БИС информация поступает на входы в аналоговой форме, затем преобразуется в цифровую с помощью встроенных средств и в таком виде обрабатывается МП. Результаты обработки снова преобразуются в аналоговую форму и поступают на выход БИС.

По области применения различают два больших класса МП БИС - специализированные и универсальные. Специализированные МП БИС предназначены для реализации лишь определенных классов микропроцессорных систем и устройств – цифровой обработки сигналов (ЦОС), систем решения задач радиолокации, гидродинамики, кинофототехники, медицинской электроники, автомобильной электроники и т. д. Универсальные МП БИС могут быть использованы в различных системах вычислительной техники и автоматики. Основное достоинство специализированных МП БИС – их высокая производительность на конкретных задачах.

По числу одновременно выполняемых программ МП БИС разделяются на одно- и многопрограммные. В однопрограммных МП БИС в один момент времени выполняется одна программа, переход к исполнению следующей программы (последовательности команд) происходит только после завершения предыдущей. В мультипрограммных МП БИС могут одновременно выполняться несколько программ.

Различают три группы параметров МП БИС: функциональные, электрические и динамические.

Основным функциональным параметром МП БИС является функциональная мощность К, измеряемая количеством операций, выполняемых в единицу времени (например, MIPS – миллион инструкций в секунду). В зависимости от типа операций различают несколько значений функциональной мощности, например: в формате операций регистр-регистр KRR, в формате операций регистр-память KRM и др.

Из других функциональных параметров используют разрядность слова адреса, разрядность слова данных, разрядность слова команды, число команд (микрокоманд), реализуемое МП БИС.

Электрические параметры МП БИС имеют размерность напряжения, тока и мощности и определяют основные технические характеристики микропроцессорных систем (см. параметры интегральных ЛЭ).

Динамические параметры МП БИС определяются по временной диаграмме (ВД), которая определяет развернутую во времени последовательность подачи на МП БИС управляющих воздействий, информационных, синхронизирующих и вспомогательных сигналов, а также последовательность считывания из БИС результатов обработки. На ВД приводится вид этих сигналов, указывают допустимые временные соотношения между ними, допустимые длительности и т. д.

Общая структурная схема микропроцессора

Как и любое сложное цифровое устройство, МП может быть представлен соединением двух устройств – операционного и управляющего. Исходя из этого, общая структурная схема МП имеет вид, представленный на рисунке 2.

Рисунок 2 – Общая структурная схема микропроцессора

В ОУ производится непосредственное выполнение операций. ОУ содержит узлы следующих типов: регистры, сумматоры, каналы передачи данных, мультиплексоры, производящие переключение каналов передачи, дешифраторы, шифраторы и др.

УУ координирует работу узлов ОУ, формируя управляющие сигналы Y1, Y2, …, Yn в определенной временной последовательности. УУ обеспечивает в определенных узлах ОУ требуемые для выполнения операции действия.

Любая операция, выполняемая в узлах ОУ, делится на последовательность элементарных действий, называемых микрооперациями. К микрооперациям относятся:

- установка регистра в некоторое состояние;

- пересылка содержимого одного регистра в другой;

- суммирование содержимого двух регистров;

- инвертирование содержимого регистра и т. д.

Указанные микрооперации выполняются не во всех узлах ОУ. Каждая микрооперация выполняется под действием одного управляющего сигнала на выходе УУ, поэтому УУ имеет число управляющих цепей, равное общему количеству микроопераций, выполняемых в ОУ.

В одном и том же тактовом периоде может выполняться несколько микроопераций, осуществляемых в разных узлах ОУ. В этом случае управляющие сигналы поступают в несколько цепей.

Набор управляющих сигналов, обеспечивающих выполнение одной или нескольких микроопераций в одном и том же тактовом периоде, называется микрокомандой (МК), следовательно, управляющие сигналы являются микрокомандами. Последовательность МК, обеспечивающая выполнение одной операции, называется микропрограммой.

Иногда последовательность действий при выполнении операций зависит от состояния узлов ОУ или, иначе, от некоторых признаков, связанных с результатами микроопераций. Такие признаки X1, X2, …, Xp выдаются из ОУ и поступают в УУ. Некоторые признаки Xp + 1, …, Xs могут поступать извне, определяя порядок работы МП. Формируя управляющие сигналы УУ обязано в соответствующие тактовые периоды ориентироваться на признаки. В ОУ поступают данные и выдаются данные.

Два подхода в построении УУ микропроцессора

При проектировании УУ МП используются два принципа:

- принцип схемной или «жесткой» логики;

- принцип программируемой логики.

При построении УУ МП по принципу схемной логики можно подобрать набор микросхем малой и средней степени интеграции. Затем определяется схема соединения выводов микросхем, обеспечивающая генерацию требуемой последовательности МК.

Достоинством принципа схемной логики является возможность достижения максимального быстродействия при заданной технологии элементной базы.

Недостатки принципа схемной логики:

- всякое изменение последовательности МК требует демонтажа старого УУ и монтажа нового, т.е. принцип схемной логики не обеспечивает гибкости применения;

- экономически не выгодно использовать последние достижения микроэлектроники – БИС и СБИС, так как разработка специализированных БИС обходится дорого.

При использовании принципа программируемой логики в УУ используется память, хранящая микропрограммы, т.е. последовательности МК.

Считывая из памяти МК и подавая их в управляющие цепи, УУ обеспечивает их выполнение в ОУ. В этом случае МП может быть выполнен в виде некоторого универсального устройства, например БИС. Изменение функционирования этого устройства обеспечивается помещением в память новой микропрограммы, т.е. этот метод обеспечивает гибкость применения. Однако при использовании принципа программируемой логики снижается быстродействие МП, так как требуется дополнительное время для формирования адресов МК и их считывания из памяти.

Структурная схема МП со схемной логикой управления

Структурная схема МП со схемной логикой управления представлена на рисунке 3.

Рисунок 3 – Структурная схема МП со схемной логикой управления

УУ содержит k устройств управления операциями (логических схем). Для выбора одной из них дешифратор декодирует операционное поле команды, поступающей из основной памяти (ОП). В зависимости от кода операции, указанного в команде, выбирается УУ операцией, которое выдает на входы ОУ нужную последовательность управляющих сигналов.

Принцип микропрограммного управления. Структурная схема МП на основе программируемой логики управления

В каждом тактовом периоде из УУ выдается на ОУ некоторая кодовая комбинация управляющих сигналов. Если число управляющих сигналов n, то кодовая комбинация n-разрядная и каждый разряд показывает присутствует ли управляющий сигнал в соответствующей управляющей цепи, например, 0010…1. Такие кодовые комбинации можно хранить в так называемой управляющей памяти (УП) или микропроцессорной памяти (МПП) и тогда МП имеет структуру, представленную на рисунке 4.

Рисунок 4 – Структурная схема МП с программируемой логикой управления

Микропрограммы различных операций хранятся в УП. Для выполнения каждой МК необходимо задать ее адрес и прочитать из УП.

Считанная из УП общая МК может быть разбита на две МК. МК ОУ определяет функционирование узлов ОУ в данном тактовом периоде. МК БМУ содержит поле адреса и поле условных переходов и задает способ формирования адреса очередной МК.

Если микропрограмма является линейной последовательностью МК, то задавать адрес каждой следующей МК можно счетчиком, предварительно загрузив в него начальный адрес микропрограммы. Однако линейные микропрограммы встречаются редко. Чаще они представляют собой последовательности с ветвлениями и с циклами. В таком случае адрес следующей МК должен определяться специальным образом. Для этой цели служит БМУ. Исходными данными для определения адреса следующей МК обычно служит адрес текущей МК, специальные поля текущей МК (МК БМУ), а также совокупность признаков (условий), поступающих от ОУ и из внешних устройств.

Рассмотрим структурную схему УУ МП с программируемой логикой управления (рисунок 5).

Рисунок 5 – Структурная схема УУ МП с программируемой логикой управления

В ячейках ПЗУ МК одной микропрограммы с номерами, отличающимися на единицу, имеют адреса, также отличающиеся на единицу. Поэтому при последовательной выборке МК удобно использовать суммирующий счетчик СТ (рисунок 5). Исходное состояние счетчика устанавливается внешним сигналом F (код операции текущей команды) при обращении к очередной микропрограмме и соответствует адресу первой МК этой микропрограммы.

Если МК не содержит микроопераций «условный переход» и «безусловный переход», то управляющий сигнал из схемы определения адреса МК увеличивает код на выходах счетчика на единицу – происходит выборка МК из соседней ячейки ПЗУ.

Если очередная МК содержит микрооперацию «безусловный переход», то адрес следующей МК из схемы определения адреса МК параллельно переписывается в счетчик (адресом является содержимое поля адреса текущей МК).

Если очередная МК содержит микрооперацию «условный переход», то адрес следующей МК определяется в зависимости от значения признаков X1, X2, …, Xm, поступающих из ОУ МП, и также параллельно переписывается в счетчик. При этом младший разряд поля адреса текущей МК замещается значением признака, т. е. происходит модификация (изменение) адреса следующей МК. В этом случае очередная МК считывается с одной из двух соседних ячеек управляющей памяти, адреса которых отличаются значениями только младших разрядов, например:

|

Код с выходов счетчика преобразуется дешифратором DC в сигнал, под действием которого из ПЗУ считывается нужная МК. Эта МК запоминается в регистре RG МК и поступает на выход УУ МП в виде управляющих сигналов Y1, Y2, …, Yn.

Временная диаграмма работы МП с программируемой логикой представлена на рисунке 6.

Рисунок 6 – Временная диаграмма работы МП

В момент t1 (рисунок 6) БМУ выдает в управляющую память адрес очередной МК. Через некоторое время (от десятков до сотен наносекунд) завершается процесс чтения МК в управляющей памяти и в момент t2 на выходах памяти появится требуемая МК. С момента t2 в ОУ начинается выполнение предусмотренной в МК микрооперации и завершится к моменту t3.

До окончания выполнения микрооперации БМУ не может формировать адрес следующей МК, поскольку это зависит от признаков, т. е. от результатов микрооперации. Поэтому БМУ формирует адрес следующей МК от момента t3 до t4.

В данном построении МП его блоки функционируют не одновременно, а последовательно во времени и длительность тактового периода T должна быть не меньше суммы времен, необходимых для выполнения действий в блоках. Для повышения быстродействия МП используется конвейерный способ считывания и исполнения МК.

Типовая структурная схема МПС с мультиплексируемой шиной адресов и данных

Практически всегда структура МПС является магистрально-модульной. В такой структуре имеется группа магистралей (шин), к которым подключаются различные модули (блоки), обменивающиеся между собой информацией поочередно, в режиме разделения времени.

Термин «шины» относится к совокупности цепей (линий) по которым передается однотипная информация. Число цепей определяет разрядность шины.

Типична трехшинная структура МПС с шинами адресов ША, данных ШД и управления ШУ. Наряду с русскими терминами применяются английские AB (Address Bus), DB (Data Bus) и CB (Control Bus).

На рисунке 7 показана структура микропроцессорной системы с МП, имеющим мультиплексируемую шину адресов/данных (например, с МП К1821ВМ85А). Линии A15–8 являются адресными, через них в систему передается старший байт 16-разрядного адреса. В эту шину включен формирователь на постоянно открытом по входу разрешения EN буферном регистре ИР82, обеспечивающем работу шины на нагрузку, образуемую внешними цепями. Собственной нагрузочной способности у выводов МП, как правило, не хватает. Линии AD7–0 мультиплексируются. Вначале они передают младший байт адреса, признаком чего служит наличие сигнала ALE (Address Latch Enable), загружающего этот байт в регистр ИР82.

Рисунок 7 – Структура микропроцессорной системы

После загрузки регистра сигнал ALE снимается, и содержимое регистра остается неизменным вплоть до новой загрузки в следующем цикле работы процессора. Так формируется 16-разрядная шина адреса, содержащая адрес A15–0. Этот адрес используется блоками постоянной и оперативной памяти ROM и RAM. Адресация портов ввода и вывода данных требует восьмиразрядного адреса, что соответствует возможности работы не более чем с 256 портами каждого из типов. Адрес портов можно снимать с любой половины адресной шины (во взятом для примера МП состояния обоих полушин адреса при адресации портов дублируются).

После передачи младшего байта адреса шина AD7–0 отдается для передачи данных. Эти передачи двунаправлены, направление задается буфером данных BD в зависимости от сигнала T (Transmit). При активном состоянии сигнала чтения  (

( ) данные передаются справа налево, при пассивном – в обратном направлении. К шине данных подключены информационные выводы всех модулей МПС.

) данные передаются справа налево, при пассивном – в обратном направлении. К шине данных подключены информационные выводы всех модулей МПС.

Выводы X1 и X2 служат для подключения кварцевого резонатора или иных контуров, задающих частоту тактовому генератору, расположенному в МП. Тактирование системы производится на частоте, равной половине частоты резонанса кварца или иного контура, поскольку генератор работает на триггер, с которого снимаются сигналы тактирования модулей МПС, а триггер делит частоту на 2. Вход  является входом асинхронного сброса, приводящим МП в исходное состояние. Сигнал L-активный. Сброс может быть осуществлен замыканием ключа K и автоматически происходит при включении питания UCC. В этом случае благодаря цепочке RC напряжение на входе

является входом асинхронного сброса, приводящим МП в исходное состояние. Сигнал L-активный. Сброс может быть осуществлен замыканием ключа K и автоматически происходит при включении питания UCC. В этом случае благодаря цепочке RC напряжение на входе  нарастает постепенно, и в течение некоторого времени после включении питания остается низким (ниже порогового), что равноценно подаче сигнала

нарастает постепенно, и в течение некоторого времени после включении питания остается низким (ниже порогового), что равноценно подаче сигнала  .

.

|

|

|

|

|

Дата добавления: 2015-03-29; Просмотров: 2021; Нарушение авторских прав?; Мы поможем в написании вашей работы!