КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Тема: Етапи виконання команди. Типи і структура даних. Взаємодія основних пристроїв ЕОМ

|

|

|

|

Лабораторна робота №4

Стекова адресація

Останній метод адресації, що ми розглянемо в цій главі, — стекова адресація. Іноді стек ще називають магазинним списком (pushdown list) і списком з дисципліною обслуговування в зворотному порядку (LIFO-list). Для розміщення стека в пам'яті резервується спеціальна область. Елементи додаються у вершину стека таким чином, що в кожен даний момент часу виділена для стека область пам'яті виявляється заповненою тільки частково. Зі стеком зв'язується покажчик адреси комірки, що знаходиться у вершині стека (його прийнято називати покажчиком стека). У деяких процесорах два верхніх елементи стека розміщаються не в оперативній пам'яті, а в спеціальних регістрах, і в такому випадку покажчик стека зберігає адресу не самого верхнього елемента, а третього зверху. Покажчик стека, як правило, розміщається в окремому регістрі процесора. Таким чином, посилання на верхню комірку стека в пам'яті є, фактично, варіантом непрямої адресації через регістр.

Стекова адресація — одна з форм неявної адресації. При цьому в машинну команду не потрібно включати посилання на операнд, оскільки кодом операції неявно передбачене виконання дій з даними, що знаходяться у вершині стека.

Контрольні питання:

1. Критерії розробки системи команд.

2. Безпосередня адресація (символічний запис, призначення, переваги та недоліки).

3. Пряма адресація.

4. Непряма адресація.

5. Реєстрова адресація.

6. Непряма через регістр адресація.

7. Адресація зі зсувом, її підвиди.

8. Стекова адресація.

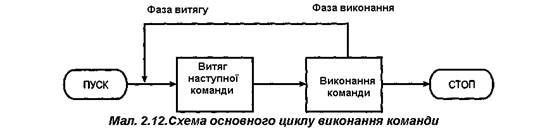

На початку кожного циклу з пам'яті витягається чергова команда, адреса якої заздалегідь готується в лічильнику команд - PC. При звертанні до PC адреса в ньому автоматично збільшується і, таким чином, відразу підготовлюється до наступного циклу, оскільки команди в пам'яті зберігаються в природному порядку, тобто в послідовних комірках. Нехай, наприклад, у комп'ютері команда займає одне 16-розрядне слово пам'яті. Припустимо, що в PC знаходиться число 300. Процесор витягає команду, що знаходиться в комірці пам'яті за адресою 300, а в PC при цьому автоматично встановлюється код 301. У наступних циклах будуть витягнуті команди по наступним адресам 301, 302, 303 і т.д.

Зчитана команда міститься в регістр команд IR (Instruction Register).Частина бітів коду команди являє собою код операції, щовизначає, яка саме операція повинна бути виконана процесором. Виконуючи задану операцію, процесор буде робити елементарні дії, які можна розділити на чотири категорії:

• передача "процесор — пам'ять": дані передаються з процесора в пам'ять або з пам'яті в процесор;

• передача "процесор — модуль вводу-виводу": дані передаються з процесора в один з модулів виводу або навпаки;

• обробка даних: процесор виконує задану арифметичну або логічну операцію над даними;

• керування: команда змінює природний порядок виконання команд програми.

Крім звертання до комірок пам'яті в команді може бути задана й операція вводу-виводу. На мал. 4.2 представлена діаграма станів при виконанні команди. Варто враховувати, що при виконанні визначених команд деякі стани можуть "обходитися", а в інші — система може попадати кілька разів протягом того самого циклу обробки команди. Зміст представлених на діаграмі станів наступний.

• Обчислення адреси команди (IAC •— Instruction Address Calculation). При природному порядку виконанні команд програми адреса наступної команди утвориться в результаті додавання константи до адреси поточної команди. Якщо, наприклад, довжина команди 16 розрядів, і таку ж розрядність мають слова в пам'яті, то адреса кожної чергової команди відрізняється від адреси попередньої на 1. Якщо ж оперативна пам'ять організована таким чином, що адресованою одиницею даних є 8-розрядний байт, то адреса в PC має збільшуватися на 2.

• Витяг команди (IF — Instruction Fetch). Зчитування команди з комірки пам'яті за адресою, заданою в PC, у регістр процесора.

• Розшифровка коду операції (IOD —Instruction Operation Decoding). Аналіз коду операції і з'ясування типу викликаної операції, кількості і типів використанних у ній операндів (чи операнда).

• Обчислення адреси операнда (ОАС — Operand Address Calculation). Якщо в операції використовуються операнди, що зберігаються в пам'яті або передаються через підсистему вводу-виводу, то на цій фазі визначаються їх "фізичні" адреси.

• Витяг операнда (OF — Operand Fetch). Зчитування операнда з заданої комірки пам'яті чи з модуля вводу-виводу.

• Обробка даних (DO — Data Operation). Виконання операції, передбаченої кодом операції.

• Збереження результату (OS — Operand Store). Запис результату операції в задану комірку пам'яті чи передача в модуль вводу-виводу.

Для тих станів, що показані у верхній частині діаграми, характерним є обмін даними між процесором і пам'яттю або яким-небудь модулем вводу-виводу. Стан в нижній частині діаграми відповідає внутрішнім операціям ЦП. У стан ОАС система може попадати двічі, оскільки в процесі виконання команди може знадобитися читання операнда (чи операндів) і/або запис результату, але суть виконуваних у цьому стані дій не залежить від того, як далі буде використовуватися обчислена.

У системі команд деяких комп'ютерів маються команди, що задають операції над векторами (одномірними числовими масивами) чи рядками (одномірними масивами символів). Такі операції також "вписуються" у діаграму станів, представлену на мал. 4.2, але при цьому для кожного елемента масиву приходиться повторно проходити по кільцю ОАС, OF, DO, OAC, OS.

Типи і структура даних.

Для багатьох комп'ютерних систем основною задачею є обробка фінансових, промислових, наукових, технічних і інших даних. На рівні архітектури команд використовуються різні типи даних.

Основним питанням є питання про те, чи існує апаратна підтримка для конкретного типу даних. Під апаратною підтримкою мається на увазі, що одна чи кілька команд очікують дані у визначеному форматі і користувач не може брати інший формат.

Розглянемо бухгалтерську фірму, що тільки що уклала договір на перевірку федерального боргу. 32-бітна арифметика тут не підійде, оскільки числа перевищують 232 (близько 4 мільярдів). Одне з можливих рішень — використовувати два 32-бітних цілих числа для представлення кожного числа, тобто всі 64 біта. Якщо машина не підтримує такі числа з подвоєною точністю, то всі арифметичні операції над ними повинні виконуватися програмним забезпеченням, але ці дві частини можуть розташовуватися в довільному порядку, оскільки для апаратного забезпечення це не важливо. Це приклад типу даних без апаратної підтримки і, отже, без апаратної реалізації.

Числові типи даних

Типи даних можна розділити на дві категорії: числові і нечислові. Серед числових типів даних головними є цілі числа. Вони бувають різної довжини: зазвичай 8,16,32 і 64 біта. Цілі числа застосовуються для підрахунку різних предметів (наприклад, вони показують, скільки на складі мається викруток), для ідентифікації різних об'єктів (наприклад, банківських рахунків), а також для інших цілей. У більшості сучасних комп'ютерів цілі числа зберігаються в двійковому записі, хоча в минулому використовувалися й інші системи.

Деякі комп'ютери підтримують цілі числа і зі знаком, і без знака. У цілому числі без знака немає знакового біта, і всі біти містять дані. Цей тип даних має перевагу: у нього є додатковий біт, тому 32-бітне слово може містити ціле число без знака від 0 до 232-1 включно. Двійкове ціле число зі знаком, навпаки, може містити числа тільки до 231-1, алезате включає і негативні числа.

Для вираження нецілих чисел (наприклад, 3,5) використовуються числа з крапкою, що плаває. Їхня довжина складає 32,64, а іноді і 128 бітів. У більшості комп'ютерів є команди для виконання операцій з числами з крапкою, що плаває. У багатьох комп'ютерах маються окремі регістри для цілочисельних операндів і для операндів із крапкою, що плаває.

Нечислові типи даних

Хоча найперші комп'ютери працювали в основному з числами, сучасні комп'ютери часто використовуються для нечислових додатків, наприклад, для обробки текстів чи керування базами даних. Для цих додатків потрібні інші, нечислові, типи даних. Вони часто підтримуються командами рівня архітектури команд.

Найбільш розповсюдженими символьними кодами є ASCII і UNICODE. Вони підтримують 7-бітні і 16-бітні символи відповідно.

На рівні команд часто маються особливі команди, призначені для операцій з ланцюжками символів. Ці ланцюжки іноді розмежовуються спеціальним символом наприкінці. Замість цього для визначення кінця ланцюжка може використовуватися поле довжини ланцюжка. Команди можуть виконувати копіювання, пошук, редагування ланцюжків і інші дії.

Крім того, важливі значення булевої алгебри. Цих значень дві: істина і неправда. Теоретично булеве значення може представляти один біт: 0 — неправда, а 1 — істина (чи навпаки). На практиці ж використовується байт чи слово, оскільки окремі біти в байті не мають власних адрес, і отже, до них важко звертатися. У звичайних системах застосовується наступна угода: 0 означає неправду, а все інше означає істину.

Останній тип нечислових даних — це покажчики, що являють собою машинні адреси.

Типи даних процесора Pentium II

Pentium II підтримує двійкові цілі числа зі знаком, цілі числа без знака, числа двоїчно-десяткової системи числення і числа з крапкою, що плаває, по стандарту IEEE 754 (табл. 4.1). Ця машина є 8-, 16-розрядної й оперує з цілими числами такої довжини. У неї маються численні арифметичні команди, булеві операції й операції порівняння. Операнди необов'язково повинні бути вирівняні в пам'яті, але якщо адреси слів кратні 4 байтам, то спостерігається більш висока продуктивність.

Таблиця 4.1 Числові типи даних процесора Pentium II. Типи, що підтримуються, відзначені хрестиком (х)

| Тип | 8 бітів | 16 бітів | 32 бітів | 64 бітів | 128 бітів | |

| Цілі числа зі знаком | х | х | х | - | - | |

| Цілі числа без знака | х | х | х | - | - | |

| Двоїчно-десяткові цілі числа | х | - | - | - | - | |

| Числа з крапкою, що плаває | - | - | х | х | - | |

Pentium II також може маніпулювати 8-розрядними символами ASCII; існують спеціальні команди для копіювання і пошуку ланцюжків символів. Ці команди використовуються і для ланцюжків, довжина яких відома заздалегідь, і для ланцюжків, наприкінці яких розташован спеціальний маркер.

Типи даних машини UltraSPARC II

UltraSPARC II підтримує широкий ряд форматів даних (табл. 4.2). Ця машина може підтримувати 8-, 16-, 32- і 64-бітні цілочисельні операнди зі знаком і без знака. Цілі числа зі знаком використовують додатковий код. Крім того, маються операнди з крапкою, що плаває, по 32,64 і 128 бітів, що відповідають стандарту IEEE 754 (для 32-бітних і 64-бітних чисел). Двоїчно-десяткові числа не підтримуються. Всі операнди повинні бути вирівняні в пам'яті.

Таблиця 4.2 Числові типи даних комп'ютера UltraSPARC II

| Тип | 8 бітів | 16 бітів | 32 бітів | 64 бітів | 128 бітів | |

| Цілі числа зі знаком | х | Х | х | х | - | |

| Цілі числа без знака | - | - | - | - | - | |

| Двоїчно-десяткові цілі числа | - | - | - | - | - | |

| Числа з крапкою, що плаває | - | - | х | x | - |

Взаємодія основних пристроїв ЕОМ

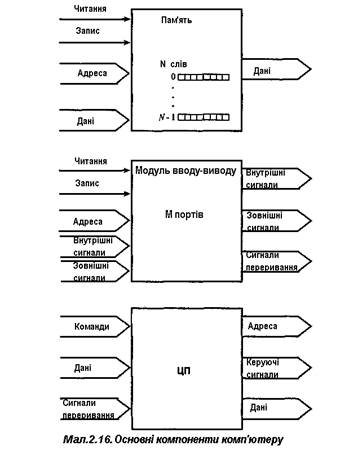

Розглядаючи конструкцію підсистеми взаємодії основних компонентів комп'ютера — процесора, пам'яті і модулів вводу-виводу, — ми в першу чергу повинні звернути увагу на характер операцій обміну інформацією, який специфічний для кожного з цих компонентів (мал. 2.16).

• Оперативна пам'ять. В переважній більшості випадків можна розглядати модуль пам'яті як сукупність слів однакової довжини. Якщо таких слів у модулі пам'яті N, то кожне з них має свій унікальний числовий атрибут — адреса (ПРО, 1,..., N-1). Порцію даних довжиною в одне слово можна одним прийомом записати в пам'ять чи зчитати її з пам'яті. Існують спеціальні керуючі сигнали, що вказують, яка саме операція — запис чи читання — повинна бути виконана, а параметрами обох видів операції звертання до пам'яті є адреса комірки.

•Модуль вводу-виводу. Характер виконуваних їм операцій не відрізняється від характеру операцій блоку оперативної пам'яті — це операції запису і читання. Більш того, один модуль вводу-виводу може контролювати роботу декількох пристроїв, а значить їх необхідно якимсь чином ідентифікувати при виконанні операції, тобто мати деякий аналог адреси комірки пам'яті. Цим аналогом є порт вводу-виводу. Модуль вводу-виводу має лінії прийому інформації від зовнішніх пристроїв її передачі і здатен, крім того, передавати в процесор сигнали запиту переривань.

•Процесор. Процесор зчитує з пам'яті команди і дані, записує в пам'ять результати обробки і формує сигнали, що керують роботою всієї системи. Він також одержує сигнали запиту переривань.

Приведений нижче список визначає, яка інформація повинна циркулювати по лініях підсистеми взаємодії. На підсистему покладається задача забезпечення виконання наступних видів операцій передачі даних.

•З пам'яті в процесор. Процесор зчитує команду чи елемент даних з пам'яті.

•З процесора в пам'ять. Процесор записує елемент даних у пам'ять.

•З модуля вводу-виводу в процесор. Процесор зчитує дані з зовнішнього пристрою через модуль вводу-виводу.

•З процесора в модуль вводу-виводу. Процесор посилає дані в зовнішній пристрій через модуль вводу-виводу.

•З модуля вводу-виводу в пам'ять чи з пам'яті в модуль вводу-виводу. Ці два варіанти операцій здійснюються у випадку, якщо модулю вводу-виводу надана можливість працювати в режимі прямого доступу до пам'яті й обмінюватися даними з блоком пам'яті, минаючи процесор.

У процесі розвитку обчислювальної техніки було випробувано кілька варіантів структур підсистеми взаємодії між компонентами, але зрештою перевага була віддана структурам на основі багатоканальних магістралей. Далі, ми розглянемо різні варіанти таких структур.

Магістраллю2 (bus) — стосовно до інформаційних систем інформаційної магістралі — є сукупність електричних зв'язків і обслуговуючих електронних приладів (обрамлення), що забезпечують обмін інформацією між двома чи більш пристроями. Характерною рисою інформаційної магістралі є спільне використання її безліччю взаємодіючих один з одним пристроїв. Сигнали, передані по магістралі одним пристроєм, доступні всім іншим, підключеним до цієї магістралі. Якщо в той самий час два пристрої спробують передавати сигнали по магістралі, то відбудеться накладення цих сигналів один на одний і їхнє перекручування. Отже, у конструкції магістралі (у її електронному обрамленні) повинні бути передбачені засоби, що забезпечують у кожен момент часу передачу по магістралі сигналів тільки від одного з підключених до неї пристроїв.

Як правило, до складу магістралі входить безліч електричних зв'язків — ліній магістралі, — по кожному з яких може передаватися двійковий сигнал, тобто сигнал, що має два чітко помітних рівні — "лог. О" і "лог. 1". По одній лінії може передаватися розгорнута в часі послідовність двійкових сигналів. Часто сигнали передаються по декількох лініях одночасно і сприймаються в сукупності. У такому випадку говорять про рівнобіжну передачу двійкових сигналів. Наприклад, можна по восьми лініях паралельно передати один 8-розрядний байт інформації.

У конструкції комп'ютерної системи може бути передбачено кілька магістралей, що забезпечують комунікацію між компонентами на різних рівнях ієрархії системи. Магістраль, що зв'язує основні компоненти (компоненти вищого рівня ієрархії — процесор, пам'ять, модулі вводу-виводу), називається системною магістраллю (system bus). Більшість розповсюджених на сьогоднішній день варіантів структури підсистеми взаємодії компонентів комп'ютерної системи засновано на використанні однієї чи навіть декількох системних магістралей.

Структура магістралі

Як правило, системна магістраль включає від 50 до 100 окремих ліній, по кожній з який передаються сигнали визначеного функціонального призначення. Хоча існує безліч варіантів конструкції системної магістралі, лінії будь-якої магістралі можна розділити на три великих групи (мал. 2.17): лінії даних, адреси і керуючі сигнали. Крім того, до складу магістралі можуть входити і силові лінії живлення, що забезпечують енергопостачання підключених модулів.

У російськомовній технічній літературі часто застосовується еквівалентний термін шина, що є калькою з англійського bus. На наш погляд, термін магістраль більш вдало передає призначення цього компонента інформаційної системи, оскільки асоціюється з засобом комунікації, що володіє значною пропускною здатністю, у той час як термін шина асоціюється з монолітним провідником великої провідності.

По лініях даних передаються сигнали, що відповідають інформації, переданої одним з підключених модулів. У сукупності лінії даних називаються магістраллю даних. Як правило, кількість ліній магістралі даних кратно 8 — 8, 16 або 32. Цей параметр прийнято називати розрядністю або шириною (width) магістралі. Оскільки в окремий момент часу по кожній лінії можна передавати тільки один біт інформації, розрядність магістралі характеризує обсяг даних, переданих по ній у кожен момент часу, і є, таким чином, ключовим фактором, що впливає на інформаційну продуктивність усієї системи. Наприклад, якщо розрядність магістралі даних дорівнює 8, а машинна команда має довжину 16 розрядів, то протягом фази витягу кожного циклу обробки команди процесору доведеться двічі звертатися до модуля пам'яті.

По лініях адреси передаються сигнали, що у сукупності визначають джерело або приймач даних, виставлених на лінії даних. Якщо, наприклад, процесор має намір прочитати слово (8-, 16- чи 32-розрядне) з визначеної комірки пам'яті, він виставляє двійковий код адреси цієї комірки на лінії адреси. Зовсім очевидно, що розрядність магістралі адреси визначає максимальний обсяг пам'яті, адресованої по такій магістралі. Більш того, порти модулів вводу-виводу адресуються по цих же лініях адреси. Як правило, формат коду адреси порту вибирається таким чином, що старші розряди задають визначений модуль вводу-виводу з підключених до магістралі, а молодші — адреси в пам'яті або порт у модулі вводу-виводу. Наприклад, якщо магістраль адреси 8-розрядна, то коди 0111111 і менші задають адреси комірок у модулі пам'яті (модулі з адресою 0), а коди, починаючи з 10000000, задають порти пристроїв вводу-виводу, що знаходяться під керуванням модуля вводу-виводу (модуля з адресою 1). Лінії керуючих сигналів використовуються для керування доступом до ліній даних і адреси. Оскільки інформація, передана по магістралях адреси і даних, надходить на всі підключені модулі, повинен існувати деякий компонент, що спостерігає за порядком у цьому "господарстві". Керуючі сигнали, по-перше, несуть визначене інформаційне навантаження, тобто передають команди, що наказують, як надходити з іншими сигналами в даній ситуації, а по-друге, синхронізують процеси

Коли деякий пристрій, підключений до магістралі, формує на окремій групі ліній (або даних адреси) набір сигналів, що відповідають визначеному двійковому коду, ми будемо говорити, що даний пристрій виставляє такий-то код на таку-то групу ліній у магістралі. Сигнали синхронізації визначають ті моменти (чи інтервали) часу, коли код, виставлений на лінії даних і адреси, можна вважати достовірним. Керуючі сигнали задають виконувані операції. Типовий набір керуючих сигналів наступний:

•Memory write (запис у пам'ять) — ініціює запис коду, виставленого на лінії даних у пам'ять за адресою, код якого виставлений на лінії адреси;

•Memory read (читання з пам'яті) — ініціює читання з комірки пам'яті за адресою, код якої виставлений на лінії адреси, прочитаний код виставляється на лінії даних;

•I/O write (запис у пристрій вводу-виводу) — ініціює запис коду, виставленого на лінії даних у пристрій вводу-виводу, код адреси якого (адреса модуля вводу-виводу і номер порту пристрою) виставлений на лінії адреси;

•I/O read (читання з пам'яті) — ініціює зчитування з порту пристрою вводу-виводу, код адреси якого (адреса модуля вводу-виводу і номер порту пристрою) виставлений на лінії адреси, прочитаний код виставляється на лінії даних;

•Transfer ACK (підтвердження передачі) — сигналізує, що дані зчитані з шини модулем, якому вони призначалися командою запису, чи виставлені на шину модулем, від якого вони викликані командою читання;

•Bus request (запит керування магістраллю) — сигналізує, що якийсь модуль просить надати в його розпорядження ресурси магістралі;

•Bus grant (надання керування магістраллю) — сигналізує, що модулю, що передав сигнал Bus request, надане право розпоряджатися ресурсами магістралі;

•Interrupt request (запит переривання) — сигналізує, що відбулася подія, що вимагає переривання поточної програми;

•Interrupt ACK (підтвердження переривання) — сигналізує, що запит переривання сприйнятий;

•Clock (синхронізація) — використовується для синхронізації виконуваних операцій;

•Reset (загальне скидання) — використовується для установки всіх модулів, підключених до магістралі, у вихідний стан.

Функціонує магістраль у такий спосіб. Коли один з модулів "бажає" передати дані іншому, він повинний виконати дві операції:

1) одержати право користатися магістраллю;

2) передати дані по магістралі.

Коли якому-небудь модулю необхідно одержати дані від іншого модуля, він також повинен виконати дві операції:

1) одержати право скористатися магістраллю;

2) передати запит іншому модулю, виставивши відповідний код на адресних лініях і сформувавши сигнали на визначених лініях керуючих сигналів.

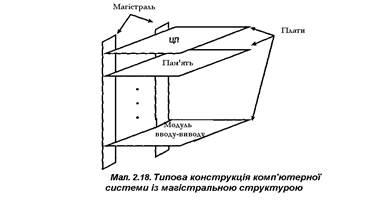

Фізично (конструктивно) системна магістраль являє собою безліч провідників, підключених до однойменних контактів усіх рознімань, у які вставляються плати модулів (мал. 2.18). Як правило, провідники виконуються на багатошаровій друкованій платі (її іноді називають генпанеллю), у яку упаюються рознімання для модулів. Уся конструкція (генпанель і вставлені в неї плати модулів) закривається загальним кожухом. У цьому ж кожусі іноді розміщаються і блоки живлення.

Така конструкція одержала найбільше поширення. При комплектації невеликих комп'ютерів звичайно залишаються вільні рознімання, що дозволяє надалі нарощувати їхні функціональні можливості, вставляючи в ці рознімання додаткові модулі або пам'яті модулі керування додатковими пристроями вводу-виводу. Якщо який-небудь модуль виходить з ладу, його досить просто витягти і замінити новим, справним.

Контрольні запитання:

1. Схема основного циклу обробки команди.

2. Призначення регістрів PC, IR.

3. Що таке апаратна підтримка конкретного типу даних.

4. Числові типи даних.

5. Двійково-десятковий формат.

6. Нечислові типи даних.

7. Числові типи данихPentium II.

8. Числові типи даних Ultra SPARC II.

9. Операції та структура оперативної пам’яті.

10. Операції модуля вводу-виводу.

11. Операції процесора.

12. Структура системної магістралі.

|

|

|

|

|

Дата добавления: 2015-04-24; Просмотров: 645; Нарушение авторских прав?; Мы поможем в написании вашей работы!