КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Тема: Організація прямого доступу до пам’яті

|

|

|

|

Лабораторна робота №14

У багатьох комп'ютерах сигнал переривання породжується шляхом логічного множення (І) біта дозволу переривань і біта готовності пристрою. Якщо програмне забезпечення спочатку дозволяє переривання (перед запуском пристрою вводу-виводу), переривання відбудеться відразу ж, оскільки біт готовності буде дорівнює 1. Таким чином, може знадобитися спочатку запустити пристрій, а потім відразу після цього ввести переривання. Запис байта в регістр стану пристрою не змінює біта готовності, що може тільки зчитуватися.

Ввід-вивід з керуванням по перериваннях — це великий крок вперед у порівнянні з програмувальним вводов-виводом, але усе-таки він далеко не досконалий. Справа в тім, що переривання потрібно для кожного переданого символу. Отже, потрібно якимсь чином позбутися від більшості переривань.

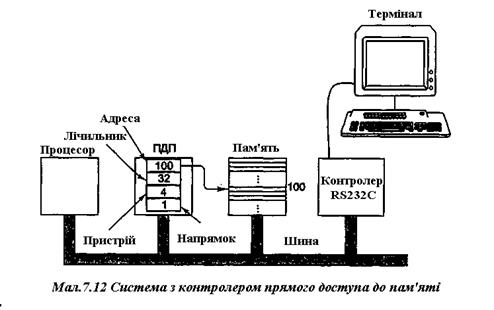

Рішення лежить у поверненні до програмувального вводу-виводу. Але тільки цю роботу повинний виконувати хтось інший. Подивіться на мал. 7.12. Ми додали нову мікросхему — контролер прямого доступу до пам'яті (ПДП) із прямим доступом до шини.

Мікросхема ПДП має принаймні 4 регістри. Усі вони можуть завантажуватися програмним забезпеченням, що працює на центральному процесорі. Перший регістр містить адреси пам'яті, які потрібно зчитати або записати. Другий регістр містить число, що показує кількість переданих байтів або слів. Третій регістр містить номер пристрою або адресу пристрою вводу-виводу, визначаючи, таким чином, який саме пристрій нам потрібен. Четвертий регістр повідомляє: повинні дані зчитуватися з пристрою чи записуватися на нього.

Щоб записати блок з 32 байтів з адреси пам'яті 100 на термінал (наприклад, пристрій 4), центральний процесор записує числа 32,100 і 4 у перші три регістри ПДП і код запису (наприклад, 1) у четвертий регістр, як показано на мал. 7.12. Контролер ПДП, ініціалізований таким чином, робить запит на доступ до шини, щоб зчитати байт 100 з пам'яті, точно так само як якби центральний процесор зчитував цей байт. Одержавши потрібний байт, контролер ПДП посилає пристрою 4 запит на ввід-вивід, щоб записати на нього байт. Після завершення цих двох операцій контролер ПДП збільшує значення регістра адреси на 1 і зменшує значення регістра лічильника на 1. Якщо значення лічильника більше 0, то наступний байт зчитується з пам'яті і записується на пристрій вводу-виводу.

Коли значення лічильника доходить до 0, контролер ПДП зупиняє передачу даних і встановлює лінію переривання на мікросхемі процесора. При наявності ПДП центральному процесору потрібно тільки ініціалізувати кілька регістрів. Після цього центральний процесор може виконувати яку-небудь іншу роботу доти, поки передача даних не завершиться. При завершенні передачі даних центральний процесор одержує сигнал переривання від контролера ПДП. Деякі контролери ПДП містять два, три і більше наборів регістрів, так що вони можуть керувати декількома процесами передачі одночасно.

Відзначимо, що якщо який-небудь високошвидкісний пристрій, наприклад диск, буде запускатися контролером ПДП, то буде потрібно дуже багато циклів шини і для звертань до пам'яті, і для звертань до пристрою. Під час цих циклів центральному процесору прийдеться чекати (ПДП завжди має пріоритет над центральним процесором на доступ до шини, оскільки пристрій вводу-виводу звичайно не допускає затримок). Процес відбору контролером ПДП циклів шини в центрального процесора називається захопленням циклу. Але виграш у тім, що не потрібно обробляти одне переривання при кожному переданому байті (слові), сильно переважує втрати, що відбуваються через захоплення циклів.

Контрольні питання:

1. Недолік вводу-виводу з керуванням по переданням.

2. Характеристика системи з контролером с ПДП.

|

|

|

|

|

Дата добавления: 2015-04-24; Просмотров: 671; Нарушение авторских прав?; Мы поможем в написании вашей работы!