КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Сегментная организация памяти

|

|

|

|

Как вы, очевидно, помните, в микропроцессоре 8086 в рамках адресного пространства объемом 1 Мбайт одновременно было доступно четыре сегмента по 64 Кбайт каждый.

В следующих моделях микропроцессоров семейства х86 (В рамках этой главы будем понимать под обозначением x86 микропроцессоры i80386 и старше) в рамках т. н. защищенного режима (protect mode, P-режим) организовано линейное адресное

пространство объемом 232 байтов, в котором допускается создание практически любого числа сегментов.

(Страница178)

Если в 8086 единственным атрибутом сегмента был его начальный адрес, то в P-режиме старших моделей семейства x86 для описания многочисленных атрибутов предусмотрена специальная структура — дескриптор.

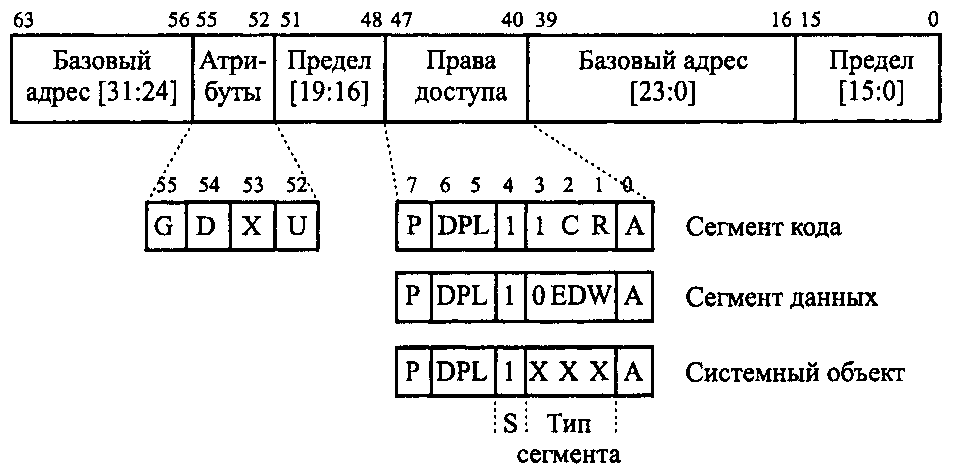

Дескриптор — это 8-байтовый блок, содержащий атрибуты области линейных адресов — сегмента. Дескриптор включает в себя информацию о положении сегмента в линейном адресном пространстве, размере сегмента, типе информации, хранящемся в сегменте и правах доступа к ней, а также другие атрибуты сегмента. Формат дескриптора представлен на рис. 7.1.

Рис 7.1. Формат дескриптора

Назначение полей дескриптора:

□ базовый адрес (Из рис, 7.1 видно, что дескриптор содержит ряд полей, имеющих название и размер. Например, 32-разрядный адрес "базовый адрес [31: 0]"; но в формате данного дескриптора он расположен в разрядах [63: 56] и [39: 16]. То же относится и к полю "предел". Это связано с желанием фирмы Intel сохранить преемственность форматов младших моделей.) [31: 0] определяет место сегмента (начальный адрес) внутри 4-гигабайтного адресного пространства;

□ предел [19: 0] определяет размер сегмента с учетом бита гранулярности (см. далее).

Поле атрибутов включает следующие признаки:

□ G — бит гранулярности. При значении G=0 размер сегмента задается в байтах, а при G=1 — в страницах по 4 Кбайт. В первом случае максимальный размер сегмента может достигать 1 Мбайт, во втором — 4 Гбайт;

□ D — бит размера по умолчанию (от англ. defaults size) обеспечивает совместимость с процессором 80286. При D=0 находящиеся в сегменте операнды считаются имеющими размер 16 битов, иначе — 32 бита;

□ X — зарезервирован Intel и не должен использоваться программистом (содержит 0);

□ U — бит пользователя (от англ. user) предназначен для использования системным программистом. Процессор игнорирует этот бит.

Байт права доступа (AR) имеет несколько отличающуюся структуру для дескрипторов сегментов разных типов, но некоторые поля этого байта являются общими для всех дескрипторов:

□ P — бит присутствия (от англ. present) сегмента, если P-0, то дескриптор не может использоваться, т. к. сегмент отсутствует в ОЗУ. При обращении к сегменту, дескриптор которого имеет P=0, формируется соответствующее прерывание;

□ DRL — уровень привилегий дескриптора (от англ. descriptor privilege level) определяет уровень привилегий, ассоциируемый с той областью памяти, которую описывает дескриптор;

□ S — определяет роль дескриптора в системе: при S=0 — системный дескриптор, служит для обращения к таблицам LDT или шлюзам для входа в другие задачи, включая программы обслуживания прерываний. При S=1 дескриптор обеспечивает обращение к сегментам программ или данных, включая стек;

□ A — бит обращения, устанавливается, когда проходит обращение к сегменту. Операционная система может следить за частотой обращения к сегменту путем периодического анализа и очистки А.

Трехбитное поле тип сегмента определяет целевое использование сегмента, задавая допустимые в сегменте операции. Значение этого поля для системных дескрипторов (S=0) безразлично. Для несистемных сегментов биты поля тип сегмента имеют следующие значения:

□ бит 3 различает сегменты кода (1) и данных (0);

□ для сегмента кода бит 2 (Conforming) отмечает при C=1 т. н. "подчиненные сегменты" (см. далее), а бит 1 (Read) при R=1 допускает чтение кода как данных с помощью префикса замены сегмента;

□ для сегмента данных бит 2 (Expand Down) определяет т. н. "расширение вниз" — для сегментов стека ED=1, а для сегментов собственно данных ED=0;

□ бит 1 (Write) показывает возможность записи в сегмент при W=1.

Дескрипторы хранятся в памяти и группируются в дескрипторные таблицы:

□ GDT — глобальная дескрипторная таблица;

□ IDT — дескрипторная таблица прерываний;

□ LDT — локальная дескрипторная таблица.

Причем, если GDT и IDT — общесистемные, присутствуют в системе в единственном экземпляре и являются общими для всех задач, то LDT может создаваться для каждой задачи.

Максимальный размер дескрипторной таблицы может составлять

213=8192 дескриптора (213 x 8=65 536 байтов).

Дескрипторная таблица локализуется в памяти с помощью соответствующего регистра. 48-битовые регистры GDTR и IDTR содержат 32-битовое поле базового адреса таблицы и 16-битный предел (размер) таблицы с байтовой гранулярностью.

Для локализации LDT используется 16-разрядный регистр LDTR, содержащий только селектор сегмента, в котором размещена таблица. Таблицы LDT хранятся как сегменты, а дескрипторы этих сегментов размещаются в GDT. Селектор регистра LDTR выбирает из GDT нужный дескриптор, и атрибуты LDT становятся доступны процессору. С LDTR, как и с сегментными регистрами, ассоциируется соответствующий "теневой регистр", в который помещается выбранный из GDT дескриптор LDT текущей задачи. При переключении задачи достаточно заменить 16-разрядное содержимое LDTR, а процессор автоматически загрузит теневой регистр.

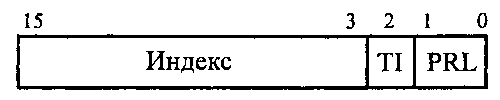

Доступ к памяти в любом режиме х86 возможен лишь в область, определенную как сегмент. Количество доступных в данный момент сегментов определяется числом сегментных регистров (CS, SS, DS, ES, FS, GS). Однако в защищенном режиме содержимое сегментного регистра не является базой сегмента, а рассматривается как селектор сегмента и имеет формат, приведенный на рис. 7.2.

Рис. 7.2. Формат селектора

Индекс определяет смещение внутри дескрипторной таблицы, которая соответственно разрядности индекса может содержать 213 8-байтовых дескрипторов. Бит TI определяет тип дескрипторной таблицы: 0 — глобальная, 1 — локальная. Поле RPL определяет запрашиваемый уровень привилегий.

Итак, селектор адресует дескриптор сегмента в одной из дескрипторных таблиц. Всякий раз, когда производится перезагрузка сегментного регистра (замена селектора), адресуемый им дескриптор извлекается из соответствующей дескрипторной таблицы и помещается в "теневой регистр" дескриптора. Все последующие обращения к этому сегменту не требуют чтения из дескрипторной таблицы.

Логический адрес в защищенном режиме, как и в реальном, описывается парой RS: EA, где RS — содержимое выбранного сегментного регистра, ЕА — эффективный адрес, генерируемый программой (смещение в сегменте).

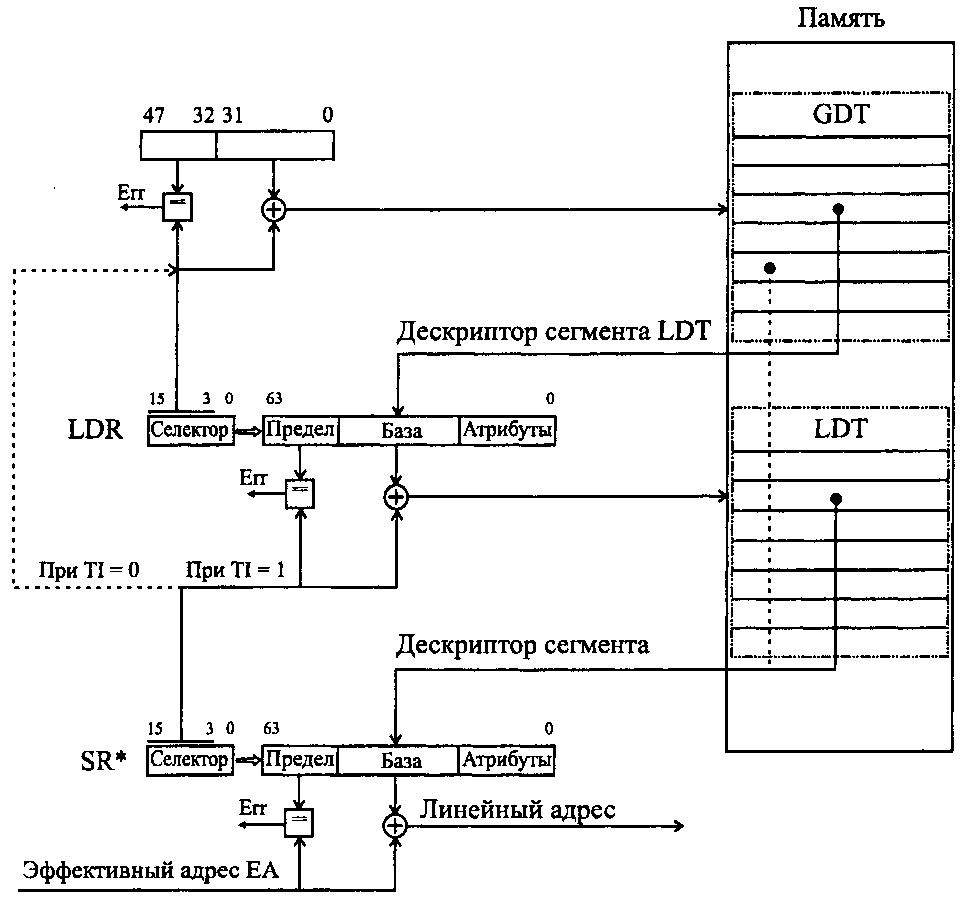

Рис. 7.3. Преобразование логического адреса в линейный

Процесс загрузки дескрипторных регистров и преобразования эффективного (логического) адреса в линейный протекает следующим образом (рис. 7.3):

1. При переходе в защищенный режим в памяти создается глобальная дескрипторная таблица, базовый адрес которой размещается в регистре GDTR.

2. Несколько сегментов определяется в памяти, и их дескрипторы помещаются в GDT.

3. При запуске очередной задачи можно определить дополнительно несколько сегментов и для хранения их дескрипторов создать локальную дескрипторную таблицу, как системный сегмент, дескриптор которого хранится в GDT, а его положение в GDT определяется селектором в регистре LDTR. В теневой регистр LDTR автоматически помещается дескриптор сегмента LDT.

4. При загрузке в любой сегментный регистр нового содержимого в соответствующий теневой регистр автоматически помещается новый дескриптор из GDTR или LDTR.

5. При генерации программой очередного адреса ЕА из соответствующего теневого сегментного регистра выбирается базовый адрес сегмента и складывается со значением ЕА. Полученная сумма представляет собой линейный адрес.

В приведенной выше процедуре не отражены особые случаи, которые могут возникать при различных нарушениях (ошибках) в процессе формирования линейного адреса.

Механизм сегментации можно искусственно подавить, назначив все базовые адреса сегментов равными нулю и определив длину всех сегментов в 4 Гбайт. Таким образом, в адресном пространстве определится единственный сегмент размером 232 байтов.

Сегмент в защищенном режиме — область памяти, снабженная рядом атрибутов: типом, размером, положением в памяти, уровнем привилегий и др. Сегмент может начинаться и кончаться, где угодно, и его размер — произвольный. Другой элемент памяти — страница — имеет строго фиксированный размер (4 Кбайт) и положение в линейном адресном пространстве: страница всегда выровнена по границе 4-килобайтовых фрагментов, т. е. 12 младших разрядов адреса страницы — всегда нули.

|

|

|

|

|

Дата добавления: 2015-04-25; Просмотров: 934; Нарушение авторских прав?; Мы поможем в написании вашей работы!