КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Демультиплексор - устройство функционального назначения, предназначенное для распределения цифровой информации с общей шины данных по соответствующим каналам

|

|

|

|

Таким образом, демультиплексор реализует операцию, обратную мультиплексированию, и под воздействием управляющих сигналов распределяет информацию по соответствующим адресам. Условное обозначение демультиплексора приведено на рисунке.

Для выходных сигналов демультиплексора можно записать булевы соотношения, описывающие функционирование устройства, по которым можно просто построить логическую схему демультиплексора.

Лекция 15. Триггеры

15.1. Классификация триггеров

Триггер – это электронная схема, имеющая два устойчивых состояния, в которых она может находиться сколь угодно долго до прихода управляющего воздействия, Триггер – элементарная ячейка памяти, способная сохранять двоичную информацию (1 или 0), после снятия входного сигнала

Классификация:

- По способу управления:

– асинхронные – выходной сигнал появляется одновременно с входным;

– синхронные (тактируемые) – выходной сигнал появляется только при совпадении во времени входного информационного сигнала с сигналом синхронизации.

- По функциям:

– с раздельной установкой 1 и 0;

– с приёмом информации по одному входу;

– универсальный.

15.2. Асинхронный RS триггер

|

|

| Рис. 15.1. Схематическое обозначение RS-триггера Входы: Set –Установка,. Reset- сброс | Рис. 15.2. Триггерная структура на различных типах логических элементов: а)И-НЕ, б)ИЛИ-НЕ |

1) Единичный импульс на выходе S при нулевом состоянии R устанавливается или подтверждает 1 на выходе Q.

2) Единичный импульс R при нулевом состоянии входа S устанавливает или подтверждает на выходе Q ноль.

3) Нулевое состояние на обоих входах не изменяет состояние триггера (режим хранения информации)

4) Единичное состояние обоих входов в RS-триггере запрещено

Таблица 15.1.

Таблица истинности RS-триггера

| S | R | Q |

| |

| Q |

| Хранение | ||

| - | - | запрещено |

|

Рис. 15.3. Временные диаграммы работы RS-триггера

Асинхронным такой триггер называется потому, что состояние триггера изменяется непосредственно при появлении соответствующего сигнала на информационных входах.

Синхронный RS-триггер

В большинстве цифровых схем необходимо переключение всех её составляющих в определённый момент времени. Для этого в каждой микросхеме существует генератор тактовых импульсов, которые и осуществляют переключение. При этом добавляется третий синхронизирующий вход.

Таблица 15.2.

Таблица истинности синхронного RS-триггера

| С | S | R | Q |

|

| ↑ | Q |

| ||

| ↑ | ||||

| ↑ | ||||

| ↑ | - | - |

|

.

Рис. 15.4. Логическая структура синхронного RS-триггера

Состояние синхронного RS триггера изменяется при входных комбинациях R и S аналогично асинхронному RS-триггеру, однако необходимое условие для переключения является только в момент прихода тактового импульса

Рис. 15.5. Временные диаграммы работы синхронного RS-триггера

D-триггер

D-триггер

Рис. 15.6. Схематическое обозначение D-триггера

|

Он может быть получен из синхронного RS-триггера:

Рис. 15.7. Реализация D-триггера на основе синхронного RS-триггера

Приход тактового импульса при наличии 1 на входе D переключает триггер в состояние 1. Приход тактового импульса при нуле на входе D переключает триггер в состояние 0.В связи с такой особенностью, его называют триггером задержки, т.е. он переписывает состояние на входе D на выход с задержкой до прихода тактового импульса.

Рис. 15.8. Временные диаграммы работы D-триггера

Однотактный JK –триггер

Он является наиболее универсальным. Входы J и K соответствуют S и R входам RS-триггера.

Рис. 15.9. Схематическое обозначение JK –триггера

Отличие JK от RS состоит в том, что в JK –триггере нет запрещенного состояния входов. При состоянии на входах J =1, K =0

приход тактового импульса переключает JK триггер в состояние 1. При состоянии на входах J =0, K =1 приход тактового импульса переключает JK триггер в состояние 0. Состояние на входах J =0, K =0 соответствует режиму хранения информации и приход тактового импульса при этом состоянии входов не изменяет состояния на выходе триггера. При состоянии входов J =1, K =1, JK –триггер работает в переключающем режиме, т.е. с приходом каждого тактового импульса при данном состоянии входов меняет состояние триггера на противоположное.

Таблица 15.4.

Таблица истинности JK –триггера

| С | J | K | Q |

|

| ↑ | Q |

| ||

| ↑ | ||||

| ↑ | ||||

| ↑ |

| Q |

|

Рис.15.10. Временные диаграммы работы JK –триггера

|

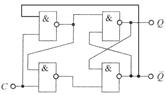

Рис. 15.11. Логическая структура JK –триггера

Двухтактные JK –триггеры или триггеры типа MS

(Master-Slave=[мастер-помощник])

Главная особенность триггера состоит в том, что переключение происходит по спаду тактового импульса. Благодаря чему появляется возможность создавать более сложные схемы, счетчики и сдвиговые регистры.

|

Рис. 15.12. Схематическое обозначение двухтактного JK – триггера

Рис.15.13. Логическая структура двухтактного JK – триггера

|

Рис. 15.14. Временные диаграммы работы двухтактного JK –триггера

С приходом тактового импульса по его фронту первый триггер переключается в состояние, сформированное соответствующим состоянием входов. В момент действия тактового импульса на входе С второго триггера сохраняется состояние 0. По спаду тактового импульса на входе C второго триггера появляется логическая 1 и информация, записанная на первом такте в первый триггер, переписывается на выход второго триггера, т.е. двухтактный триггер обеспечивает развязку между выходом и входом на время действия тактового импульса.

Счетный Т –триггер

Счётный Т-триггер можно построить на JK-триггере или на D-триггере.

Для построения Т-триггера на JK-триггере нужно сделать входы J=K=1. Тогда каждый импульс на входе С будет изменять состояние триггера на противоположное. Для построения Т-триггера на D-триггере необходимо соединить его вход D с инверсным выходом Q', т.е. сделать Q'=D. В такой схеме каждый переход 1 / 0 на входе С будет приводить к переходу триггера в противоположное состояние. Таким образом, Т-триггер представляет собой делитель частоты на два.

Рис.15.15. Счётный триггер; реализация на логических элементах.

Лекция 16. Последовательностные устройства: регистры и счетчики

|

|

|

|

|

Дата добавления: 2015-05-06; Просмотров: 480; Нарушение авторских прав?; Мы поможем в написании вашей работы!