КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Дешифраторы

|

|

|

|

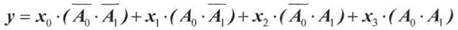

Дешифратором называют преобразователь двоичного n-разрядного кода в унитарный 2n-разрядный код, все разряды которого, за исключением одного, равны единице. Дешифраторы бывают полные и неполные. Для полного дешифратора выполняется условие:

|

(8.1)

где п — число входов (обычно n равно 2, 3 или 4); N — число выходов.

В неполных дешифраторах имеется п входов, но реализуется N<2n выходов. Так, например, дешифратор, имеющий 4 входа и 10 выходов, будет неполным, а дешифратор, имеющий 2 входа и 4 выхода, будет полным.

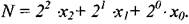

На рис. 8.1 изображен дешифратор с п = 3.

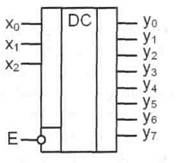

На входы х0, х1, х2 можно подать 8 комбинаций логических уровней: 000, 001, 010,..., 111. Схема имеет 8 выходов, на одном из которых формируется низкий потенциал (0), а на остальных высокий (1). Номер этого единственного выхода, на котором формируется нулевой уровень, соответствует числу N, определяемому состоянием входов х0, х1 х2 следующим

|

образом:

|

|

решают функционирование дешифратора или переводят его в пассивное состояние, при котором, независимо от сигналов на информационных входах, на всех выходах установится уровень логической единицы. Можно сказать, что существует некоторая функция разрешения, значение которой определяется состояниями управляющих входов.

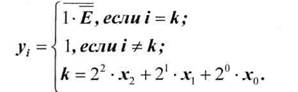

Разрешающий вход дешифратора может быть прямым или инверсным. У дешифраторов с прямым разрешающим входом активным уровнем является уровень логической единицы, у дешифраторов с инверсным входом - уровень логического нуля. Дешифратор, представленный на рис.8.1, имеет один инверсный вход управления. Принцип формирования выходного сигнала в этом дешифраторе с учетом сигнала управления описывается следующим образом:

| (8.3) ая. Для яет со-вления. тоавле- (8.4) |

Существуют дешифраторы с несколькими входами управления. Для таких дешифраторов функция разрешения, как правило, представляет собой логическое произведение всех разрешающих сигналов управления. Например, для дешифратора КР555ИД7 с одним прямым входом управления Е1 и двумя инверсными Е2 и ЕЗ функция Е имеют вид:

Мультиплексоры

Мультиплексором называется комбинационная логическая схема, представляющая собой управляемый переключатель, который подключает к выходу один из информационных входов данных. Номер подключаемого входа равен числу, определяемому комбинацией логических уровней на адресных входах. Кроме информационных и адресных входов, схемы мультиплексоров содержат вход разрешения, при подаче на который активного уровня мультиплексор переходит в активное состояние. При подаче на вход разрешения пассивного уровня мультиплексор перейдет в пассивное состояние, для которого сигнал на выходе сохраняет постоянное значение независимо от значений информационных и адресных сигналов.

В зависимости от соотношения числа информационных входов п и числа адресных входов т мультиплексоры делятся на полные и неполные. Если выполняется условие п = 2т, то мультиплексор будет полным. Если это условие не выполняется, т.е. п < 2т, то мультиплексор будет неполным.

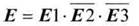

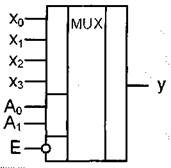

Число информационных входов у мультиплексоров обычно 2, 4, 8 или 16. На рис.8.2 представлен мультиплексор 4x1 с инверсным входом

разрешения Е и прямым выходом у, представляющий собой половину микросхемы мультиплексора КР555КШ2.

|

Рис. 8.2. Условное обозначение мультиплексора 4x1

Выражение для выходной функции такого мультиплексора можно записать в виде:

|

(8.5)

где Хо, х1, х2, х3 - информационные входы мультиплексора; Ао, А1 - адресные входы мультиплексора.

где Хо, х1, х2, х3 - информационные входы мультиплексора; Ао, А1 - адресные входы мультиплексора.

В общем случае для полного мультиплексора, имеющего п управляющих (адресных) входов и 2" информационных входов можно реализовать n-входовую логическую функцию. Поскольку каждой комбинации управляющих входов соответствует единственный информационный вход, на него следует подавать требуемое значение логической функции, которое и будет передано на выход мультиплексора.

Триггеры

Триггером называется простейшее устройство, имеющее два устойчивых состояния, переход между которыми происходит в результате процессов, обусловленных наличием в электрической цепи триггера цепей положительной обратной связи.

Два устойчивых состояния триггера обозначаются: Q=1 и Q=0. В каком из этих состояний окажется триггер, зависит от состояния сигналов на входах триггера и от его предыдущего состояния, иными словами триггер имеет память. Можно сказать, что триггер является элементарной ячейкой памяти.

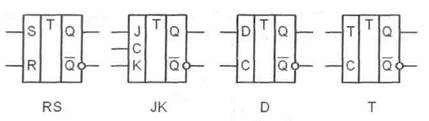

Тип триггера определяется алгоритмом его работы. В зависимости от алгоритма работы, триггер может иметь установочные, информационные и управляющие входы. Установочные входы устанавливают состояние триггера независимо от состояния других входов. В частности, входы управления разрешают запись данных, подающихся на информационные входы. Наиболее распространенными являются триггеры RS, JK, D и Т. Условное обозначение этих триггеров приведено на рис. 8.3.

|

Рис.8.3. Условное изображение триггеров: RS-, JK-, D- и Т-типа

Рис.8.3. Условное изображение триггеров: RS-, JK-, D- и Т-типа

RS-триггер имеет два информационных входа S и R. Подача на вход S сигнала 1, а на вход R сигнала 0 устанавливает на выходе Q триггера сигнал 1. Наоборот, при сигналах S=0 и R=1 сигнал на выходе триггера Q=0. Функционирование SR-триггера. определяется уравнением:

|

(8.6)

где Qn и Qn+1 - соответственно, предыдущее и новое состояния триггера.

где Qn и Qn+1 - соответственно, предыдущее и новое состояния триггера.

Для RS-триггера комбинация S=l и R=l является запрещенной. После такой комбинации информационных сигналов состояние триггера будет неопределенным: на его выходе Q может быть 0 или 1.

Существуют разновидности RS-триггеров, называемые Е-, R- и S-триггерами, для которых сочетание S=R=\ не является запрещенным. Е-триггер при S=R=1 не изменяет своего состояния (Qn+1=Qn)- S-триггер при S=R=1 устанавливается в состояние Q=1, a R-триггер в этом случае устанавливается в состояние Q=0.

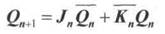

JK-триггер имеет также два информационных входа J и К. Подобно RS-триггеру, в JK-триггере J и К - это входы установки выхода Q триггера в состояние 1 или 0. Однако, в отличие от RS-триггера, в JK-триггере наличие J=K= 1 приводит к переходу выхода Q триггера в противоположное состояние, JK-триггеры синхронизируются только перепадом потенциала на входе С. Условие функционирования JK-триггера имеет вид:

|

(8.7)

D-триггер, или триггер задержки, при поступлении синхросигнала на вход С устанавливается в состояние, соответствующее потенциалу на входе D. Уравнение функционирования D-триггера имеет вид: Q„+j=D„. Это уравнение показывает, что выходной сигнал Qn+1 изменяется не сразу после изменения входного сигнала D, а только с приходом синхросигнала, т.е. с задержкой на один период импульсов синхронизации (Delay - задержка).

D-триггер, или триггер задержки, при поступлении синхросигнала на вход С устанавливается в состояние, соответствующее потенциалу на входе D. Уравнение функционирования D-триггера имеет вид: Q„+j=D„. Это уравнение показывает, что выходной сигнал Qn+1 изменяется не сразу после изменения входного сигнала D, а только с приходом синхросигнала, т.е. с задержкой на один период импульсов синхронизации (Delay - задержка).

Синхронизация D-триггера может осуществляться импульсом или фронтом.

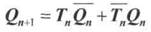

Т-триггер, или счетный триггер, изменяет состояние выхода по фронту импульса на входе С. Кроме входа синхронизации (С) Г-триггер может иметь подготовительный вход Т. Сигнал на этом входе разрешает

(при Т=1) или запрещает (при T=0) срабатывание триггера от фронтов импульсов на входе С. Функционирование T-триггера определяется уравнением:

|

(8.8)

Из этого уравнения следует, что при Т= 1 соответствующий фронт сигнала на входе С переводит триггер в противоположное состояние. Частота изменения потенциала на выходе T-триггера в два раза меньше частоты импульсов на входе С. Это свойство T-триггера позволяет строить на их основе двоичные счетчики. Поэтому эти триггеры и называют счетными. Счетный триггер без входа T ведет себя так же, как и T-триггер при T=1.

|

|

|

|

|

Дата добавления: 2015-05-06; Просмотров: 3056; Нарушение авторских прав?; Мы поможем в написании вашей работы!