КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Самостоятельная работа №43

|

|

|

|

« Проанализировать возможности МП и ЭВМ»

(МП) МИКРОПРОЦЕССОР

- программно-управляемое универсальное устройство для цифровой обработки дискретной и (или)аналоговой информации и управления процессом этой обработки, построенное на одной или неск. больших интегральных схемах (БИС). По существу, МП может выполнять те же функции, что и процессор ЭВМ (илиего составная часть),- отсюда с учётом изготовления его по технологии микроэлектроники произошло назв. "МП".

Области применения МП определяются, с одной стороны, возможностями МП как БИС - компонентаэлектронных схем, а с другой - возможностями МП по обработке информации и управлению этимпроцессом, присущими ЭВМ. В совокупности с БИС постоянного запоминающего устройства (ПЗУ),оперативного запоминающего устройства (ОЗУ) (см. Памяти устройства)и БИС управления вводом-выводом информации МП позволяет создавать универсальные ЭВМ, причём он выполняет функциипроцессора (организацию работы ЭВМ, логич. и арифметич. обработку информации). Др. областьприменения МП - специа-лизиров. системы для сбора информации с объекта, её обработки и оптим.управления объектом. Примерами из этой области являются специализиров. управляющие МП(микроконтроллеры) и приборы со встроенной микропроцессорной системой ввода-вывода информации и еёобработки (т. н. интеллектуальные приборы).

Спектр применений МП в физике определяется наряду с этим ещё двумя обстоятельствами. Во-первых, МП,работающий от внеш. источника энергии и управляющий состоянием замкнутой системы, способенуправлять изменением её энтропии заданным образом [1]. Эта способность широко используется вавтомати-зиров. устройствах управления системами для оптимизации либо повышения эффективностипроисходящих в них процессов (напр., удержание на заданном уровне темп-ры печи, в контур управлениянагревателем к-рой включён МП). Во-вторых, любой алгоритм обработки информации можно реализоватьпрограммно (с помощью выполнения соответствующей программы универсальным МП) либо аппаратурно (спомощью епециализиров. МП, при разработке к-рого искомый алгоритм был реализован непосредственно вего электронной схеме). Последний способ обеспечивает макс, быстродействие алгоритма и представляетинтерес в том случае, когда требуется обрабатывать информацию с частотой, превышающей частоту еёобработки программным путём. Напр., для обработки изображений, следующих с частотой телевизионнойразвёртки, широко используется фурье-МП, аппаратурно реализующий алгоритмы быстрого преобразованияФурье.

МП характеризуются: полупроводниковой технологией изготовления интегральных схем, составляющих МП,их кол-вом; архитектурой (логич. организацией МП, определяющей процесс обработки информации вконкретном МП и включающей методы кодирования информации, состав, назначение и принципывзаимодействия аппаратурных средств МП); набором инструкций; ёмкостью адресуемой памяти;производительностью; стоимостью и др. [1, 2, 4, 5].

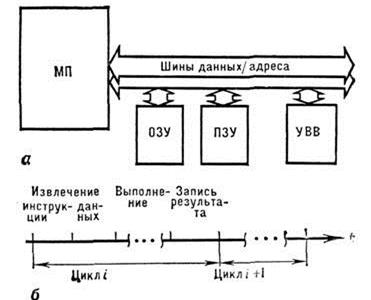

Принцип функционирования МП. МП работает, выполняя т. н. циклы инструкций - последоват. извлеченияиз памяти (ОЗУ, ПЗУ) инструкций, управляющих работой МП, их анализ и исполнение. При этом в началецикла МП обращается к памяти один раз для чтения инструкции, а затем при необходимости ещё неск. раздля чтения (записи) данных из памяти или ввода-вывода данных через устройства ввода-выводаинформации (УВВ).

В ОМП обычно используется одна и та же шина для обращения к памяти и УВВ (рис. 1, а), причём в один итот же момент времени может читаться или записываться только одна инструкция или слово данных, т. е.инструкции и данные обрабатываются последовательно (рис. 1, б).

Рис. 1. Архитектура (а) и временная диаграмма цикла инструкции (б) однокристального микропроцессора.

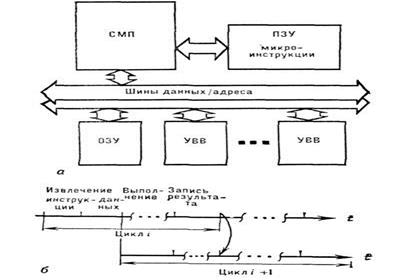

В СМП шины данных (адреса) памяти, в к-рых хранятся микроинструкции, как правило, разделены (рис. 2, а)и процесс выборки след, инструкции может быть совмещён во времени с исполнением текущей инструкции(рис. 2, б).

Рис. 2. Архитектура (а) и временная диаграмма цикла инструкции (б) секционного микропроцессора.

Технология изготовления МП. При произ-ве МП используются все известные виды технологий (ТТЛ, ТТЛШ, И2 Л, И 3JI, ЭСЛ, n -МОП, к-МОП и р -МОП [3-4]), дающие разл. выходные характеристики МП. Так, технологияТТЛШ позволяет получить быстродействующие МП с высокой радиац. стойкостью, но имеющие большуюпотребляемую мощность и невысокую степень интеграции, технология n -МОП обеспечивает высокуюстепень интеграции при умеренной мощности потребления, но низкую радиац. стойкость. Высокимипотребительскими свойствами обладают МП, изготовленные по технологии к -МОП на подложке из сапфира,а изготовленные по технологии р -МОП имеют низкую себестоимость, но обладают небольшимбыстродействием.

Универсальные и специализированные МП. Универсальный МП представляет собой многофункциональнуюБИС или их набор с программируемой логикой работы. Из-за своей универсальности он зачастую имеетнизкую эффективность использования в разл. областях применений из-за несоответствия архитектуры МПхарактеру задач.

Альтернативой ему в этом отношении является специализиров. МП, архитектура к-рого полностьюориентирована на решение конкретной задачи. Появление таких МП стало возможным благодаря технологиипроиз-ва БИС на базе вентильных матриц или базовых матричных кристаллов, когда один или неск. нижнихслоев БИС являются неизменными, а меняется лишь верх, слой (слои) [5

Специализиров. МП развиваются по пути создания МП, реализующих спец. алгоритмы обработки данных(алгоритмич. МП). Для традиц. архитектуры первыми шагами в этом направлении стала разработка МП ссокращённым набором инструкций (RISC) и МП с набором инструкций языков программирования высокогоуровня.

Алгоритмич. МП - по сути развитие указанных направлений. Напр., применительно к задачам физикисоздаются алгоритмич. МП, служащие для обработки изображений и речи, цифровой фильтрации сигналов(систолич. ЭВМ) [5], а также МП для аналитич. вычислений, реализации метода наим. квадратов, линейногопрограммирования, работы с фактографич. базами данных и др.

Среди специализиров. МП можно выделить МП для обработки сигналов (сигнальные МП), к-рьте по сутидела являются алгоритмич. МП, обрабатывающими информацию, заданную не в цифровом виде. При этомперед началом её цифровой обработки МП преобразует эту информацию в цифровой вид (напр.,аналоговый сигнал - с помощью встроенного аналого-цифрового преобразователя). В случае аналоговыхвходных сигналов обрабатывающий их специализиров. МП наз. аналоговым MП [4]. Они могут выполнятьфункции любой аналоговой схемы (усиление сигнала, модуляцию, смещение, фильтрацию и др.) вреальном масштабе времени. При этом применение аналогового МП значительно повышает точностьобработки сигналов, их воспроизводимость, расширяет функциональные возможности обработки сигналов засчёт цифровых методов.

Устройство микропроцессор

Электрона вычислительные машины (ЭВМ)

Основные узлы микропроцессора:

Устройство управления, выполняющее роль арбитра над прочими узлами: анализ и декодирование потока инструкций, передача их в функциональные устройства, синхронизация узлов.

Одно или несколько исполнительных устройств, производящих обработку данных: арифметические, логические, сдвиговые операции, пересылки, операции над числами с плавающей запятой и пр.

Регистровый файл, выполняющий роль хранилища входных, промежуточных и выходных данных для обработки, а также хранилища управляющей информации.

Устройство ввода-вывода, обеспечивающее выборку инструкций из памяти, обмен данными с памятью и внешними устройствами.

Микропроцессорные архитектуры

По характеру исполняемого кода и организации устройства управления выделяется несколько типов архитектур:

Процессор со сложным набором инструкций, англ. CISC — Complex Instruction Set Computer. Эту архитектуру характеризует большое количество сложных инструкций, и как следствие сложное устройство управления. В ранних вариантах CISC-процессоров и процессоров для встроенных приложений характерны большие времена исполнения инструкций (от нескольких тактов до сотни), определяемые микрокодом устройства управления. Для высокопроизводительных суперскалярных процессоров свойственны глубокий анализ программы, внеочередное исполнение операций.

Процессор с упрощённым набором инструкций, англ. RISC — Reduced Instruction Set Computer. В этой архитектуре значительно более простое устройство управления. Большинство инструкций RISC-процессора сожержат одинаковое малое число операций (1, иногда 2-3), а сами командные слова в подавляющем числе случаев имеют одинаковую ширину (PowerPC, ARM), хотя бывают исключения (Coldfire). У суперскалярных процессоров — простейшая группировка инструкций без изменения порядка исполнения.

Процессор с явным параллелизмом, англ. EPIC — Explicitly Parallel Instruction Computer (-ing, термин ® Intel, HP). Отличается от прочих прежде всего тем, что последовательность и параллельность исполнения операций и их распределение по функциональным устройствам явно определены программой. Такие процессоры могут обладать большим количеством функциональных устройств без особого усложнения устройства управления и потерь эффективности. Обычно такие процессоры используют широкое командное слово, состоящее из нескольких слогов, определяющих поведение каждого функционального устройства в течение такта.

Процессор с минимальным набором инструкций, англ. MISC — Minimal Instruction Set Computer. Эта архитектура определяется прежде всего свехмалым количеством инструкций (несколько десятков), и почти все они нуль-операндные. Такой подход даёт возможность очень плотно упаковать код, выделив под одну инструкцию от 5 до 8 бит. Промежуточные данные в таком процессоре обычно хранятся на внутреннем стеке, и операции производятся над значениям на вершине стека. Эта архитектура тесно связана с идеологией программирования на языке Forth и обычно используется для исполнения программ, написанных на этом языке.

Процессор с изменяемым набором инструкций, англ. WISC — Writable Instruction Set Computer. Архитектура, позволяющая перепрограммировать себя, изменяя набор инструкций, подстраивая его под решаемую задачу.

Транспорт-управляемый процессор, англ. TTA — Transort Triggered Architecture. Архитектура изначально ответвилась от EPIC, но принципиально отличающаяся от остальных тем, что инструкции такого процессора кодируют функциональные операции, а так называемые транспорты — пересылки данных между функциональными устройствами и памятью в произволном порядке.

По способу хранения программ выделяется две архитектуры:

Архитектура фон Неймана. В процессорах этой архитектуры используется одна шина и одно устройство ввода-вывода для обращения к программе и данным.

Гарвардская архитектура. В процессорах этой архитектуры для выборки программ и обмена данным существуют отдельные шины и устройства ввода-вывода. Во встроенных микропроцессорах, микроконтроллерах и ПЦОС это также определяет существование двух независимых запоминающих устройств для хранения программ и данных. В центральных процессорах это определяет существование отдельного кэша инструкций и данных. За кэшем шины могут быть объединены в одну посредством мультиплексирования.

По организации регистрового файла ФУ можно выделить следующие типы процессоров.

Регистровая архитектура — характеризуется свободным доступом к регистрам для выборки всех аргументов и записи результата. Элементарны арифметико-логические операции в таких процессорах кодируются в двух-, или трёхоперандные инструкции (регистр+регистр→регистр, иногда регистр результата совпадает с источником одного из агрументов).

Аккумуляторная архитектура — из регистров выделяется один из несколько регистров-аккумуляторов. Регистр-аккумулятор является источником одного из аргументов и приёмником результата вычислений. Операции кодируются как правило в однооперандные инструкции (аккумулятор+операнд→аккумулятор). Такая архитектура характерная для многих CISC-процессоров (напр. Z80).

Стековая архитектура — определяется организацией регистрового файла в виде стека, и косвенной адресацией регистров через указатель стека, который определяет положение вершины стека, операции производятся над значениями на вершине стека и результат кладётся также на вершину. Арифметические операции кодируются в нуль-операндные инструкции. Стековая архитектура является неотъемлемой частью MISC-процессоров.

|

|

|

|

|

Дата добавления: 2015-05-06; Просмотров: 407; Нарушение авторских прав?; Мы поможем в написании вашей работы!