КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Основные логические устройства компьютера (сумматор, регистр)

|

|

|

|

Поскольку любая логическая операция может быть представлена в виде комбинации трех базовых операций (И, ИЛИ, НЕ), любые устройства компьютера, производящие обработку или хранение информации, могут быть собраны из базовых логических элементов как из кирпичиков.

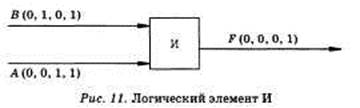

Логический элемент И. На входы А и В логического элемента последовательно подаются четыре пары сигналов различных значений, на выходе получается последовательность из четырех сигналов, значения которых определяются в соответствии с таблицей истинности операции логического умножения (рис. 11).

Логический элемент ИЛИ. На входы Аи В логического элемента последовательно подаются четыре пары сигналов различных значений, на выходе получается последовательность из четырех сигналов, значения которых определяются в соответствии с таблицей истинности операции логического сложения (рис. 12).

Логический элемент НЕ. На вход А логического элемента последовательно подаются два сигнала, на выходе получается последовательность из двух сигналов,

значения которых определяются в соответствии с таблицей истинности логического отрицания (рис. 13).

Сумматор. В целях максимального упрощения работы компьютера все многообразие математических операций в процессоре сводится к сложению двоичных чисел. Поэтому главной частью процессора является сумматор, который обеспечивает такое сложение.

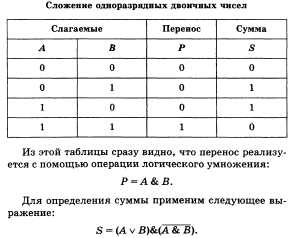

При сложении двоичных чисел образуется сумма в данном разряде, при этом возможен перенос в старший разряд. Обозначим слагаемые (А, В), перенос (Р) и сумму (S). Построим таблицу сложения одноразрядных двоичных чисел с учетом переноса в старший разряд (табл. 4).

Теперь, на основе полученного логического выражения, можно построить из базовых логических элементов схему полусумматора (рис. 14).

Данная схема называется полусумматором, так как выполняет суммирование одноразрядных двоичных чисел без учета переноса из младшего разряда.

Многоразрядный сумматор процессора состоит из полных одноразрядных сумматоров. На каждый разряд ставится одноразрядный сумматор, причем выход (перенос) сумматора младшего разряда подключен ко входу сумматора старшего разряда.

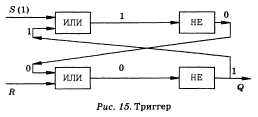

Триггер. Важнейшей структурной единицей оперативной памяти компьютера, а также внутренних регистров процессора является триггер (рис. 15). Это устройство позволяет запоминать, хранить и считывать информацию (каждый триггер может хранить 1 бит информации).

Для построения триггера достаточно двух логических элементов «ИЛИ» и двух элементов «НЕ».

В обычном состоянии на входы триггера подан сигнал «О», и триггер хранит «О». Для записи «1» на вход S (установочный) подается сигнал «1». При последовательном рассмотрении прохождения сигнала по схеме видно, что триггер переходит в это состояние и будет устойчиво находиться в нем и после того, как сигнал на входе S исчезнет. Триггер запомнил «1», т. е. с выхода триггера Q можно считать «1».

Чтобы сбросить информацию и подготовиться к приему новой, на вход R (сброс) подается сигнал «1», после чего триггер возвратится к исходному «нулевому» состоянию.

|

|

|

|

|

Дата добавления: 2015-04-24; Просмотров: 1308; Нарушение авторских прав?; Мы поможем в написании вашей работы!