КАТЕГОРИИ:

Архитектура-(3434)Астрономия-(809)Биология-(7483)Биотехнологии-(1457)Военное дело-(14632)Высокие технологии-(1363)География-(913)Геология-(1438)Государство-(451)Демография-(1065)Дом-(47672)Журналистика и СМИ-(912)Изобретательство-(14524)Иностранные языки-(4268)Информатика-(17799)Искусство-(1338)История-(13644)Компьютеры-(11121)Косметика-(55)Кулинария-(373)Культура-(8427)Лингвистика-(374)Литература-(1642)Маркетинг-(23702)Математика-(16968)Машиностроение-(1700)Медицина-(12668)Менеджмент-(24684)Механика-(15423)Науковедение-(506)Образование-(11852)Охрана труда-(3308)Педагогика-(5571)Полиграфия-(1312)Политика-(7869)Право-(5454)Приборостроение-(1369)Программирование-(2801)Производство-(97182)Промышленность-(8706)Психология-(18388)Религия-(3217)Связь-(10668)Сельское хозяйство-(299)Социология-(6455)Спорт-(42831)Строительство-(4793)Торговля-(5050)Транспорт-(2929)Туризм-(1568)Физика-(3942)Философия-(17015)Финансы-(26596)Химия-(22929)Экология-(12095)Экономика-(9961)Электроника-(8441)Электротехника-(4623)Энергетика-(12629)Юриспруденция-(1492)Ядерная техника-(1748)

Опис тригерних схем

|

|

|

|

А. Шиков

Подполковник

Тригерна (послідовнісна) схема ― схема з елементом пам’яті (тригером), який синхронізується фронтом (синхронний тригер) або рівнем тактового сигналу (тригер-засувка).

2.1.1. Регістри

Регістр ― пристрій призначений для прийому, зберігання, передачі та перетворення форм подання даних (паралельна, послідовна).

За способами прийому і передачі даних розрізняють:

Паралельний регістр ― регістр з паралельним завантаженням і видачею даних;

Зсувний регістр ― регістр з послідовним завантаженням і видачею даних;

Зсувний регістр з паралельним завантаженням даних;

Зсувний регіт з паралельним виводом даних.

Паралельний регістр

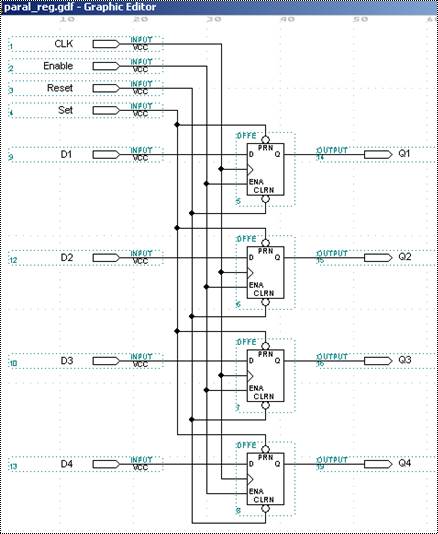

З метою кращої уяви структури паралельного регістра паралельно розглянемо структурну схему чотири розрядного паралельного регістра (наведену на рис. 3), виконану засобами системи проектування MAX+plus II.

Рис. 3

У наведеного регістра  ,

,  , відповідно, чотирирозрядний вхід і вихід даних. Інші виводи описані вище.

, відповідно, чотирирозрядний вхід і вихід даних. Інші виводи описані вище.

Опис відповідного регістра, виконаного мовою AHDL, наведено в проекті RG_4

SUBDESIGN RG_4

(

D[4..1], CLK, Set, Reset:INPUT=GND;

Enable: INPUT=VCC;

Q[4..1]: OUTPUT;

)

VARIABLE

FF[4..1]:DFFE;

BEGIN

FF[].clk =CLK;

FF[].(clrn, prn)=(Reset, Set);

FF[].ena =Enable;

FF[].d =D[];

Q[] =FF[].q;

END;

Як видно з файлу, регістр оголошений у секції VARIABLE, як D-Тригер з дозволом (DFFE). У першому булевому рівнянні в логічній секції відбувається під’єднання входу тактового сигналу CLK (початковий стан GND) до портів тактового сигналу clk тригерів ff[4..1]. У другому рівнянні входи скидання (clrn) і установки (prn) з’єднуються із входами Reset і Set, початковий стан яких GND. У третьому рівнянні вхід дозволу ena з'єднується із входом Enable, початковий стан якого VCC. У четвертім рівнянні входи даних проекту з'єднуються з портами даних тригерів ff[4..0]. У п’ятому рівнянні виходи проекту з'єднуються з виходами тригерів. Всі п’ять рівняння оцінюються одночасно.

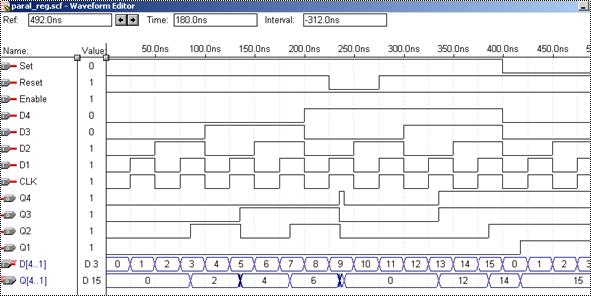

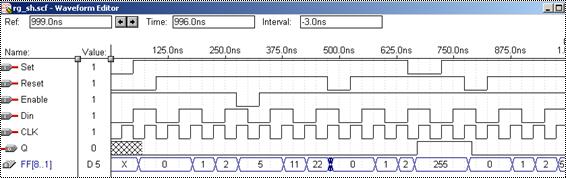

Робота схемного проекту і проекту, описаного мовою AHDL наведено на рис. 4 і 5 відповідно.

Рис. 4

Рис.5

Рис. 6

Звернемо увагу на те, що у випадку коли на входи Set і Reset подані одночасно нулі, то регістри не працюють. На рис.4 це відображено сіточкою і символом “x”, а на рис.6 символом “x”.

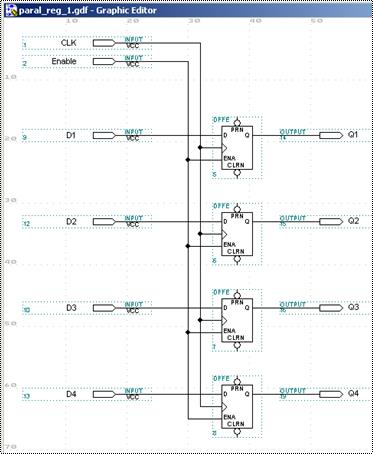

Аналогічним чином можна реалізувати регістри паралельного завантаження за допомогою примітиві DFFE, але без підключення входів PRN і CLRN (рис. 7, 8)

Рис. 7

Рис. 8

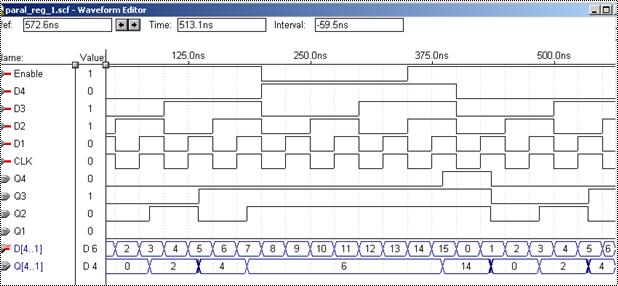

Нижче наведено проект аналогічного регістра паралельного завантаження, описаного мовою опису апаратури AHDL. Результати моделювання роботи такого регістра наведено на рис. 9.

SUBDESIGN RG_4_1

(

D[4..1], CLK: INPUT;

Enable: INPUT=VCC;

Q[4..1]: OUTPUT;

)

VARIABLE

FF[4..1]:DFFE;

BEGIN

FF[].clk =CLK;

FF[].Ena =Enable;

FF[].d =D[];

Q[] =FF[].q;

END;

Рис. 9

Тригери з регістровими виходами

У попередніх прикладах тригерну змінну, наприклад, ff[4..1]: DFFE, яка описана в розділі VARIABLE називають регістровою змінною.

Разом з тим, можна оголосити регістрові виходи, якщо оголосити виходи підпроекту як D-тригери в розділі VARIABLE.

Наведений нижче файл reg_out.tdf забезпечує ті ж функції, що й попередній (RG_4_1.tdf), але має регістрові виходи.

SUBDESIGN reg_out

(

clk, load, D[4..1]: INPUT;

Q[4..1]: OUTPUT;

)

VARIABLE

q[4..1]: DFFE;

BEGIN

q[].clk = clk;

q[].ena = load;

q[] = d[];

END;

Значення з D входів направляється в регістр. Виходи з регістра не виводяться до тих пір, поки не появиться додатній фронт сигналу CLK. Звернення до виходів Q тригерів відбувається без використання порту Q. Результати моделювання роботи такого тригера наведено на рис. 10.

Рис. 10

Параметризований N-розрядний паралельний регістр

Нижче наведено параметризований опис N-розрядний паралельний регістр зі входами асинхронної установки (Set) асинхронного скидання (Reset) і дозволу завантаження даних (Enable). Моделювання роботи такого регістра наведено на рис. 11.

PARAMETERS (N=8);

SUBDESIGN rg _par

(

Din[N..1], Set, Reset: INPUT=GND;

CLK: INPUT;

Enable: INPUT=VCC;

Q[N..1]: OUTPUT;

)

VARIABLE

FF[N..1]: DFFE;

BEGIN

FF[].clk = clk;

FF[].ena = Enable;

FF[].d=Din[];

FF[].prn=Set;

FF[].clrn=Reset;

Q[] =FF[].q;

END;

Рис. 11

Зсувний регістр

Нижче наведено параметризований опис N-розрядного зсувного регістра зі входами асинхронної установки (Set) асинхронного скидання (Reset) і дозволу завантаження даних (Enable). Моделювання роботи такого регістра наведено на рис. 12.

PARAMETERS (N=8);

ASSERT (N>0)

REPORT "Value of WIDTH parameter must be greater then %" N

Severity Error;

SUBDESIGN rg_sh

(

Din, Set, Reset: INPUT=GND;

CLK: INPUT;

Enable: INPUT=VCC;

Q: OUTPUT;

)

VARIABLE

FF[N..1]: DFFE;

BEGIN

FF[].clk = clk;

FF[].ena = Enable;

FF[].prn=Set;

FF[].clrn=Reset;

FF[].d=(FF[N-1..1].q,Din);

Q =FF[N].q;

END;

Рис. 12

Таблиця стані розряд регістра зсуву

| ← | Розряди регістра | ||||||||

| Установка в 0 | |||||||||

| Зсув і уведеня 1 | |||||||||

| Зсув і уведеня 1 | |||||||||

| Заборона зсуву | |||||||||

| Зсув і уведеня 1 | |||||||||

| Зсув і уведеня 1 | |||||||||

| Зсув і уведеня 1 | |||||||||

| Установка в 0 | |||||||||

| Зсув і уведеня 1 | |||||||||

| Зсув і уведеня 1 | |||||||||

| Установка в 1 |

Регістр зсуву даних

Нехай нам потрібно перемножити числа:

,

,

Потрібно знайти добуток  шляхом розбиття чисел

шляхом розбиття чисел  і

і  на два доданки по чотири розряди кожний:

на два доданки по чотири розряди кожний:

,

,  .

.

Тоді можна записати:

.

.

Таким чином, для одержання добутку нам потрібно перемножувач 4х4 розряди, 16-ти розрядний суматор та регістр зсуву для передачі даних:

без зсуву ―  ,

,  ;

;

зсув даних вліво на чотири розряди:  ,

,  , або

, або  ,

,  ;

;

зсув даних вліво на вісім розрядів:  ,

,  .

.

Оскілки при множенні маємо три випадки маємо три випадки зсуву на нуль, чотири і вісім розрядів, то нам потрібно змінну, яка може приймати не менше як три різні значення, наприклад, змінна  та одну змінну, яка може приймати результат множення складових, наприклад, змінна

та одну змінну, яка може приймати результат множення складових, наприклад, змінна  .

.

Такий регістр, мовою опису апаратури AHDL, має вигляд:

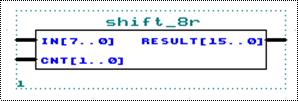

SUBDESIGN shift_8r

(in[7..0]:INPUT;

cnt[1..0]:INPUT;

result[15..0]:OUTPUT;)

BEGIN

CASE cnt[] IS

WHEN 1 => result[15..12]=0;

result[11..4]=in[];

result[3..0]=0;

WHEN 2 => result[15..8]=in[];

result[7..0]=0;

WHEN others => result[15..8]=0;

result[7..0]=in[];

END CASE;

END;

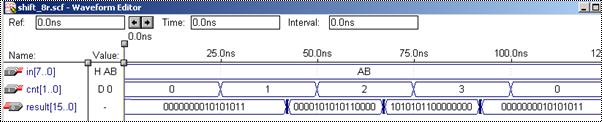

Символ такого регістра та результати моделювання його роботи наведено на рис.13, 14, відповідно.

Рис. 13

Рис. 14

|

|

|

|

|

Дата добавления: 2015-05-09; Просмотров: 835; Нарушение авторских прав?; Мы поможем в написании вашей работы!